ADF4108在宽带X波段频率合成器中的设计应用

ADF4108在宽带X波段频率合成器中的设计应用

本文所讨论的就是基于锁相环路的同步原理,由一个高准确度、高稳定度的参考晶体振荡器,综合出大量离散频率的一种技术。现代雷达系统对频率源的精度、分辨率、带宽、转换时间及频谱纯度等提出了越来越高的要求,性能卓越的频率源均通过锁相环频率合成技术来实现,

由于ADF4108芯片的工作带宽宽(最大带宽8GHz)、集成度高,因此只需要少量的外围电路就可以构成一个宽带、低噪声、低功耗、高稳定度的X波段频率合成器。该器件适用于高频无线系统,如宽带无线接入、卫星通信、仪器仪表、无线局域网和无线射频基站。ADF4108是较高的PLL频率合成,该器件可用来实现无线接收器和发射系统中的上变频和下变频部分的本地振荡频率。

锁相环频率合成器的基本原理

锁相环路(PLL)通常由鉴相器(PDF)、环路滤波器(LF)、压控振荡器(VCO)和可变程序分频器组成。锁相环路是一个相位误差控制系统,它比较输入信号与压控振荡器输出信号之间的相位差,产生一个对应于两个信号相位差的误差电压,该电压经处理后调整压控振荡器的频率(相位)。当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等。锁相环路的这一特点,使它在自动频率控制中得到应用,以实现精确的频率控制。环路在锁定时要得到一定的控制电压,则鉴相器必须有一个非零的输出,即f0=fr,环路作用必须有相位差,相位差维持着两信号的同步,使输出信号频率稳定。锁相环基本原理如图1所示。

可变程序分频器(N)的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位。锁相环路对高稳定度的参考振荡器(通常是晶体振荡器)锁定,环路串接可编程的程序分频器,通过编程改变程序分频器的分频比R、N,从而获得N/R倍参考频率的稳定输出。频率合成器输出频率f0与晶体振荡器参考频率fr的关系为:

![]()

其中,R是固定分频比,N是程序(可变)分频比,fr是晶振输出的参考频率,f0是频率合成器的输出频率。

电路设计、噪声分析及仿真

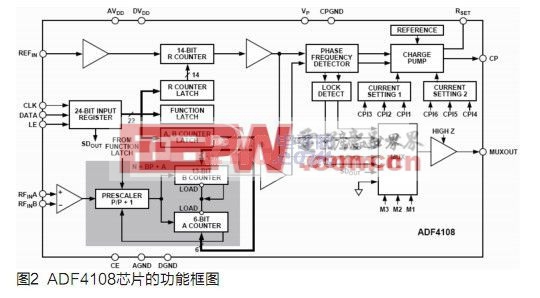

ADF4108主要由一个低噪声数字鉴相器(PDF)、一个精密电荷泵、一个可编程参考分频器、可编程A(6bit)及B(13bit)分频计数器和一个双模分频器(P/P+1)构成。在这里,随模式控制高、低电平的不同,双模分频器采用两个不同的分频模数P+1和P。双模分频器的输出同时驱动两个可编程分频器,他们分别预置在A和B(A

压控振荡器输出的信号经N次分频后送入鉴相器中作为一路鉴相信号,参考晶振输出的标准信号经参考分频器R次分频后送到鉴相器中作为另一路鉴相信号。鉴相器的输出反映两路鉴相信号相位误差特性的电流序列脉冲,经电荷泵的作用输入到低通滤波器中,低通滤波器将电流转换成VCO的控制电压,同时对噪声及鉴相输出的纹波等干扰进行抑制,鉴相器内部还有一个可编程延迟单元,用来控制翻转脉冲的宽度,这个翻转脉冲保证鉴相器的传递函数没有死区,因此,降低了相位噪声和参考杂散。VCO输出与其输入端控制电压相应的工作频率。

ADF4108最大的特点是工作在高频,设计的锁相环路具有宽带宽,从而在X波段频合器中省掉了倍频器,消除了倍频器带来的谐波、杂波及噪声干扰(倍频器对系统的噪声恶化公式为:10logN,其中N为倍频次数,即每增加一倍频率就会带来3dB的噪声),这样有利于简化系统电路、提高系统性能及降低系统成本。ADF4108能通过芯片的数字串口接口对A、B、R及P等寄存器进行预置和改变,从而可方便地获得不同的输出频率。其功能框图如图2所示。

噪声分析

对于PLL整个系统而言,其总相位噪声也是我们关心的一个重要问题,它和很多因素有关。

频率合成器的相位噪声和10logfPDF有关,对于每一个2fPDF频率而言,其相位噪声将减小3dB。然而VCO的输出被分频,它的相位噪声符合20logN的规律(其中N为分频比,N=BP+A),因此,对每一个N=2值来说,将增加6dB相位噪声。例如4fPDF频率,fVCO除以4得到fOUT的输出。一方面,在4fPDF的频率下相位噪声减少6dB;另一方面,因为fVCO除以4而增加了12dB的相位噪声,总的结果将增加6dB的相位噪声。

衡量PLL整个系统的相位噪声,可用下面的表达式得到,PHTOTAL= PHSYNTH+20logN+10logfPDF,其中PHTOTAL为PLL整个系统的相位噪声, PHSYNTH为PLL芯片自身的相位噪声,20logN是一个和分频比N有关的相位噪声的增量,10logfPDF是一个和鉴相器输入频率fPDF有关的相位噪声的增量。ADF4108在1Hz时产生-219dBc/Hz相位噪声,在这里我们可根据给定的fPDF及PLL的输出频率求出PLL整个系统的相位噪声PHTOTAL。例如,PLL输入fVCO频率为2.2GHz,fPDF为20MHz,则分频比:N=2200MHz/20MHz=110

PHTOTAL=-219+20log110+10log20×106

=(-219+41+73)dBc/Hz

= -105dBc/Hz

优化设计及仿真

为了实现X波段的微波频率合成器,设计时可以选用锁相环芯片ADF4108与外部VCO和环路滤波器来进行设计。由于受到芯片频带的限制,通常在芯片基础上需增加一个固定分频器,通常称之为固定前置分频式单环频率合成器,以便降低锁相环芯片RFIN的输入频率。该方案的具体电路结构原理如图3所示。

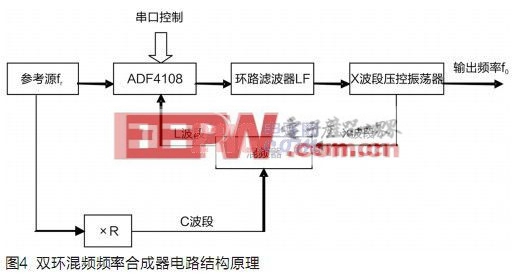

本设计将采用另外方法即外加混频器进行下混频方案,该设计保证了PLL系统中全相参且不引入前置分频器的电源噪声,同时还降低了的RFIN,称之为双环混频式锁相环频率合成器,该方案具体电路结构原理如图4所示(图4中R为倍频次数)。

ADF4108有一个简单的SPI可兼容串联读写接口,CLK、DATA和LE可控制数据传输,当LE(latch enable)为高电平时,在CLK的每个上升沿,已锁入输入内存的24 位数将被送入合适的缓存器。该系统工作速度是纳秒级。这比有几百微秒的锁定时间的典型系统更能满足要求,从而提高了锁相环的锁定速度。本设计采用CPLD进行控制,CPLD芯片中XC95288XL最快工作时间为10ns,并且具有较多的宏单元,可以快速实现对ADF4108芯片的串口控制。混频器选用成都亚光的HSPK68C,压控振荡器选用十三所的HE832K1,输入采用进口的100MHz晶振,其相位噪声可达-155dBc/Hz/kHz,100MHz的晶振经过二功分后,一路信号给梳谱发生器倍频使其产生C波段信号,另外一路送ADF4108作为参考源频率。该方案的具体电原理图见图5。

使用ADI公司提供的专门针对4000系列的锁相环芯片的仿真软件ADI SimPLL,可对ADF4108器件进行仿真。该软件本身提供有多种类型的环路滤波器,用户可根据需要选择滤波器,本设计为了不引入有源器件的电源噪声,选用三阶无源低通滤波器,输入所选定的VCO特性参数,这样,软件可自动计算出环路的各个参数以及相位噪声、锁定时间等。图6 是最终的仿真波形,由图6 可见该方案设计的X波段频率合成器在10GHz的输出频率上相位噪声只有-105dBc/Hz/kHz,且入锁时间只有2.5ms。

结语

由ADF4108芯片构成的X波段频率合成器具有电路简单、功耗低、工作带宽大、相位噪声低及控制灵活等优点,搭配不同的外围电路就可形成不同频段的频率合成器,在无线通信、电子侦查和雷达等系统中具有明显的优势。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理

评论