常用的跳频频率合成器方案比较

1.1 直接频率综合

直接频率综合技术的典型工作原理是将高稳定度的晶体振荡器输出的频标信号通过谐波发生器产生梳状频谱信号,并用滤波器取出所需要的频率成分,再将它们进行组合混频滤波,经电子开关切换得到最终的跳频信号。其优点是频率转换时间短;相位噪声低;输出信号频率较高。缺点是频谱杂散较难抑制,随着跳频点数增加,硬件的复杂度呈指数关系增长,相应的体积和重量也较大。

1.2 锁相环频率综合

与直接频率综合技术不同,采用锁相环频率综合技术的频率合成器可以输出较多的频率点数,频谱杂散分量较少,相位噪声也较低,硬件比较简单。它的工作原理是将压控振荡器产生的射频信号和晶体振荡器输出的参考信号分别进行分频,得到两个频率近似相同的信号,并送到鉴相器比较出误差信号,误差信号经过滤波后,控制压控振荡器,使压控振荡器输出的射频信号保持稳定。它也易于得到较高频率的信号,但是,采用锁相环频率合成技术的频率合成器应用于高速跳频系统最大的弱点是其频率转换时间长,从数十微秒到几百毫秒之间,这对于某些超高速跳频系统而言,已经不能满足频率驻留时间的要求。

1.3 直接数字频率综合

直接数字频率综合技术,是一项基于大规模数字集成电路的技术。它是在外部控制命令下,直接由查表得出当前所需要的频率和相位码,经数模转换输出相应的模拟信号。它主要的特点是频率转换快,频率点数多,而且频率分辨率很高。但是,由于数字集成电路速度和奈奎斯特原理的限制,其输出信号频率不高,输出信号频谱杂散也较大,在较宽的工作范围时,不能达到实用要求。

三种频率合成技术的技术特性如表1所示。从表中可以看出,采用单一的频率合成技术,目前都难以达到所需超高速频率合成器的要求。因此必须采用它们的组合形式,取长补短。组合方法常用的主要有DDS+PLL频率合成和DDS+DS频率合成方法,下面分别介绍。

表1 三种频率合成技术的技术特性

1.4 基于DDS的组合式跳频频率合成器

1.4.1 DDS+PLL频率合成方法

1) DDS激励PLL的间接频率合成方法[1, 2]

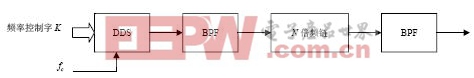

将PLL设计成N倍频环,DDS输出通过带通滤波器BPF直接作为PLL的参考信号。

DDS和PLL结合后,通过合理地选择频率控制字K、系统时钟fc以及可变分频比N,可以将DDS输出频率倍频到合成器工作频段。加入带通滤波器可以有效地抑制DDS的宽带频率杂散。系统原理如图1所示。

图1 DDS激励PLL系统方案原理框图

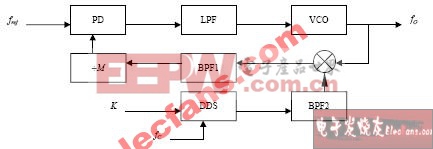

2) PLL内插DDS系统方法[1]

DDS激励PLL的间接频率合成方法,DDS输出的带内杂散经过倍频后,存在着频谱纯度恶化的缺点。为充分发挥PLL频谱纯度高的优势,避免DDS杂散多的弱点,利用高精度的晶体振荡器作为PLL参考频率源。

系统原理如图2所示,图中PLL作为系统核心,输出合成的频率,DDS插入到锁相环内,与VCO输出混频后反馈至PD。

图2 PLL内插DDS系统原理框图

虽然该方案避免了DDS输出的带内杂散倍频后频谱纯度恶化的问题,频谱纯度优于DDS激励PLL方案。但是,在反馈支路内引入混频器和带通滤波器,增加了电路复杂度和调试难度。

由于DDS+PLL频率合成方法都是基于锁相环系统,它是一个惰性环节,锁定时间较长,频率合成器的频率转换时间一般要长达几十微秒以上,因此DDS+PLL的实现方法的系统输出频率捷变速率不高,不适合高速跳频频率合成器的技术要求

1.4.2 DDS+DS频率合成方法

DDS与DS相结合,利用模拟倍频器替代PLL,克服了DDS+PLL频率合成器的频率转换时间长的弱点。在该方案里,用DDS作为频率合成器核心部件,产生足够多离散频点,然后利用多个倍频器和滤波器组成的倍频链提高DDS输出频率,同时拓展了DDS输出带宽。系统方案原理如图3所示。图中插入带通滤波器抑制带外的杂散,提高了频谱纯度。

图3 DDS+DS系统方案原理框图

尽管本方案带通滤波器只能滤掉带外杂散,带内杂散经过倍频后造成频率纯度有所恶化,但是DDS+DS方法在频率转换速率比DDS+PLL方法更具有优势,有利于高速跳频合成器的实现。然而,在保证频率高速切换前提下,如何提高频率合成器的频谱纯度是本方案实现的难点。

模拟信号相关文章:什么是模拟信号

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

评论