实时视频处理系统中乒乓缓存控制器的设计

引言

缓存技术是分布式计算环境中的重要技术,它可以改善系统的整体性能(如吞吐量、查询响应时间等),构建大规模视频服务系统时,可以减少对磁盘的访问,提高系统性能。在高速数据采集系统中,通常在存储设备的前端加一级缓存,可以使低速存储设备无丢失地记录高速数据[1]。不仅如此,现在,在比较高速cpu的性能参数时,一个重要的指标就是看其是否具有高速缓存。

随着数字多媒体技术的不断发展,实时视频数据处理的一个突出的问题就是数据量庞大,特别是在图像帧率及分辨率要求比较高的场合,仅用专用的视频压缩芯片(video asic)、专用的视频信号处理器(video dsp)或通用的高性能数字信号处理芯片(dsp),均无法获得令人满意的效果,为此,人们提出了多种解决方案,其中比较有代表性的方案有以下两种:一是在中央控制器的调度下,两片或多片视频处理芯片并行对实时视频进行处理。二是整个实时视频处理系统由视频采集系统和视频压缩系统组成,其中视频采集系统负责接收原始的视频数据并对其进行一定的预处理;视频压缩系统负责接收视频采集系统预处理后的数据并进行压缩[2]。本文将采用第二种方法,并在此方法中应用fpga设计乒乓缓存控制器,从而实现实时视频数据流的无缝缓冲和处理。

常用数据缓存结构的比较

实时视频处理系统中,输入缓冲和输出缓冲电路的作用主要是为恒速的视频编解码与变速的dsp图像处理过程之间提供适应通道,输入和输出缓冲电路一般有三种结构形式:

(1)双口ram结构

双口ram是在一个sram存储器上具有两套完全独立的数据线、地址线、读写控制线、并允许两个独立的系统同时对该存储器进行随机访问。

(2)fifo结构

fifo可以进行双端操作,但是数据必须先进先出,不能进行随机性的访问,从容量大小来看,双口ram比fifo要大一些,但总的来说,这两种缓冲结构的存储容量还是相对较小,对高速图像处理系统而言,还不是特别适合。

(3)乒乓缓存结构

这种结构是将输入数据流通过输入数据选择单元等时地将数据流分配到两个数据缓冲区。在第1个缓冲周期,将输入的数据流缓存到数据缓冲模块1上,在第2个缓冲周期,通过输入数据选择单元的切换,将输入的数据流缓存到数据缓冲模块2,同时,将数据缓冲模块1缓存的第1个周期的数据通过输出数据选择单元的选择,送到运算处理单元进行处理,第3个缓冲周期,再次切换数据的输入与输出缓冲模块。如此循环,周而复始。

综上所述,乒乓缓存结构实际上相当于一个双口ram,但它与普通的双口ram又有所不同,主要表现在以下几方面:

◆普通双口ram是单个存储体构成的ic,乒乓缓存结构则由包含两个相互独立存储体的多片ic构成,从而使其在结构、速度、容量等方面具有更大的灵活性;

◆若双口在访问同一地址时,普通双口sam指向的必定是存储体内的同一存储单元,而乒乓缓存结构则分别指向属于sram1和sram2的两个不同的存储单元;

◆乒乓缓存结构的双口指向的存储区(sram1还是sram2)可以由外部信号来控制,而普通双口ram则必须由地址线来控制。

乒乓缓存结构的上述特点决定了可以相对较便宜的高速大容量sram、外围逻辑器件构成比双口ram以及高速fifo更适合视频处理的系统所需要的缓冲存储器。

实时视频处理系统结构

数字视频处理系统的突出特点是视频数据的流量非常大,且对系统处理的实时性要求也比较高,因此,系统必须建立快速、有序的视频数据输入、输出机制、尽可能采用高速的fpga,在此基础上,采用适应于高速dsp和fpga处理系统的乒乓缓存结构。

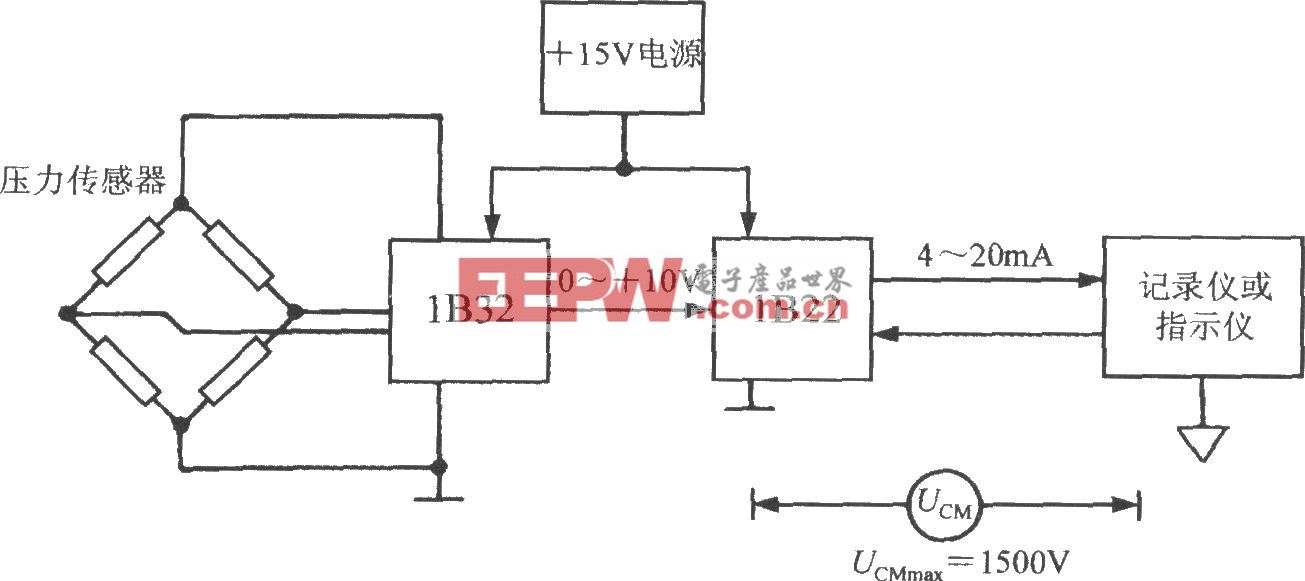

虽然视频信号处理的需求多种多样,但数据处理的流程都遵循数据采集、格式转换、数据接收、数据计算、数据通信的步骤,图1所示是基于fpga和dsp的实时视频信号处理框架。

视频信号转换模块由视频信号处理器完成视频信号从模拟信号到数字信号的转换、图像信号与其他信号的分离、视频信号的格式转换等,最终提供供给后端可以处理的数字视频数据;视频数据计算模块首先接受来自前一个模块的数字视频数据,然后完成对数字视频数据的计算,数据接收由fpga完成,数据计算由dsp完成,通信模块则实现与外界的数据交换。

本文重点介绍的是视频数据计算模块中的输入乒乓缓存结构(如果经dsp编码的信号需要输出并解码的话,同样可以设计输出乒乓缓存结构,原理一样。)

乒乓缓存控制器分析

由上文可知,实现乒乓缓存结构的关键是sram的选择以及控制器的设计,下面对这两个问题进行探讨:

一般情况下,sram1和sram2需选用两个速度、容量以及其他特性完全相同的静态存储器,这是由乒乓缓存结构实际工作时,电路状态转换的对称性决定的,sram器件的速度应高于外部电路所要求的数据输入、输出速度,其容量应不小于需要缓存的数据量,对于一个图像处理系统而言,假如需要缓存的数据量是一帧256×256的图像,那么所需单片sram的容量应大于或等于64k字节。

实现乒乓缓存结构的外部逻辑一般较复杂,故常用高速fpga来实现其控制,这种方式的优点是:

(1)将所有的控制逻辑集成在一块芯片上,减小了控制器的体积;

(2)根据外部信号处理电路的特点,可以灵活设计双口p1、p2以及控制信号vs的输入形式这种普通双口ram所不具备的一个重要特点;

(3)sram存储器接口sr1、sr2的信号位置也可以根据电路板的实际需要来设计。

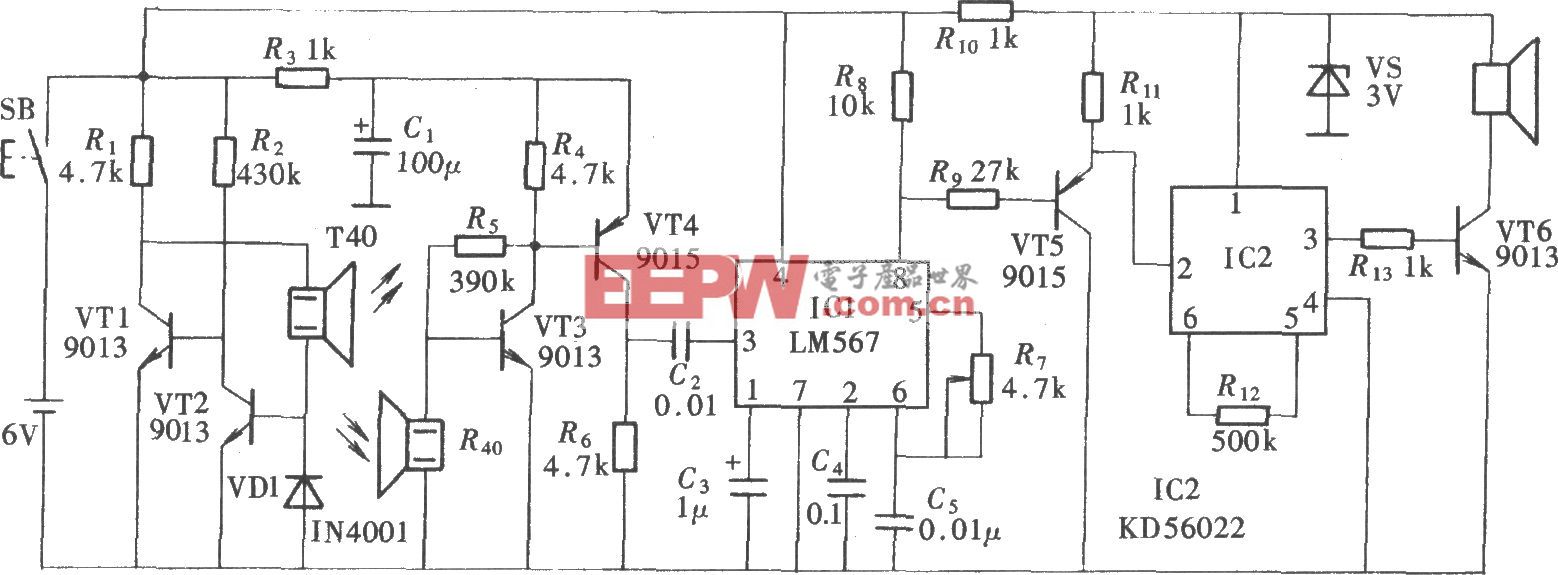

实际上,若系统电路所决定的乒乓缓存结构双口p1和p2是包含地址、数据、以及控制线在内的普通并行口,那么控制器实际上就是一组“单刀双掷开关”。具体方式如图2所示。

乒乓缓存控制器接口

在图2中,输入缓冲电路的上游接视频解码器saa7113,下游接dsp(需要解码时,输出缓冲电路上游接dsp,下游接视频编码器)。对于大多数a/d转换器,由于其仅具有并行数据输入输出端口,而没有地址和控制信号输出口,故它无法直接对普通sram进行读/写操作,因而要求乒乓缓存控制器本身具有地址产生功能,故必须增加地址产生逻辑,其中,clk为ad(或da)转换时钟,它作为计数器的脉冲源,而计数器的输出端则提供了sram寻址线。该图中,db1接ad转换器saa7113的数据输出端(或da转换器的数据输入端),cb1为读写使能信号,而对ad转换器而言,因其是恒定输出器件,故p1口cb1的/re应恒接高,/we恒接低(对da转换器而言,因其是恒定输入器件,故p1口cb1的/re应恒接低,/we恒接高),p2口接dsp外存接口(emif)之ce0空间,db2接dsp的数据总线ed,ab2接dsp的地址总线ad。工作时,数据从视频解码器输出到乒乓缓冲器,经缓冲之后输入到dsp的emif外存空间,以备处理。其中,ad转换时钟saa7113 clk作为计数器的计数脉冲,以产生地址线ab1;场同步信号vs用于复位计数器,这意味着乒乓缓存的容量(亦即sr1、sr2的容量)为一场的视频数据。

这样,从saa7113过来的数字信号就可以在乒乓缓存控制器的控制下,像单刀双掷开关一样交替接通,从而将数据写入sdram以便dsp进行处理,这样就很好地解决了对高速数据的缓冲。

仿真流程与结果

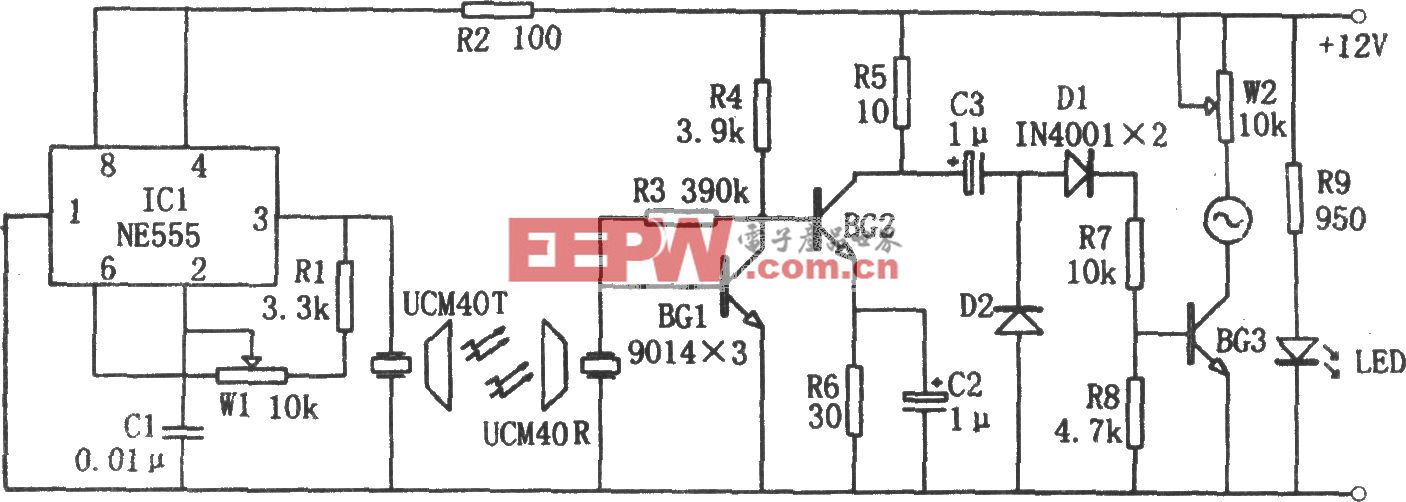

乒乓缓存控制器程序可采用verilog hdl编写,并可在modelsim下实现逻辑仿真,仿真程序包括3部分:一是处于top的主体程序,用于控制其他各个部分程序的运行;二是视频图像采集程序,用于从saa7113获得数据图像数据并保存到sram中,三是乒乓缓存控制器,用于实现对sram数据读写的切换,限于篇幅,这是只列出整体控制过程流程图,见图3。

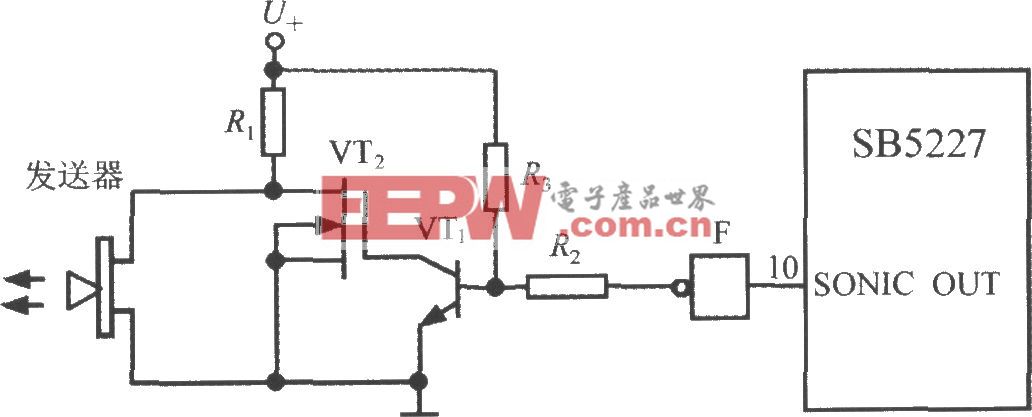

图4是其仿真波形。在控制信号toggle=1时,dsp的emif连接到sr1,以从sram1中读取视频数据,同时saa7113将数据写到sram2,在控制信号toggle=0时,dsp的emif连接到sr2,以从sram2中读取视频数据,同时saa7113写数据到sram1,此过程如此循环,便可实现大量高速视频数据流的无缝缓冲和处理。

结论

本文讨论了乒乓缓存控制器的实现方法,实践证明,乒乓操作的最大特点是可通过输入数据选择单元和输出数据选择单元按节拍相互配合切换,从而将经过缓冲的数据流停顿地送到运算处理单元,以进行运算和处理,如果把乒乓操作模块当做一个整体,站在这个模块的两端看数据,那么,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理,以高效完成大量事实时频数据的无缝缓冲和处理。

评论