模数转换器时钟优化:测试工程观点

系统时钟优化可以提升系统的性能,但也颇具挑战性。为模数转换器设计抖动为350飞秒(fs)的编码电路是相对容易的,但这是否能够满足当今的高速需求?例如,测试AD9446-1001(16 bit 100 MHz ADC)时,在Nyquist区使用100 MHz的采样时钟频率,350 fs的抖动将使信噪比(SNR)下降约3 dB。如果在第三Nyquist域中使用105 MHz的模拟输入信号测试相同的设备,SNR下降可达10 dB。为了将时钟抖动减少到100 fs或更少,设计者需要理解时钟抖动来自哪里,以及ADC能够允许多大的抖动。如果在电路设计完成后才发现时钟电路性能受抖动的限制,并且在设计阶段中本可以很容易地避免该问题发生,这时已经太晚了。

在这里我们将讨论相关的时钟参数和方法以实现高速转换器预期的性能,为此要用到一些技术诀窍和经验。首先从典型的ADC时钟方案开始,如图1中所示,我们将焦点放在信号链路中每一级的可用于优化时钟的技术,并且指明一些应避免使用的常用技术。

图1. 典型的时钟信号链路

什么是抖动?

抖动是系统时钟电路设计中最重要的参数,因此了解某些基础知识并且理解术语的含义是十分重要的。许多技术文献描述了关于抖动的十分精确的数学模型,但是设计性能优良的转换器并非全部取决于精确的抖动描述。设计人员必须理解抖动如何进入系统以及如何使抖动的影响最小。

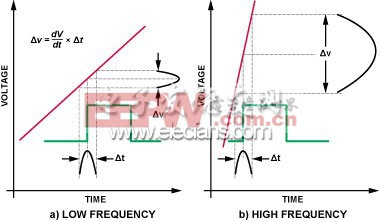

抖动是时钟边沿的位置变化,这将产生定时误差,直接导致转换幅度精度的误差(图2a)。模拟输入频率的增加导致输入信号的斜率增加,这将使转换误差放大(图2b)。应当注意,转换误差的度量是相对的,10 bit器件0.5 LSB(最低有效位)的转换误差等效于16 bit器件32 LSB的误差。这意味着随着ADC分辨率和模拟输入频率的增加,抖动变得更加引人注意。

图2. 转换误差是时钟抖动和模拟输入频率的函数

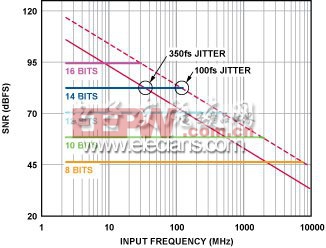

直观上看,它们之间的关系是非常明显的,因此工程师可以通过分析ADC性能和编码时钟抖动之间的关系,最终确定可接受的抖动量。式1定义了理想ADC(具有无穷大分辨率)SNR(dB)与频率的关系,而式2定义了N(10、12、14或16)bit理想ADC的SNR(dB)。

(1) 参看图3的斜线

(1) 参看图3的斜线

(2) 参看图3的水平线

(2) 参看图3的水平线

图3是由这两个公式画出的曲线图。用户可以在曲线交点处确定给定模拟输入信号频率时可容忍的总时钟抖动量。在低频下,精度受到转换器分辨率的限制。然而,随着输入信号频率的增加,在大于某个频点之后,ADC的性能将受控于系统的总时钟抖动。位于该频点左侧的输入信号频率,无须考虑小抖动的问题。

图3. 理想ADC的SNR vs. 模拟输入信号频率和抖动

然而,如果信号频率在该频点附近或者在其右侧,则必须降低频率或分辨率,或者必须提高抖动指标。因此,抖动越大,SNR性能受控于时钟系统抖动的频点就越低。

例如,如果使用具有350 fs抖动的时钟测试14 bit ADC,为了避免性能下降,输入信号频率必须低于35 MHz(14 bit水平线与350 fs斜线的交点)。如果抖动为100 fs,则输入信号频率可以达到125 MHz。

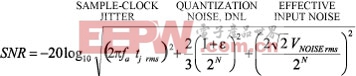

实际上,当模拟测试频率接近交点时,使用该一阶近似的简化模型便丧失了有效性。为了全面地理解时钟抖动对ADC性能的影响,除了分辨率以外,还要考虑量化噪声和模拟输入幅度(式3,基于参考文献9)。

(3)

(3)

其中

SNR=信噪比(dB)

fa=满刻度正弦波的模拟输入频率

tj rms=内部ADC抖动和外部时钟抖动的组合rms抖动

ε=ADC的平均差分非线性(DNL)(LSB)

N=ADC的分辨率(bit)

VNOISE rms=ADC的有效输入噪声

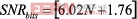

如果tj rms=0,ε=0并且VNOISE rms=0,则上面的公式变为我们所熟悉的

SNR=6.02N+1.76dB

评论