32位元MCU功耗再降

物联网与智慧生活风潮兴起,带动市场对高效能且低功耗的32位元微控制器(MCU)需求增温,因此微控制器业者已积极从制程和中央处理器(CPU)核心选择,以及电路设计等层面着手,以降低动态与静态功耗,并兼顾整体运算效能。

传统的低功耗微控制器(MCU)设计都是以8位元MCU为主,因为8位元内核阈门相对较少,运行或泄露的电流低,售价也相对低廉。然而,许多新兴的应用皆需要比8位元内核更大的处理效率。

近年智慧生活的抬头、物联网的兴起,手持式消费性电子产品与无线功能需求愈来愈高、设计愈来愈复杂,要提高性能的同时又要兼顾低功耗,需要有一高性能、低功耗的主控MCU做为平台。此外,工业上的智慧化也在展开,如远端监控、数位化、网路化等。简言之,云端应用和物联网需求越来越多,已导致产品功能愈来愈复杂,运算需求愈来愈高。

2009年安谋国际(ARM)发表32位元Cortex-M0内核,提供MCU厂商一个强而有力的平台,加上制程微缩技术的进步,嵌入式快闪记忆体制程普及化及降价,主要成本来自记忆体大小及类比周边和输入输出(I/O)接脚数量,中央处理器(CPU)内核的成本差异已大幅缩短,更促进高性价比32位元低功耗MCU的快速发展。

运行与静态耗电量组成MCU功耗

在开始讨论低功耗MCU设计前,必须先探讨MCU功耗的来源,其主要由静态功耗及运行功耗两部分组成。实际的应用,须藉由计算平均功耗,决定最后系统功耗性能指标。

动态功耗与工作电压和频率相关

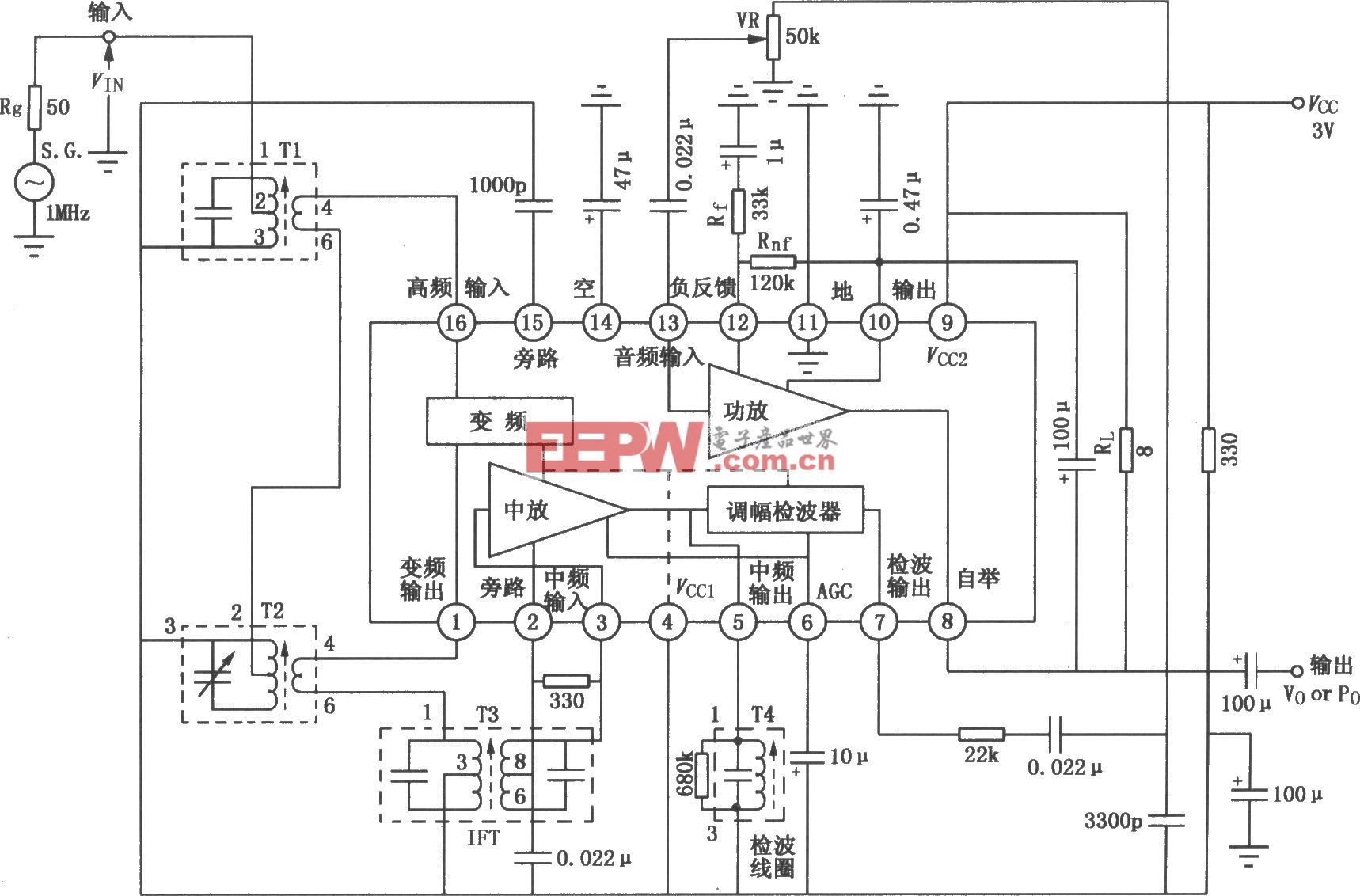

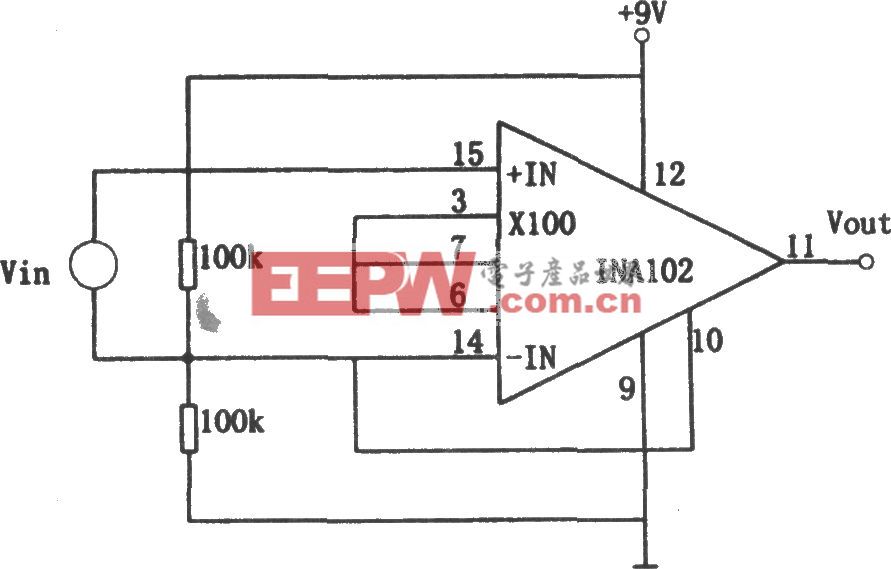

现代MCU已整合相当多的类比周边,不能单纯考量数位电路的动态功耗。MCU运行时的总功耗,由类比周边功耗和数位周边的动态功耗相加而得。类比电路的功耗通常由工作电压及其性能要求指标来决定,如100奈秒传递延迟(Propagation Delay)的比较器工作电流可能约为40微安培;当允许传递延迟规格为1微秒时,工作电流有机会降到个位数微安培。

数位电路的动态功耗主要来自开关频率、电压及等效负载电容,其计算公式如下:

PDynamic(动态功耗)~f(工作频率)xCL(等效负载电容)xVDD2(工作电压)

由以上公式可以理解到降低动态功耗最直接的方式,为降低工作电压及工作频率,但MCU实际应用面通常要求更宽广的工作电压及更高的效能。在降低工作电压方面,可以选择更先进的制程,并透过线性稳压器(LDO)让CPU内核、数位电路及与接脚输出入电压无关的类比周边在低压操作;I/O接脚及须与其他外部电路连接的类比周边,则在较高的系统电压操作,如此可以兼顾低功耗及宽工作电压的需求。

在降低工作频率这项参数上,一个设计优良的32位元MCU更能突显其效能优势,除了直觉的每秒可执行多少百万指令(MIPS)比较之外,32位元汇流排也代表更高的资料存取频宽,能以更低的工作频率达到相同的效能,进而降低整体功耗。另外,若MCU内建与操作频率相关的类比周边,例如石英晶体振荡电路、嵌入式快闪记忆体或电流式数位类比转换器(DAC),其电流消耗与转换频率成正比,也要纳入低功耗MCU的动态功耗设计考量。

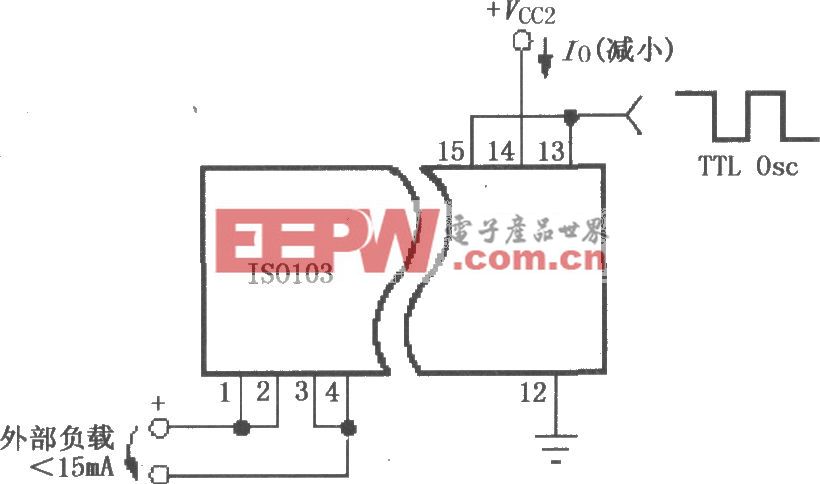

静态功耗缩减挑战重重

传统静态功耗的定义是指系统时脉源关闭时,数位电路的漏电流,但是在混合讯号低功耗MCU的设计中,要同时考虑下列多种漏电流来源,包含数位电路漏电流、静态随机存取记忆体(SRAM)漏电流、待机时已关闭的模拟电路漏电流(例如ADC、嵌入式快闪记忆体)、待机时不关闭的模拟电路工作电流(如LDO、电压不足侦测(BOD))及I/O接脚的漏电流。

由于时脉源已关闭,影响静态功耗的主要参数为制程、电压及温度。也因此,降低静态功耗必须选择超低功耗制程,但是低功耗制程通常伴随较高的Vt,导致低电压类比周边设计困难。另外,以MCU待机电流1微安培的规格,代表

评论