产品开发中的自适应性能分析

开发工具的目的不仅仅是用于调试复杂问题,而且还要提高开发效率。有时候,比起有效电源特性,这一目标的达成更取决于标准产品特性的便捷与实用。大部分专业调试器中的一大便捷特性是以寄存器组来显示存储器映射SoC外设寄存器,包括其名称、比特域和描述,这与外设文档中的相一致。

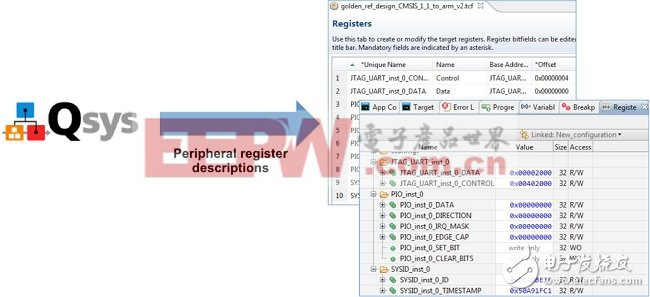

当针对FPGA进行开发时,还要复杂一些。FPGA供应商通常会提供FPGA硬件库,例如,加密/解密模块、数学算法加速模块和外设控制器等。但是,需要硬件开发人员确定将多少模块综合到FPGA中,确定在处理器中,它们位于存储器映射的哪些位置,这意味着,软件调试器不可能立即提供外设寄存器视图。软件开发人员能够手动生成调试器外设描述视图,但是手动编辑非常耗时,而且容易出错。其解决方法要求在FPGA综合工具和软件调试器之间进行通信。Altera QSys系统配置工具为完整的FPGA设计生成外设寄存器描述文件,ARM DS-5调试器能够自动导入文件,显示FPGA IP寄存器,看起来它们就像硬核处理器系统的组成部分。

图1:自动生成外设寄存器视图,并在DS-5调试器上进行导入

系统级性能分析

今天,产品开发人员更关注调试性能问题,努力在相同的硬件上实现更多的功能,或者降低功耗。因此,工具供应商越来越关注性能和功耗分析工具。

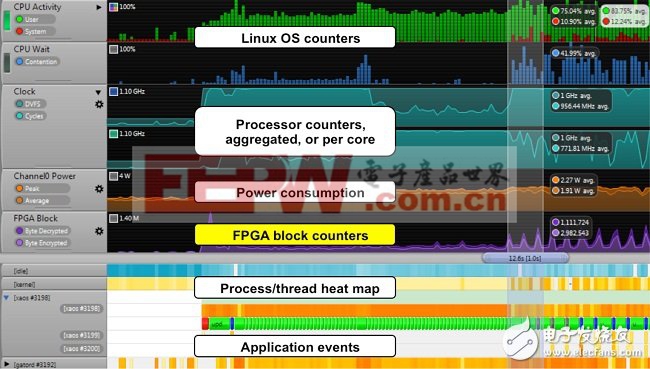

选择SoC器件(集成了处理器和FPGA架构)的一个主要原因是能够使用FPGA硬件模块来加速软件工作。例如,可以使用FFT解码器或者FPGA架构中的 DES解密算法来释放处理器,从而让处理器去完成其他任务,或者,进入睡眠状态以节省功耗。对于这些器件,工具应能够查看处理器和FPGA IP模块资源占用率相对水平。然后,设计人员可以使用这些信息来优化系统。

虽然采用了指令跟踪来优化软件编解码器和其他性能软件,但是,对于运行Linux和Android等操作系统的ARM应用处理器,还是需要使用ARM DS-5流线性能分析器等某些特定的分析工具。ARM DS-5使用在目标中运行的Linux驱动,按照一定的时间间隔对信息进行采样,每次由事件计数器提供捕获的任务切换信息,诸如:

● 处理器负载等操作系统事件。

● 分支误预测等处理器事件。

● 系统事件,这些计数器支持用户找到系统级瓶颈。

● 软件注释,用于报告感兴趣的事件。

看到这一信息在一条时间线上显现后,开发人员就了解了软件和硬件之间的相互作用。

对于混合处理器和FPGA器件,可以使用流线分析器来同时优化硬件和软件。硬件中需要的唯一基本组件是存储器映射寄存器,对每一不同IP模块的利用率进行计算。然后,可以配置流线来访问这些新计数器,显示其随着时间变化的数值,与CPU使用率和其他系统级计数器相关联。

图2:ARM DS-5流线中的时间线视图。

对功耗有要求的用户可以通过ARM

评论