复位设计中的结构性缺陷及解决方案(一)

随着数字化设计和SoC的日益复杂,复位架构也变得非常复杂。在实施如此复杂的架构时,设计人员往往会犯一些低级错误,这些错误可能会导致亚稳态、干扰或其他系统功能故障。本文讨论了一些复位设计的基本的结构性问题。在每个问题的最后,都提出了一些解决方案。

复位域交叉问题

1. 问题

在一个连续设计中,如果源寄存器的异步复位不同于目标寄存器的复位,并且在起点寄存器的复位断言过程中目标寄存器的数据输入发生异步变化,那么该路径将被视为异步路径,尽管源寄存器和目标寄存器都位于同一个时钟域,在源寄存器的复位断言过程中可能导致目标寄存器出现亚稳态。这被称为复位域交叉,其中启动和捕捉触发的复位是不同的。

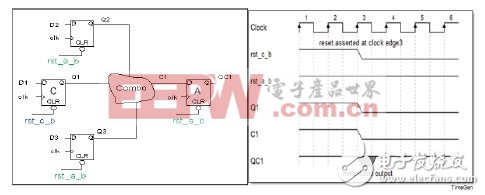

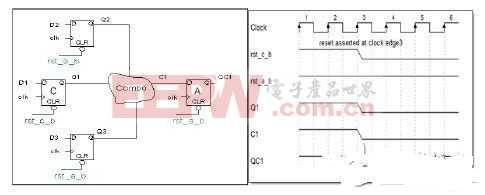

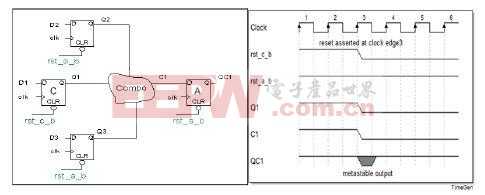

在这种情况下,C寄存器和A寄存器的起点异步复位断言是不同的。在C寄存器复位断言过程中而A触发器没有复位,如果A寄存器的输入端有一些有效数据交易,那么C寄存器的起点异步复位断言引起的异步变更可能导致目标A寄存器发生时序违规,从而可能产生亚稳态。

图1:复位域交叉问题

在上面的时序图中,当有一些有效数据交易通过C1进行时,rst_c_b获得断言,导致C1发生异步改变,w.r.t clk从而使QC1进入亚稳态,这可能导致设计发生功能故障。

2. 解决方案

* 使用异步复位、不可复位触发器或D1触发器POR.

* 如果复位源rst_c_b是同步的,那么则认为来自C_CLR --> Q的用于从rst_c_b_reg -->C_CLR-->C_Q1-->C1-->A_D进行设置保持检查的时序弧能够避免设计亚稳态。然而,通常在默认情况下 C_CLR-->Q时序弧在库中不启用,需要在定时分析过程中明确启用。

* 在目的地(A)使用双触发器同步器,以避免设计中发生亚稳态传播。然而,设计人员应确保安装两个触发器引入的延迟不会影响预期功能。

由于组合环路导致复位源干扰

1. 问题

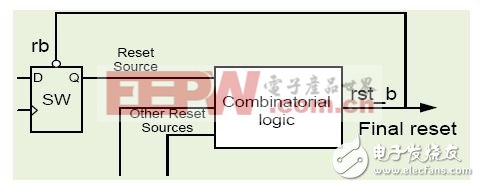

在SoC 中,全局系统复位在设备中组合了软件或硬件生成的各种复位源。LVD复位、看门狗复位、调试复位、软件复位、时钟丢失复位是导致全局系统复位断言的一些示例。 然而,如果由于任何复位源导致的全局复位断言是完全异步的,且复位发生源逻辑被全局复位清零,那么设计中会产生组合环路,这会在该复位源产生干扰。组合路径的传播延迟会根据不同的流程、电压或温度以及干扰范围而不同。如果设计中使用了组合信元用于复位断言和去断言,那么也会导致模拟中出现紊乱情况。这被视为设计人员的非常低级的错误。

图2:复位源干扰(基本问题)

评论