使用时间可控发射方法来进行模拟电路的失效分析

时间可控发射方法(TRE)是一种常用的非入侵式波形测量方法,它能从芯片的背面探测芯片内部节点的时序波形。完美的TRE系统能提供很高的带宽 (》5GHz), 很好的探测尺寸精度 (0.25微米), 而且能显示芯片内部所有节点的波形。TRE波形一般用于探测不正确的信号电平,电路竞争和冒险问题以及几皮秒的高精度时序错误。

通常,在模拟电路诊断中TRE的使用经常受到限制,因为从模拟电路内部提取TRE波形会非常困难。动态的光子发射具有很高的非线性度。但是,我们可以提取芯片内部小幅度差分逻辑电路的波形,而这些信号能导致模拟波形的pass或者fail。在0.18微米工艺中,这些波形在判断芯片pass或fail时非常关键。

工作原理

科利登的EmiScope(R)是一种发射显微设备,它能收集处于饱和状态的CMOS器件所发**的光子。当CMOS管子的电平跳转时,主要载流子 (NMOS管中的电子,PMOS管中的空穴) 将通过晶体管的沟道从源极流向漏极。当这种电平转换发生时,沟道附近的小范围内会产生很强的电场。载流子通过这个区域时,该电场对载流子进行做功,使得载流子拥有很多能量。当这些载流子达到漏极之后,这些能量将会被释放。能量的释放有多种机制,其中的一部分会以所谓的光子发射的方式来完成。

EmiScope(R)能测量并在时域上叠加这些光子的发射,因此通过它就能从芯片背面测量芯片内部的时序。使用该技术调试数字电路时很好理解。其实,TRE系统所测得的光子发射信息也能用于模拟电路的探测。与高精度仿真结果结合在一起,这些探测结果能很好地用于模拟电路的调试。

案例分析:调试一个混合信号电路

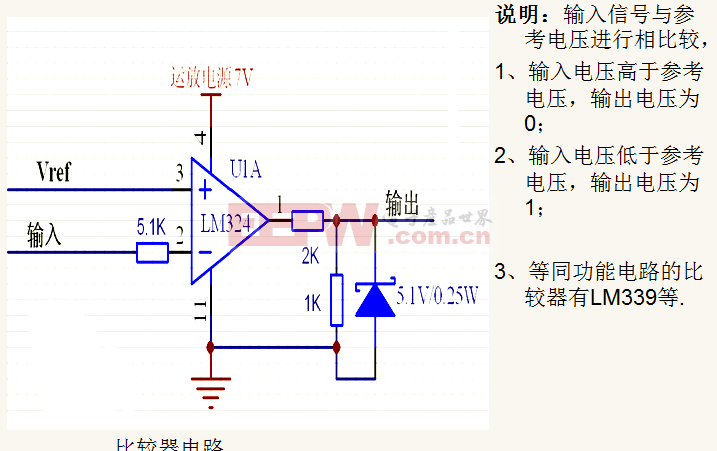

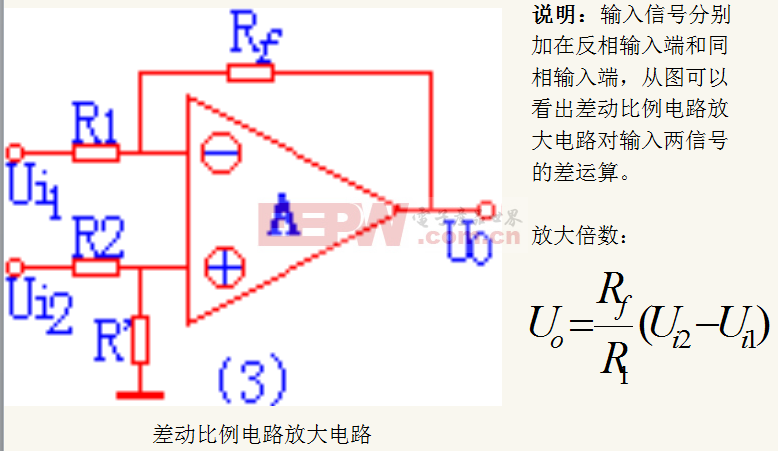

本案例的芯片是一个混合信号芯片,拥有一个数字核和32个相同的模块。每个模块包含一个可编程的“事件发生器“,能用于产生任何低于频率的事件(脉冲)。事件发生器主要是由小幅度差分逻辑电路构成的。由于后续电路的输入时钟需要较大的信号幅度,所以需要使用一个差分信号到单端信号的缓冲器(D2S)来作为二者的接口。图1所示是一个D2S电路的原理图。 输入信号Vin/VinN的幅度分别是0或600mV。两个满幅的输出信号CVO和CVON信号能独立的用于后续电路。

在测试第一批投片芯片时,发现了一个奇怪的问题:下一级电路会出现脉冲丢失现象。而仿真结果则表明芯片工作正常。失效随机地出现在不同的芯片中。在调试之前,我们认为该问题不是由数字部分产生的。同样,事件发生器也似乎不是该问题的原因。

选择一个芯片将其放入TRE系统,收集其发射的光子柱状图。关注其中的两个模块,其中的模块3C经常fail, 模块3B经常pass。在D2S输出端分别观察两个事件发生器模块的”正“输出信号和”负”输出信号。

显示了CVO和CVO#信号的期待信号以及pass和fail条件下,分别利用得到的TRE数据。显示的则是CVON和CVON#信号的相应信息。在光子发射图上,很明显,CVON3B信号上升沿和下降沿的两个尖峰之间的光子强度较高。这表明CVON3B的输入信号(图中的Vgs)从未降低到NMOS管的门限电平之下。

结果

根据仿真结果,CVON在pass和fail的时候其光子发射波形应该是一致的。但我们看到的结果是,当晶体管输出从高到低转换时,发射光子图在信号波形上升沿约1ns之后开始变高,直到信号转换时才变回为0,而不是预期的窄发射脉冲。如果波形脉冲越来越窄,当晶体管输出Vds变低时,发射光子图将会被截断。如果波形脉冲足够宽,发射波形将会逐渐降低到0。

由于发射波形出现时,输出波形应该变高,这表明电压电平有问题。事实上,对于多脉冲脉冲信号来说,高电压降低到足够低的低电压,后续电路却会把它当作前一个较慢脉冲的负下降沿。这一特殊情况将会导致我们前面的测试设备所观察到的失效现象。

结论

为了验证电路功能,我们还做了很多仿真。此外,我们还使用了决定不同芯片参数的发射技术。通过仿真,晶

模拟电路文章专题:模拟电路基础

评论