ISP1362 USB OTG控制芯片及其应用

关键词:ISP1362;OTG;USB主机控制器;MCF5249

1 引言

USB已在PC及笔记本电脑中得到了广泛的应用,它们起到了集线器的作用,用以连接数码相机、打印机等各种外设,但目前大部分设备还不能实现彼此之间的直接通信。

新的USB On-the-Go标准正是针对这一情况而推出的,它将最终结束用电脑作为各种电子设备连接纽带的时代,借助USB On-the-Go,外设既可作为主机,也可作为从机,彼此之间能够互相通信,并可根据实际情况协商确定哪个设备作为主机。

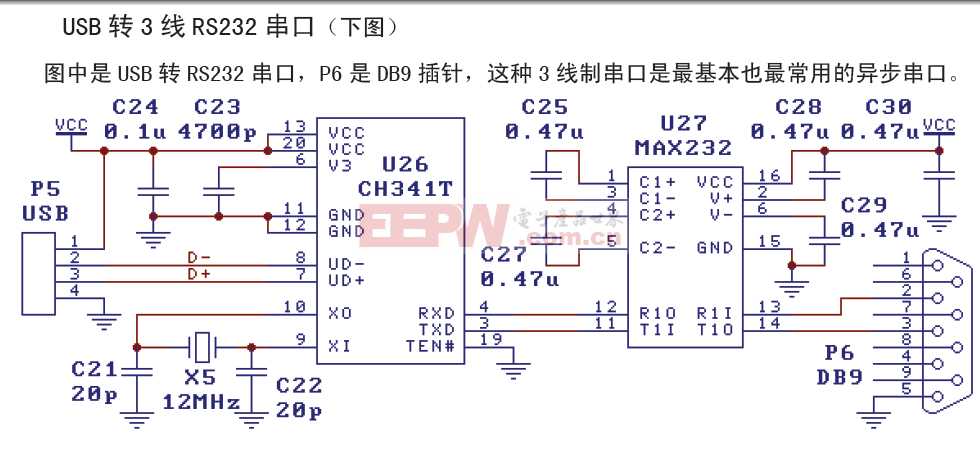

图1

2 ISP1362的结构特点

飞利浦ISP1362由OTG控制器、主机控制器、外设控制器、USB收发器、OTG收发器和缓存器等组成,通过内部集成的总线接口可与CPU相连,ISP1362的内部结构如图1所示。

OTG控制器模块用于提供OTG要求的所有控制、监控及交换功能。它还支持OTG Supplement 1.0标准规定的所有功能。

若以OTG模式进行配置,ISP1362既可用作主机,也可用作外设,并支持主机与外设之间角色转换的主机通信协议HNP(Host Negotiation Protocol)和两种模式下的对话请求协议SRP(Session Request Proto-col)。ISP1362作为主机使用时,能够关闭VBUS以响应SRP,而作为外设使用时,能够启动SRP以唤醒主机。一套OTG寄存器提供的控制及状态监控功能可以用来支持HNP及SRP软件。

ISP1362支持内置电源供电及外部电源供电两种模式。对于较低功耗的应用设计,可用内部集成的电荷泵激励器。而如果应用系统的功耗较高,则要用外部电源供电。

作为外设控制器时,ISP1362支持两个控制端点,还能以全速及低速将多达14个端点编程为任何四种传输类型。

除了通用的USB收发器,ISP1362还集成了计时器及全OTG功能所需要的模拟元件。一个12MHz~48MHz的锁相环?PLL?使得采用低成本的12MHz晶振成为可能,同时由于采用了低频率运作模式,也降低了EMI。

ISP1362还内置了一个用于非OTG配置(仅限于主机及外设)的过流保护电路。当ISP1362用作主机时,一个片内的3.3V到5V电荷激励器可调整支持大量外设所要求的输出电流。此外,ISP1362还提供两个USB端口。端口1可进行软件配置,并可用作下行、上行或OTG端口。作为OTG端口,端口1可在主机或外设模式下工作,并可通过HNP或布线变化来动态转换角色。端口2只用作下行传输。

3 ISP1362的引脚功能

图2是LQFP封装的ISP1362BD的引脚排列,其主要引脚功能如下:

D0~D15:连接到ISP1362内部寄存器和缓冲存储器的16比特数据总线。

RD(引脚20):读信号线。低电平时表示HC/DC驱动器需要读相应的缓冲存储器和寄存器。

CS(引脚21):片选信号,低电平有效。用于控制HC/DC驱动器访问对应的缓冲存储器和寄存器。

WR(引脚22):写信号线。低电平时表示HC/DC驱动器需要写数据到相应的缓冲存储器和寄存器。

TEST0(引脚23):输入输出测试。

DREQ1(引脚24):DMA请求输出。当它有效时,通知DMA控制器HC正在请求数据传送。

DREQ2(引脚25):DMA请求输出。当它有效时,通知DMA控制器DC正在请求数据传送。

DACK1(引脚28):DMA确认输入。表明来自HC的DMA传输请求已经被DMA控制器确认。

DACK2(引脚29):DMA确认输入。表明来自DC的DMA传输请求已经被DMA控制器确认。

INT1和INT2(引脚30,31):连接到外部微处理器的IRQ引脚,使ISP1362执行中断服务程序(ISRS)。

RESET(引脚32):复位输入。

图3

D SUSPEND(引脚34):该引脚电平为高时,设备控制器处于“挂起”状态,电平为低时,唤醒设备控制器。

H-PSW1(引脚35):和外部PMOS开关相连。当引脚电平为低时,打开PMOS开关以为VBUS提供下行端口;引脚电平为高时,关闭PMOS开关。

CLKOUT(引脚38):可编程时钟输出。默认时钟频率为12MHz,变化范围为3MHz~48MHz。

A0(引脚61):用于决定控制器处于命令状态还是数据状态;

A1(引脚62):用于决定控制器工作于主机还是设备控制模式:0 表示处于主机控制(HC)模式;1表示处于设备控制(DC)模式。

4 应用举例

下面以ISP1362开发的USB主机为例详细说明ISP1362的应用。该设计所采用硬件平台是MO-TOROLA MCF5249C3实验开发板,以它作为母板,为USB主机开发提供RS232、BDM接口,并提供8M的SDRAM及2M的flash ROM的编程调试资源。该设计采用的软件平台是Metrowerks CodeWarrior,通过对MCF5249编程实现对ISP1362的控制,从而完成USB主机功能。

4.1 硬件连接原理图

图3所示为ISP1362控制芯片与MCF5249的硬件连接电路原理图。

4.2 USB主机软件流程

整个USB主机软件流程如图4所示,软件部分主要包括USB主机和USB外设功能模块。它们既可相互独立,又可相互调用,共同完成USB主机的功能。

4.3 MCF5249和ISP1362底层通信的实现

这是整个USB体系软件的根基,包括了MCF5249对ISP1362的读、写、设定地址等操作,主要通过MCF5249访问ISP1362的控制寄存器来完成。ISP1362的寄存器结构是命令―数据寄存器对结构,一个完整的寄存器访问周期需要在一个命令阶段后紧跟一个数据阶段。命令阶段用来告知ISP1362将在数据阶段访问它的寄存器。在微处理器的16位数据总线上,命令阶段占低字节,高位填零。下面是读32位寄存器的程序代码:

unsigned long read_reg32(unsigned char reg_no)

{

unsigned int result_l,result_h;

unsigned long result;

outport(hc_com, reg_no); //命令阶段

result_l=inport(hc_data); //数据阶段

result_h=inport(hc_data); //数据阶段

result = result_h;

result = result<<16;

result = result+result_l;

return(result);

}

4.4 主机功能实现

整个程序通过中断调度来完成主机功能。USB总线在工作的时候,系统仍然按照特定的时序和协议规范运行。如系统通过数据线上的电平变化检测到USB设备的接入与移出,接着主机和外设就按照事先约定的顺序执行一系列的信息交换, 即:主机重启外设→主机给外设供电→外设通过缺省的地址0与主机通讯→主机给外设分配地址→主机请求外设的一系列功能和设备描述符。因此, 在C 语言中, 通过顺序的编程和中断的调度,就可以完成主机系统的标准的USB活动。

5 结束语

借助ISP1362,开发商可制造兼容OTG的双功能产品,实现点到点通信,其中的ISP1362不仅可作为主机或传统外设使用,还可根据需要动态转换主机/外设角色。ISP1362的低功耗特性使其成为小型手持设备如个人数字助理(PDA)、数码相机、MP3播放器及移动电话等的理想选择,能满足此类产品对电池使用寿命、产品尺寸的严格要求。

评论