基于EPLD技术的PCI总线接口设计

PCI总线自其问世以来,以其诸多优点,在当今的计算机系统中得到了广泛应用,已经成为计算机设备的标准接口。本文在认真分析PCI总线的接口信号和接口时序的基础上,利用EPLD器件设计实现了PCI总线接口。由于EPLD器件支持在线编程,所以可以根据使用要求将PCI总线接口配置成即插即用和非即插即用两种形式,这种设计方式结构简单、集成度高,具有较高的实用价值。

本文引用地址:https://www.eepw.com.cn/article/202713.htm1 PCI总线概述

局部总线特别是PCI总线的发展,打破了PC数据传送的瓶颈。传统的PC总线结构不能满足图形系统和大型应用程序的要求,所以在此基础上产生和发展了局部总线。它将计算机外设从I/O总线上移下来,使它们更靠近系统处理器,从而提高了处理器和外设之间的传送速度。

从设备的PCI接口至少需要47条信号线,而主控设备的PCI接口至少需要49条信号线,包括数据/地址复用总线、接口控制线、仲裁、总线命令以及系统线等。

PCI总线在进行数据传输时,地址节拍、总线命令在C/BE[0..3]上由主机输出,用于说明当前PCI总线周期需要执行的功能。其命令如表1所示。

2 PCI总线协议和读写时序

PCI总线的传输机制是成组数据猝发传输,每组数据由一个地址脉冲和一个或几个数据脉冲组成。一般基本的PCI传输由三个信号控制:

信号由PCI主控设备驱动,表示总线操作的开始和结束;

信号由PCI主控设备驱动,在读周期表示主控设备准备接收数据,在写周期表示AD[31..0]上数据有效;

信号由PCI从设备驱动,在读周期,表示从设备准备好传输数据,在写周期表示从设备准备好接收数据。

当数据有效时,数据源设备需要无条件地设置XRDY有效,一旦主控设备使有效,中途不能改变状态,直到信号无效或数据传送结束。

PCI是地址/数据复用总线,其读操作的时序如图1所示。当进行PCI读传输时,首先置低,有效,读传输开始,同时AD[31..0]保持有效地址信号,C/BE[3..0]保持总线命令。如果总线命令为存储器读(0110),AD[31..0]地址在从设备地址范围内,从设备置有效,主控设备驱动,表明主控设备准备好接收数据。为避免总线冲突,接下来的一个周期AD[31..0]既不被主控设备驱动,也不被从设备驱动(该周期成为总线转换周期),此后AD[31..0]上出现数据,C/BE[3..0]变为字节允许信号,主控设备开始检测信号。如果信号无效(为高电平),则主控设备自动插入等待周期,如果信号有效,则总线开始传输数据。在最后一个数据脉冲之后,主控设备将和 置为无效,表示传输结束。

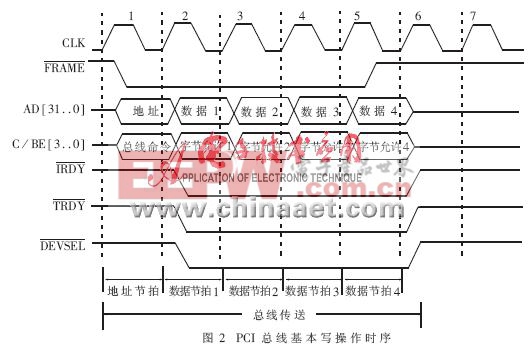

写传输时,由于地址均由主控设备提供,因此不存在总线转换周期。其传输过程与读周期基本类似,只是C/BE[3..0]上的总线命令为存储器写(0111),具体的传输时序如图2所示。

3 PCI总线的接口设计方案

根据以上分析,选用ALTER的高速EPLD器件EPM7128S84来完成PCI总线接口的设计。为简化起见,选用存储器作为从设备,其总体结构如图3所示。

下面将给出用AHDL语言编写的EPLD控制程序以及仿真结果。为简单起见,设定从设备为非即插即用类型的PCI插卡,直接将其地址空间配置为0X50000000~0X5FFFFFFF(或在计算机内不与其他设备冲突的地址),时钟周期选用33MHz,具体的程序如下:

SUBDESIGN pci_if

(

clkin : input;

frame : input;

ad[31..0] : input;

cbe[3..0] : input;

irdy : input;

trdy : output;

devsel : output;

wr : output;

cs : output;

a[10..0] : output;

)

variable

count[1..0] : DFF;

da[31..0] : DFF;

wr1 : node;

rd1 : node;

sign1 : node;

sign2 : node;

sign4 : node;

sign3 : node;

cs1 : node;

begin

count[1..0].clk=clkin;

count[1..0].clrn=!frame;

sign1=(count[]==3);

if sign1 then count[].d=count[].q;

else

count[].d=count[].q+1;

end if;

sign2=(count[]1)!frame;

sign3=(count[]>=2)(count[]=3);

sign4=(count[]>=1)(count[]=3);

da[31..0].clk=sign2!frame;

da[31..0].d=ad[31..0];

cs1=!da31da30!da29da28;

if cs1 then

devsel=!sign4;

a[10..0]=ad[10..0];

wr1=!cbe3cbe2cbe1cbe0;

rd1=!cbe3cbe2cbe1!cbe0;

if rd1!irdy then

trdy=!sign3;

!cs=cs1!frame;

wr=rd1!frame;

end if;

if wr1!irdy then

trdy=!sign4;

!cs=cs1!frame;

!wr=wr1frame;

end if;

end if;

end ;

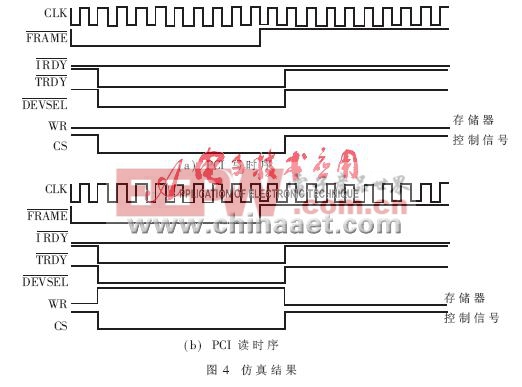

仿真结果如图4所示。

评论