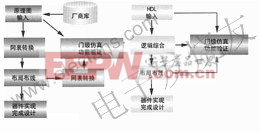

- FPGA/EPLD的自上而下设计方法,FPGA/EPLD的自上而下(Top-Down)设计方法: 传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特

- 关键字:

FPGA EPLD 自上而下 设计方法

- FPGA/EPLD的自上而下(Top-Down)设计方法:传统的设计手段是采用原理图输入的方式进行的,通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图

- 关键字:

FPGA EPLD 自上而下

- FPGA/EPLD的自上而下设计方法及其优缺点介绍,FPGA/EPLD的自上而下(Top-Down)设计方法: 传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特

- 关键字:

缺点 介绍 及其 方法 自上而下 设计 FPGA/EPLD

- 在同步串行数据传输过程中,时钟线上只要有一点小毛刺就会导致数据传输失误,从而影响系统的正常工作。传统...

- 关键字:

滤波器 EPLD 干扰信号

- FPGA/EPLD的自上而下设计方法,FPGA/EPLD的自上而下(Top-Down)设计方法: 传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特

- 关键字:

方法 设计 自上而下 FPGA/EPLD

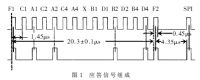

- 1问题的提出

在同步串行数据传输过程中,时钟线上只要有一点小毛刺就会导致数据传输失误,从而影响系统的正常工作。传统的处理方法是在接收端并入一小电容来滤除毛刺,这种方法只能去除某一固定频率下的干扰,

- 关键字:

EPLD 抗干扰滤波器

- 随着VLSI/ULSI技术的发展,可编程逻辑器件EPLD/FPGA越来越受到人们的青睐,由于它具有集成度高、速度快、开发周期短、费用低、用户可定义功能及可重复编程和擦写等许多优点,其应用领域不断扩大。这些器件的灵活性和

- 关键字:

EPLD PCI 总线 仲裁器

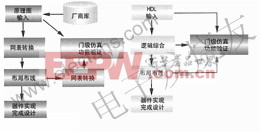

- PCI总线自其问世以来,以其诸多优点,在当今的计算机系统中得到了广泛应用,已经成为计算机设备的标准接口。本文在认真分析PCI总线的接口信号和接口时序的基础上,利用EPLD器件设计实现了PCI总线接口。由于EPLD器件支

- 关键字:

EPLD PCI 总线 接口设计

- 主要介绍作为从设备如何根据PCI总线协议设计PCI总线接口电路,从而实现基于PCI总线的GP-IB接口电路设计,重点阐述PCI总线接口状态机的设计。

- 关键字:

PCI 状态机 GP-IB EPLD 200806

- 摘 要:用EPLD实现的单脉冲二次雷达应答处理器。其主要功能包括:应答框架脉冲检测,应答信息解码,将应答信息装配成飞机的同步应答组形成目标报告,丢弃非同步虚假应答。

关键词:单脉冲二次雷达 应答模式 EPLD

1 一次雷达与二次雷达

二次雷达与一次雷达基本上是并行发展的。与一次雷达相比,二次雷达有回波强、无目标闪烁效应、询问波长与应答波长不等的特点,从而消除了地物杂波和气象杂波的干扰。单脉冲技术应用于二次雷达,可以方便地基于多个波束对目标测量,进而有效地增加数

- 关键字:

EPLD 单脉冲二次雷达 应答模式

epld介绍

EPLD EPLD: Erasable Programmable Logic Device(可擦除可编辑逻辑器件)可擦除可编程逻辑器件(EPLD)是一种集成电路,包括一系列的编程逻辑器件,其无需进行再次连接。

1、PLD器件的设计步骤

1.电路逻辑功能描述

PLD器件的逻辑功能描述一般分为原理图描述和硬件描述语言描述,原理图描述是一种直观简便的方法,它可以将现有的小规模集成 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473