串行数据转换器接口

问:我现在需要安装节省空间的数据转换器,认为串行式转换器比较适合。为了选择 和使用这种转换器,请问我需要了解些什么?

本文引用地址:https://www.eepw.com.cn/article/202572.htm答:首先我们看一下串行接口的工作原理,然后再将它与并行接口相比较,从而可以消 除对串行接口数据转换的神秘感。

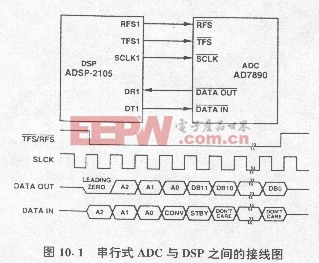

图101示出了一种8通道多路转换12位串行式模数转换器(ADC) AD7890与一种带串行接 口的 数字信号处理器(DSP) ADSP2105接线图。图中还示出了使用DSP与ADC通信的时序图。通过 一根线以串行数据流的形式传输12位转换结果。串行数据流还包括3位地址,用来表示AD789 0当前被选中的多路转换器中的输入通道。为了区分不同组的数据串行位流,必须提供时钟 信 号(SCLK),通常由DSP提供。有时ADC作为输出信号提供这种时钟信号。DSP通常(但不总是) 提供一个附加的成帧脉冲,它要么在通信开始第一个周期有效,要么在通信期间(例如TFS/R FS)有效。

图101 串行式ADC与DSP之间的接线图

在这个实例中,利用DSP的串行端口来设置ADC内部5位寄存器。这个寄存器的位控功能包 括:选择通道、设定ADC处于电源休眠方式和起动转换。显然,这种情况下串行接口必 须双向工作。

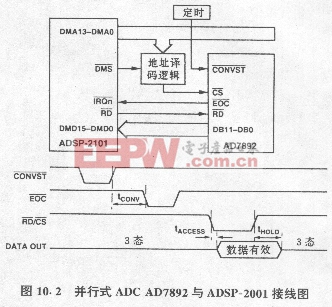

从另一方面来说,并行式ADC的数据总线直接(或可能通过缓冲器)与带接口的处理器的 数 据总线相连。图102示出了并行式ADC AD7892与ADSP2101的接线图。当AD7892完成一次 转换后,中断该

图102 并行式ADC AD7892与ADSP2001接线图

DSP,DSP响应后,按照ADC的译码内存地址读一次数据。串行式数据转换器与并行式数据转换器之间的重要差别在于需要的连接线数。从节省 空间的角度来看, 串行式数据转换器有明显的优点。因为它减少了器件的引脚数目,从而有可能做成8脚DIP或 SO封装的12位串行式ADC或DAC。更重要的是它节省了印制线路板的空间, 因为串行接口只需连接几根线条。

问:我的数模转换器(DAC)必须离中心处理器及其它处理器距离很远。我最 好采用何种方法?

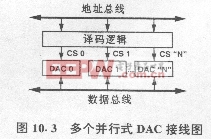

答:首先你必须确定是使用串行式DAC还是并行式DAC。当使用并行式DAC时,你应该确 定每个DAC进入存储器I/O端口的地址,如图10.3所示。然后你应该对每个DAC编程,将写命 令直 接写入适当的I/O口地址。但这种结构具有明显的缺点。它不但需要并行数据总线,而且到 所有远处的端口都需要一些控制信号线。然而串行接口只需要为数不多的两条

图103 多个并行式DAC接线图

线,显然它比并行接口经济得多。 一般说来,虽然串行式数据转换器不能对处理器的存储器寻址,但是可以把许多串行DA C接到处理器的串行端口上,然后利用处理器的其它端口产生片选信号来逐一地启动每个DAC 。片选信号虽然仅需要一条线就能将每个DAC都接到串行接口上,但是接到处理器上传输 片选信号线的数目可能受到限制。

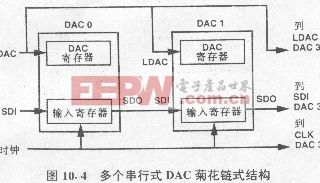

解决这个问题的一种方法是采用菊花链(daisychained)式结构,将所用的串行式DAC 都连在一起。图10.4示 出了如何将多个DAC连接到一个I/O端口上。每个DAC都有一个串行数据输出(SDO)脚,将第一 个DAC(即DAC0)的SDO脚接到本菊花链中的下一个DAC(即DAC1)的串行数据输入(SDI)脚。LDAC 和 SCLK以并行方式被送到本菊花链中的所有DAC。因为在时钟作用下送入SDI的数据最终都要到 达SDO(N个时钟周期之后),所以一个I/O端口能够寻址多个DAC。但是这个I/O端口必须输 出很长的数据流(每个DAC占的N位乘以本菊花链中DAC的数目)。这种结构的最大优点是不需 要对寻址的DAC进行译码。所有的DAC在相同的I/O端口上都有效。菊花链式结构的主要缺点 是可达性(accessibility)或等待时间长。即使要改变某一个DAC的状态,处理器也必须从该 I/O端口输出全部数据流。

图104 多个串行式DAC菊花链式结构

问:既然串行式数据转换器节省许多空间和线路,那么为什么不在每个要求节省空间的 应用场合都使用它们呢?

答:串行式数据转换器的主要缺点是为了节省空间从而降低了速度。例如,对并行DAC 编程,只用一个写脉冲便可以把数据总线上的数据在时钟作用下送入DAC。然而,如果要把 数据写入串行DAC,那么DAC的位数必须等于相继的时钟脉冲数(N位DAC需要N个时钟脉冲), 每个时钟脉冲后还要跟随一个装入脉冲。所以这种处理器的I/O端口与串行数据转换器通信 要花费相当多的时间。因此吞吐率高于500 ksps 的串行式DAC平常是少见的。

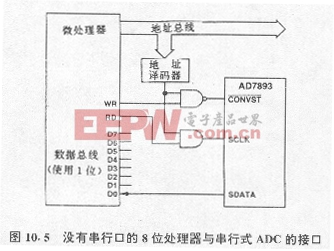

问:我的8位处理器没有串行接口,有什么办法可以把一个12位串行 式ADC(例如AD7993)接到该8位处理器总线上?

答:当然我可以使用外部移位寄存器,将数据用串行(和异步)方式装入移位寄存器,然 后在时钟作用下进入处理器的并行端口。但是,如果这个问题的着眼点是“没有外部逻辑” ,那么可以把这个串行式ADC看作1位并行式ADC来连接。将该ADC的SDATA脚接到该处理器 数据总线的一条数据线上,这里接到数据线D0。如图10.5所示。使用某种译码逻辑电路 , 能使 该ADC的口地址看作是该处理器的一个存储器地址,以便用12个逐次读命令读取ADC的转换结 果。然后用附加的软件命令把12个字节的LSB组合起来,拼成一个12位的并行字。

图105 没有串行口的8位处理器与串行式ADC的接口

上面介绍的方法有时称作“位拆裂”(bit banging)。从软件的观点来看,这种方法是很 不经济的,但是当处理器的运行速度远远高于ADC的转换速度时,这种方法可以采用。

问:在前面的例子中,利用了处理器的写信号门控方式来 起动AD7893转换。请问这种方法是否有问题?

答:我很高兴你看出这一点。在这个例子中,每转换一次都要对AD7893的寻址存储器发 出一个空操作的写命令。虽然没有数据交换,但是处理器仍然提供开始转换所需要的写脉冲 。从硬件的观点来看,这种结构非常简单,因为它不必再产生一个转换信号。

但是,对信号必须进行周期性采样的交流数据采集应用场合,不推荐这种方法。即使程 控处理器,对ADC发出周期性写命令,写脉冲的相位抖动将会严重降低实际得到的信噪比。 经过门控之后写脉冲会抖动得更坏。例如,假设采样时钟相拉抖动仅仅1 ns,对一个理想的 100kHz正弦波来说,其信噪比会降到大约600dB(低于10有效位分辨率)。另外一个缺点是, 过冲和采样信号噪声都会进一步降低模数转换的完整性。

评论