基于ACE约束的S-IRA编译码器设计

摘要:考虑到结构化非规则重复累积码具有准循环的结构便于硬件实现,采用了结构化非规则重复累积码进行编码器设计。准循环矩阵的构造采用了基于ACE约束的PEG填充构造方法。结合所用码型的特点,设计出了简单有效的编码流程图。译码方面,采用了分层修正最小和译码算法,并设计出了译码器结构。

关键词:结构化非规则重复累积码;分层修正最小和译码算法;编码器结构;译码器结构

O 引言

重复累积码(Repeat-Accumulate Codes)是由D.Divsalar等人于1998年提出的,作为LDPC码与Turbo码的一个子集,在译码方面它具有LDPC码优异的性能以及并行译码的优势,在编码方面又同时具有Turbo码线性复杂度的特点,因此受到广泛关注。在实际应用方面,欧洲DVB-S2标准中的信道编码部分采用了RA码的技术。经过近几年的研究,重复累积码有了一些新的发展,如非规则重复累积码(IRA)、扩展重复累积码(elRA)、累积重复累积码(ARA)、结构化的非规则重复累积码(S-IRA)等,这些码对RA码的误码性能、误码平层、编码复杂度以及码率的灵活性等方面进行了改善。

为了减少硬件实现的复杂度,提高编译码器的吞吐量,将校验矩阵构造成准循环形式是一种普遍被采用的方法。因此,考虑到S-IRA码具有准循环形式,本文采用了基于ACE约束的S-IRA码进行编码器设计,使用分层最小和译码算法进行译码器设计。

1 编码器设计

1.1 RA码校验矩阵设计

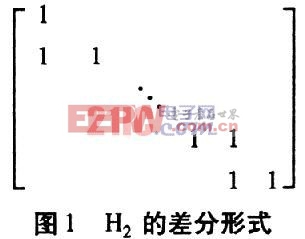

RA码编码就是将信息位u中的每一位重复q次,经过交织以后输入传输函数为的累加器,经过累加即得到校验位p,完成编码。RA码可分为非系统码和系统码两类,RA码与IRA码系统码的校验矩阵可以表示为H=[H1H2]。H1的列重为{db,t},行重为{dc,i}。H2具有差分形式:

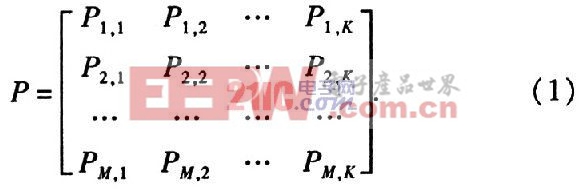

由于H2的差分形式,可以直接使用校验矩阵H进行编码,为了降低编码复杂度,将H1设计成准循环形式,即为结构化的IRA码(S-IRA)。但如果将H1直接构造成准循环形式,H2的双对角线形式会使构造出的校验矩阵最小汉明距离太小,而先构造与H1相同大小的准循环矩阵P,再将P进行行交织得到H1则可以避免这个问题。

在设计校验矩阵时,采用了中提出的基于近似环外信息度(Approximate Cycle Extrinsic Message Degree)约束的边增长算法(PEG)来构造准循环矩阵P。

1.2 编码器结构

编码器最复杂的部分在于信息位u通过准循环矩阵PT,即进行uPT的运算。本文采用上海交通大学无线通信研究所LDPC小组提出的SRAA(shift-register-identity-matrix-ad-der-accumulator)结构进行uPT的运算。

假设准循环矩阵P的大小为M×Q行,K×Q列。其中Q×Q为P中循环置换矩阵和全零矩阵的大小。将信息序列u顺序分成K段,每段长为Q比特,即u=(u1,u2,…,uK),其中 。将准循环矩阵P写作:

。将准循环矩阵P写作:

其中Pi,j为P中的循环置换矩阵或者全零矩阵。在硬件中存储P时,只需存储每个Pi,j第一列“l”元素的位置,![]() 当Pi,j为全零矩阵时,存储的位置为O。

当Pi,j为全零矩阵时,存储的位置为O。

评论