高速传输需求飙升 PCIe讯号测试不妥协

随着科技的迅速发展,数字数据转换正面临着前所未有的挑战。从人工智能的应用到高画质影音串流服务的普及,再到自动驾驶技术的日益成熟,数据流量正在以惊人的速度增长。这种趋势也在网络和运算领域引发了一系列的变革,人工智能和分解技术的引入,进一步提升了运算、服务器和储存系统的效能。这些技术的快速发展推动着对于高速数字接口的需求,例如PCI Express(PCIe)、USB、DDR等,这些接口在当今数字世界中扮演着至关重要的角色。

高速数字系统的挑战

高速数字系统面临着众多技术挑战。其中最主要的挑战,来自于高速数字讯号频率特性以及传输线材料的高频损耗。

高速数字系统的研发过程包括对芯片、功能电路区块、电/光线路和连接器等组件的深入研究。从最初的原型设计到后续的除错、设计验证和认证合规性测试,工程师们透过不懈的努力,不断提升着高速数字讯号的质量与效能。

然而,高速数字系统同时也面临着众多的技术挑战。其中,最主要的挑战来自于高速数字讯号频率特性以及传输线材料的高频损耗。这些因素导致了讯号衰减、频率抖动、串扰和眼图等问题的出现。

频率抖动是数字讯号时间轴上的时序变化,受到多种因素的影响,例如电路和通讯路径中的噪声;而串扰则是相邻讯号线之间的讯号泄漏现象,可能导致高速数字系统的误操作;眼图作为评估数字讯号质量的重要工具,用于展示串行数据讯号中0和1数据流的图形。

克服这些技术挑战是高速数字系统开发中的一个重要任务,这需要工程师们不断寻找创新解决方案,以确保高速数字系统的可靠性和性能。

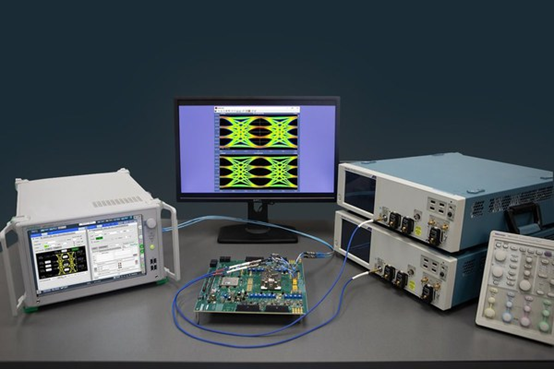

图一 : 一体化讯号质量分析仪结合了多种测试功能。

深入了解PCIe

在当今数据驱动的世界中,高速数据传输已成为数据中心、车辆系统、运算和储存领域的核心需求。而PCIe作为一种扩充总线和插槽接口标准,正在引领着这个领域的发展。PCIe标准由PCI-SIG管理和定义,其不断演进以适应日益增加的数据需求。

PCI-SIG不仅专注于传统电线技术,还在积极研究最新的光学电路,目的在克服当前数据传输速度的限制。与传统的电线技术相比,光学电路能以更快的速度传输数据,同时降低能量损耗,这对于未来数据中心和高速运算系统的发展至关重要。

然而,PCIe的发展并非一帆风顺,它面临着来自技术和设计的挑战。早期的PCIe 5.0标准及以前版本使用了不归零(Non-Return-to-Zero;NRZ)代码,其中数据1由正电压表示,数据0由负电压表示。然而,随着数据需求的增加,PCIe 6.0和7.0标准导入了脉冲幅度调变(Pulse Amplitude Modulation;PAM)技术,采用四个电压(PAM4)来表达2个数据位,并导入了前向纠错(Forward Error Correction;FEC)。虽然PAM4提供了更高的传输速率和更大的容量,但其误码率(Bit Error Rate;BER)更容易受到抖动和噪声的影响,进而增加了设计的复杂度。

在PCIe的开发过程中,从原型设计到商业发布的每个阶段都需要评估高速数字系统的讯号质量。测试讯号质量是为了提高产品质量,并确保讯号的可靠性。此外,为了确保主机与装置的互联性,物理层测试也变得至关重要,例如抖动容限测试和链路训练评估。

PCIe测试与分析技术

在当今高速数据传输的世界中,PCIe已经成为许多系统的核心接口标准。然而,要确保PCIe设备的稳定运行,进行有效的发射器、接收器以及协议测试是至关重要的。

发射器与接收器测试

发射器(Tx)测试旨在评估PCIe设备输出的参考频率和数据讯号的各种特性,如上升/下降时间、振幅、眼图宽度和抖动等。这些测试通常使用实时示波器(Real-Time Oscilloscope;RTO)进行,同时锁相环(Phase Locked Loop;PLL)带宽则由脉冲模式产生器(Pulse Pattern Generator;PPG)作为讯号源进行测量。

接收器(Rx)测试则是透过PPG和误码率(Bit Error Rate;BER)测试仪对电讯号施加压力,例如噪声和抖动,来评估PCIe装置的抖动容限、串扰和运行裕度等。

协议测试

协议测试涉及使用链路训练状态机(Link Training and Status State Machine;LTSSM)来管理物理层中连接的状态转换。这些测试可以评估LTSSM是否正常转换,并分析链路训练和LTSSM,以确定是否存在物理或逻辑错误。

Tx、Rx和协议测试通常可透过一体化讯号质量分析仪(如安立知的MP1900A),该仪器结合了实时示波器、脉冲模式产生器和误码率测试仪的功能。测试软件能够轻松设定复杂的测试参数,并自动控制讯号质量分析仪,缩短测试时间,提高测试效率。

互连测试

互连测试涉及使用向量网络分析仪(Vector Network Analyzer;VNA)来评估零件和讯号线的插入和返回损耗。这对于除错和性能提升至关重要,可以帮助确定正在开发的原型设备中讯号劣化的原因,并提出改善方案。

PCIe 6.0基本规格测试系统

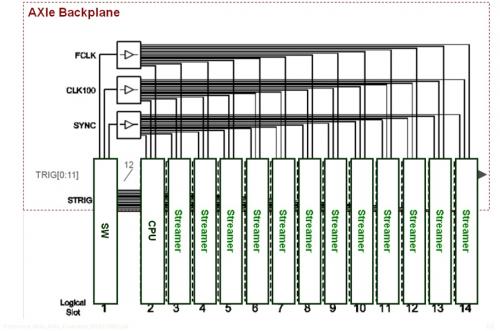

图二 : PCIe 6.0基本规格测试系统

安立知的讯号质量分析仪MP1900A兼具测试重现性和简单的操作等优点,是一款经PCI-SIG认证的高性能误码率测试仪。而MP1900A系列,搭配太克科技的DPO70000SX实时示波器,以及通过硅验证的Synopsys PCI Express 6.0 IP,便是一套PCIe 6.0的基本规格测试系统。

PCIe 6.0的前向纠错(FEC)是一项关键技术,可确保32-Gbaud PAM4(64 Gbps)且受传输路径损耗影响的低讯噪比(SNR)讯号之完整性,然而带来的影响是与评估待测物(DUT)有关的复杂度变得更高。为了提高测试效率,使用Tektronix DPO70000SX 实时示波器执行自动基本规范校准和讯号质量评估,并结合安立知的MP1900A,可以实时测量FEC误码率。

根据PCI Express 6.0规格,安立知MP1900A将产生由DPO70000SX示波器校准的应力兼容讯号,并将该讯号传输至Synopsys PCI Express 6.0 IP,即可使用DUT内部错误计数器测量位错误。此外,MP1900A PAM4误码检测器将在DUT回放模式下测量位误差。使用MP1900A的FEC功能,将有助于分析并显示FEC纠正与未纠正错误,以及后FEC误码率,而DPO70000SX实时示波器则将分析来自DUT的讯号波形。

结语

透过不断的研究和创新,PCIe将继续在数据传输的领域中发挥着重要作用。测试讯号质量和寻找新的解决方案将是确保PCIe设备高质量、高效能的关键。对于PCIe设备来说,发射器、接收器和协议测试是确保其性能和可靠性的关键步骤。通过使用先进的测试仪器和技术,工程师们能够更准确地评估设备的性能,并快速解决潜在问题,确保系统的顺利运行和符合标准规范。

评论