面向电路的噪声耦合抑制技术

任何在示波器上仔细观察过低电平信号读数的人都会熟悉电子电路中可能出现的噪声。出现的各种固有的噪声源在低信号电平下十分明显。在其他以典型逻辑电平运行的系统中,由于电磁干扰和电路之间的耦合,会产生外在噪声。这些噪声源都需要一个特定的电路或策略来降低耦合强度或减少噪声,或两者兼而有之。

本文引用地址:https://www.eepw.com.cn/article/202212/441706.htm本文要点

● 电子产品中有许多噪声源,可能出现在系统内部和外部。

● 噪声耦合抑制技术在电路设计层面和物理布线中实施,以抑制特定的噪声源。

● 可以通过布线前和布线后仿真来评估噪声耦合抑制技术的有效性。

任何在示波器上仔细观察过低电平信号读数的人都会熟悉电子电路中可能出现的噪声。出现的各种固有的噪声源在低信号电平下十分明显。在其他以典型逻辑电平运行的系统中,由于电磁干扰和电路之间的耦合,会产生外在噪声。这些噪声源都需要一个特定的电路或策略来降低耦合强度或减少噪声,或两者兼而有之。

噪声耦合抑制技术涉及设计特定电路、使用特定的器件,或在物理布线中放置一些结构来抑制特定的噪声源。对于 PCB 设计师来说,修改物理布线以尽量抑制各种噪声源非常简单。本文将介绍可以使用哪些工具来抑制系统中不同类型的噪声。

将噪声耦合抑制技术与噪声源相匹配

噪声通常是指出现在互连或电路中的任何不需要的信号,并且可以有多个来源。有时,除非掌握必要的信息,否则很难为特定的噪声确定具体的来源。当在电路或互连中检测到噪声时,最好了解是哪种耦合机制带来了不必要的噪声。

所有的电子噪声最后都会导致在接收器上读到不需要的信号,这意味着某种机制在受干扰电路或互连中诱发了一些电压/电流。噪声通过三种可能的机制耦合:

传导:由于噪声源和受干扰电路之间的直接接触,在一个电路中产生的任何噪声电流都可以传导到另一个电路。

电场耦合:一般是指由于电场的存在而在电介质中感应出位移电流。在电路模型方面,电场耦合指的是通过寄生电容耦合。

磁场耦合:变化的磁场可以通过法拉第定律在导体中诱发电流,而不需要噪声源和受干扰电路之间有直接接触。

第一种被称为传导型 EMI,它依赖于噪声源和受干扰互连/电路之间的直接接触。后两种会将辐射型 EMI 耦合到电路中,这是指没有传导到受干扰电路或互连的噪声。

由于辐射型 EMI 可以诱发电流和电压,一开始的辐射型 EMI 可以作为传导型 EMI 被接收。这意味着有两种方法来消除电子电路中的噪声:

● 防止辐射型 EMI 以电容和电感方式诱发电路中的噪声。

● 抑制任何传导型 EMI,不管它是如何在电路中产生的。

● 接下来了解一下可以抑制电子系统中这两种类型噪声的布线策略。

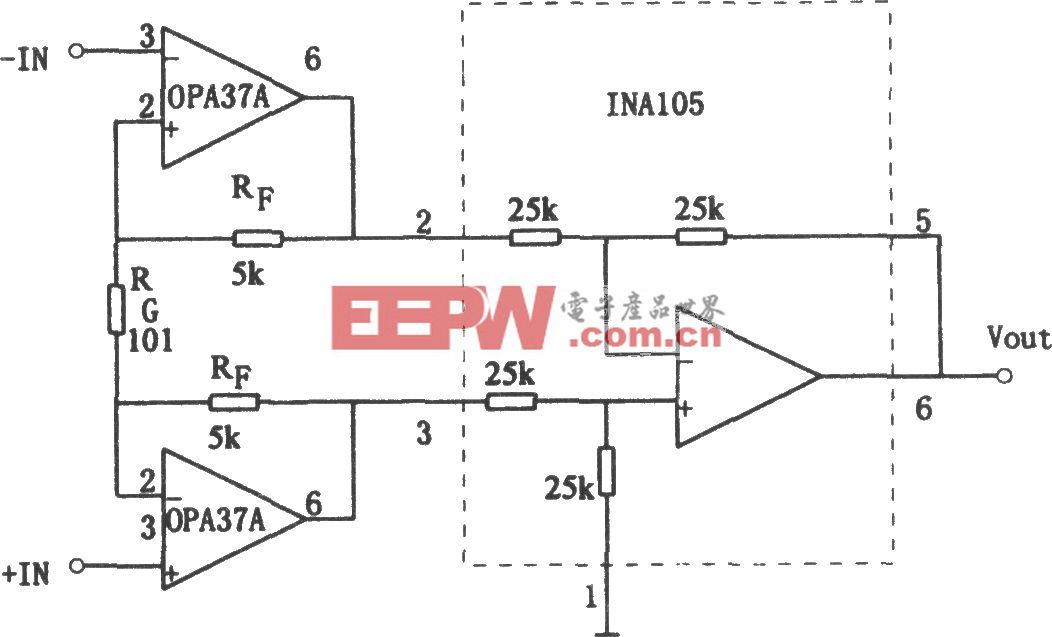

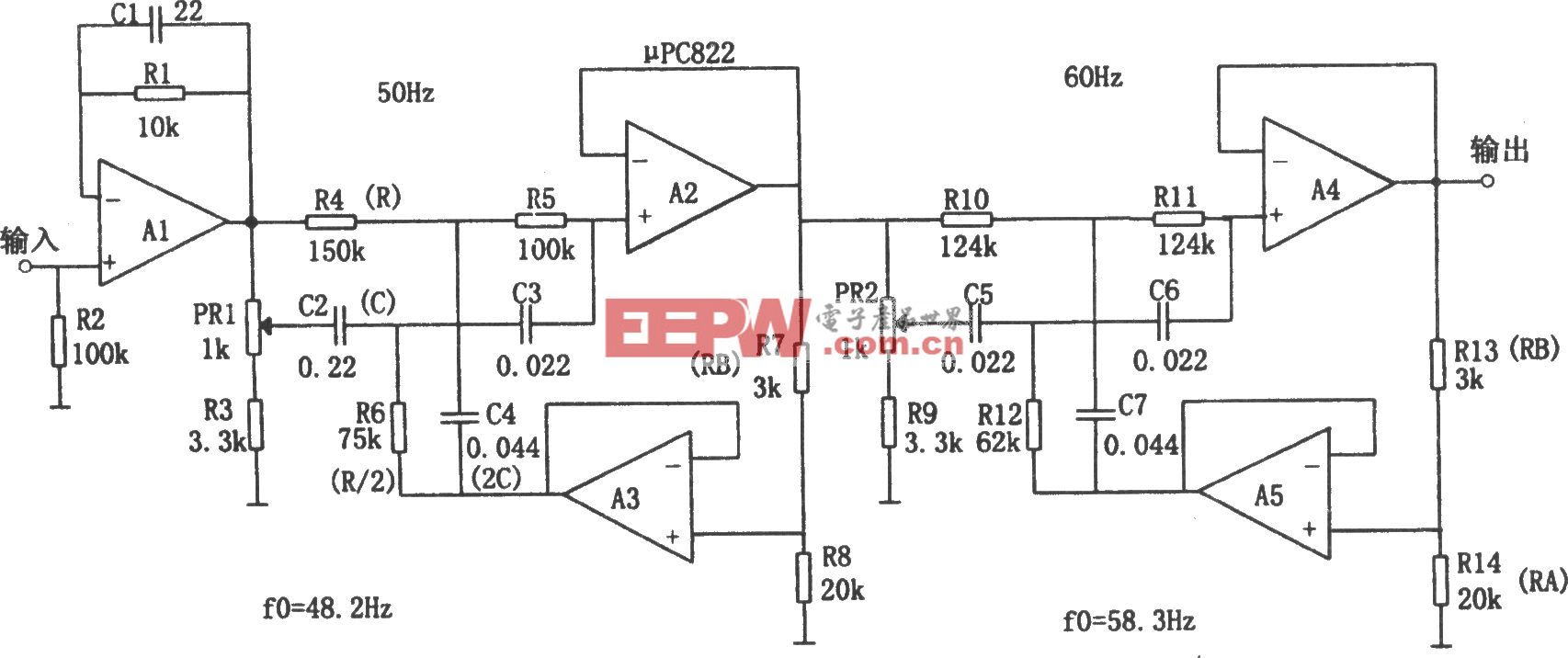

滤波电路

滤波电路是消除传导型 EMI 的经典方法,因为滤波器直接作用于电路中的电压/电流。滤波器可以是宽带的,如低/高通滤波器,或极窄带的,如陷波滤波器。EMI 滤波器可以是单一器件,如共模扼流圈,或是涉及多个器件的复杂电路。这些电路可以针对单一频率或较宽的频率范围来使用。

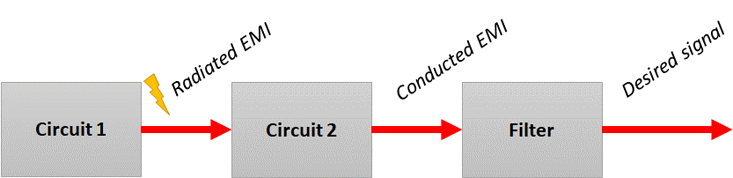

滤波电路可以消除源自辐射型 EMI 的传导型 EMI。通过这种方式,滤波电路抑制了来自电路 1 和电路 2 的任何噪声耦合。

印刷屏蔽结构

这个方法听起来略显陌生,但它通常是指 PCB 上任何可以对辐射型 EMI 提供屏蔽的结构。这些结构的目的是改变 PCB layout 中的寄生效应,从而阻断电磁感应的电流。这种结构的例子包括:

● 电子带隙结构

● 表层覆铜接地

● 额外的平面层

● 沿着波导或天线馈线等重要互连的过孔栅栏

● 重新设计互连结构

这种方法的目标是抑制导致磁耦合或电耦合的寄生效应。要成功做到这一点,需要从物理布线中提取寄生电容和电感的模型。互连阻抗取决于自电感和自电容的值,而寄生效应总是会导致互连阻抗与期望值有所偏差。一些额外的印刷结构或重新设计互连的几何形状有助于减少寄生效应,并减少通过辐射型 EMI 耦合到互连的任何噪声的强度。

总结

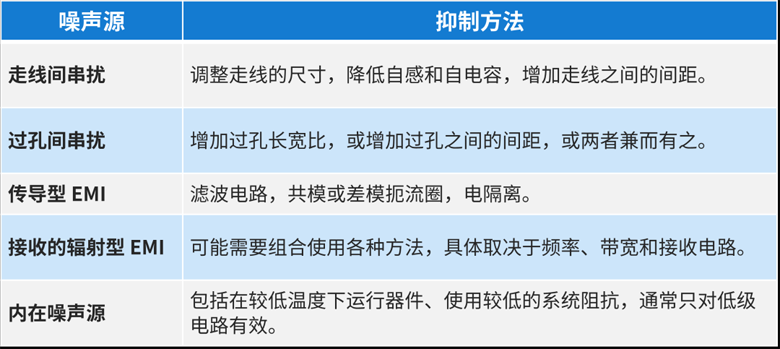

综上所述,没有哪种特定的技术可以抑制所有形式的噪声耦合。在系统中使用哪种具体的噪声耦合抑制技术,取决于所涉及的特定噪声源和电路间耦合的功率。我们通过下列表格对上文讨论的噪声源和抑制方法进行了简要总结。

如果有了合适的降噪技术,并准备在系统中进行验证,最好在做原型设计之前使用仿真来对设计进行评估。传导型 EMI 可以在电路仿真中用 SPICE 进行检查。对于其他噪声源而言,除非有一个准确的电路模型来描述系统,否则无法在电路层面上进行检查。因为这些其他的抑制机制取决于精确的物理布线,所以需要用 3D 场求解器来全面评估许多噪声抑制技术的有效性。对于 PCB 设计工程师来说,最好的场求解器应用可以直接在 PCB 设计工具内使用,并能直接根据布线数据运行模型。

无论需要解决什么噪声源,都可以使用具有集成 3D 电磁场求解器和全套 CAD 工具的 PCB 设计和分析软件来应用这些噪声耦合抑制技术。Cadence 可以提供强大的软件,自动执行系统分析中许多重要的任务,包括一系列布线前和布线后仿真功能,顺利完成系统评估。

(来源: Cadence楷登PCB及封装资源中心)

评论