高动态范围的电容测量电路

摘要:本文介绍了一款电容检测电路(CDC),其中给出了一种基于电荷转移型AFE,在宽待测电容范围下针对不同大小的电容进行粗测和细测两次测量以获得最佳测量值的粗细测逼近型AFE,并为此设计了一种结构简单有效的控制时序以及对应的逻辑电路和针对获得的ADC输出值设计的可编程除2电路。同时,为了将AFE和ADC隔离开来,提出了AFE和ADC的匹配中间级结构(高精度跟随器)。

0 引言

电容数字转换器是专为激励电容式触摸传感器设计,具有低功耗、高集成度、高精度测量的特点,已成为消费电子领域中电容传感器应用的主流产品。随着的工艺和技术的不断发展,电容的大小在不断减小,这令对电容的检测产生了一定的难度,基于这样的现状,我们设计了一款具有转换精度高(转换有效位数为11-bits),电容检测范围(电容检测为1 fF~2 pF)宽,电容速率为400 μs的电容检测电路(CDC)。

1 系统整体设计

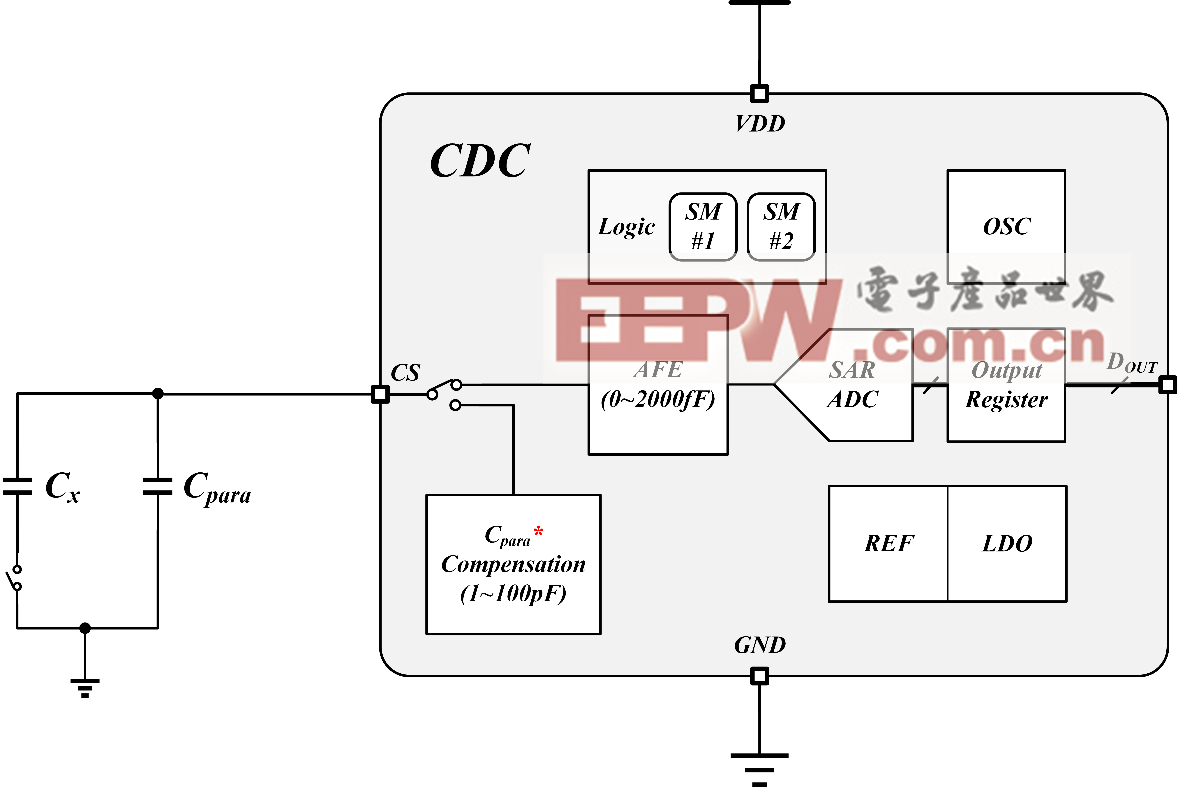

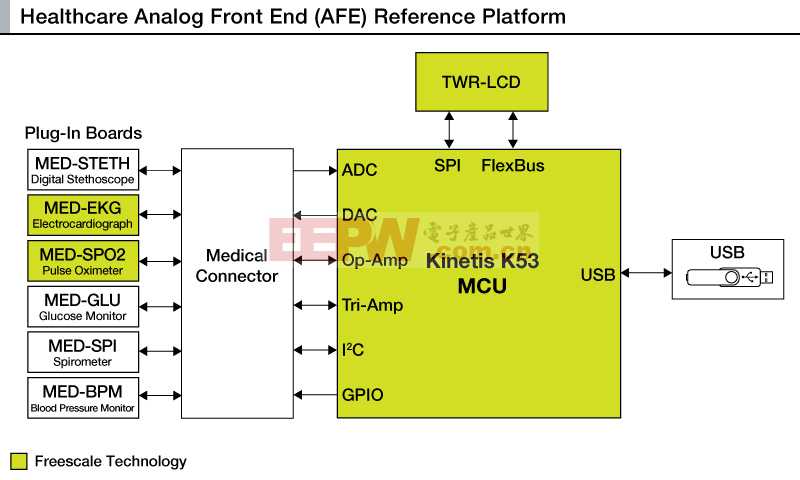

本设计的顶层电路如图1所示,为本作品CDC总体框架结构,片内产生基准和时钟,主干结构为AFE和ADC,进行输入电容至数字量的转换后,由输出寄存器进行简单的DSP,然后输出数字量至片外。

图1 CDC系统顶层电路(*标记的寄生电容补偿电路仅停留在前仿/原理验证阶段)

2 高速电荷转移型-粗细测AFE设计

2.1 AFE整体电路介绍

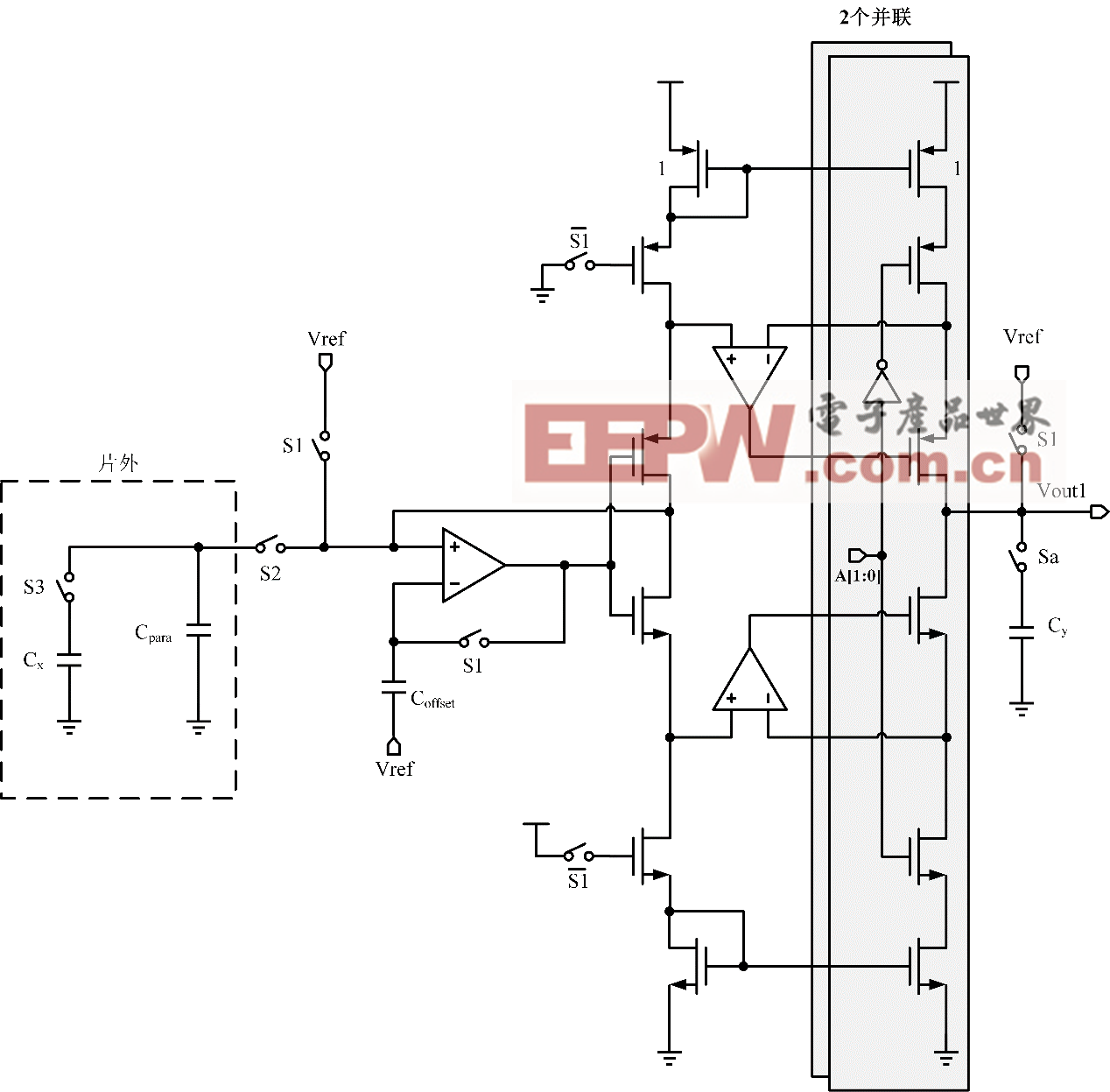

图2 电路原理图

本文提出的电路是一种将微弱电容值转换为数字量的集成电容测量电路,该电路是基于电荷守恒提出的电容测量原理如图2所示,其创新处在于控制时序、模拟前级电路结构、以及控制算法。

该电路由模拟前级电路(AFE)、ADC、输出移位寄存器和控制逻辑电路四个部分组成,模拟前级电路用于将输入的待测电容的电容值线性对应地转换成一个可供ADC测量的电压值,其由若干个电容、运放、MOS管、电压跟随器、反相器、以及MOS管开关组成。

其中,所用到的运放是一个低失调电压的一级运放,Coffset是一个用于在校正过程中存储运放的输出失调电压的皮法电容,Vref是外部引入的参考电压,Cy是用于收集电荷的电容。电压跟随器采用一级或二级结构,用于隔离ADC和AFE,并提供阻抗匹配。

模拟前级电路中心的电流镜结构采用1:1的宽长比,用于将流过左端补给至Cx的电荷复制到右端的Cy,电流镜右端为2个相同结构的电路并联,不同之处在于反相器的输入为A[0]至A[M-1]. A[M-1:0]是由控制逻辑电路产生的,用于控制流入到Cy的电荷的增益倍数,是一个2位的数字信号。

整个电路一共用到7个开关,其中S3控制的是片外的任意形式开关,剩余的6个开关为片内的MOS管开关,它们的作用简述如下:

S1:控制模拟前级电路电路初始化

S2:连通片外与片内电路的控制信号

S3:控制片外待测电容Cx是否接入

模拟前级电路左方框内的电容Cx是片外的待测电容,S3是一个受控与控制逻辑的开关,Cpara是片内外Pad的寄生电容。

2.2 粗细测时序设计介绍

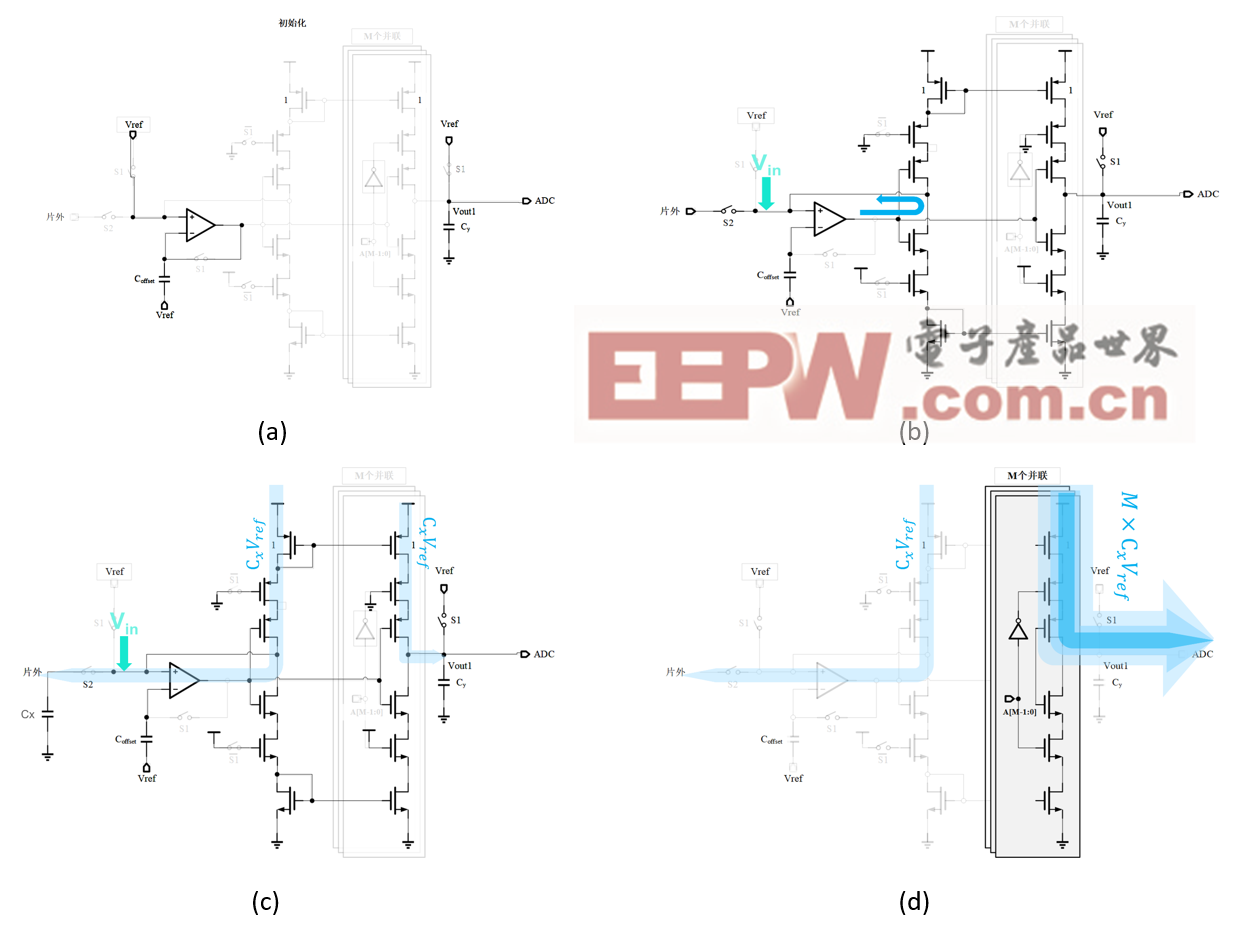

图3 开关状态图:(a)初始态 (b)就绪态 (c)接入待测电容 (d)调整增益档位

AFE运行时需要频繁地进行开关切换,可总结为以下4个步骤,4个步骤对应的开关状态如图图3(a)(b)(c)(d)所示。以下参照时序图和电路原理图给出各个时间点电路进行的动作。

T0:将A设为(11)2,开始进行电容值测量。

T1:电路初始化,运放同相输入端的反馈环路断开、反相输入端的反馈环路接通,运放的失调电压Voffset被保存至Coffset,Cy被初始为Vref,ADC的反相输入端持续采集接入待测电容之前的AFE输出电压。

T2:将芯片的测量引脚导通,断开用于初始化的开关,此时运放的反相输入电压为Voffset,抵消了运放的失调电压。同时将寄生在Pad和外部连线的等效寄生电容充电至Vref。

T3:断开ADC的反相输入端,此时已经将接入待测电容前的AFE输出电压保存到ADC的反相输入端,记为VN。

T4:接入待测电容,运放的同相输入端被拉低,控制推挽级补充电荷。同时,电流镜将M倍的电荷注入到Cy,等待电路稳定后,Cy的上极板电压VP被保存到ADC的同相输入端,ADC开始转换VP-VN的值。

T5:第一次采集完成,ADC的输出值为D1,假设ADC的最大输出值为Dmax,如果D1>Dmax/2,则A变为(01)。如果D1<Dmax/2,则A不变。

T6:再进行一次T1至T4,获得ADC第二次的输出D2,将D2送入输出移位寄存器,并将D2进行重复左移1位运算,重复右移M次,获得实际的测量值。

2.3 AFE与SAR ADC的匹配中间级设计(高精度跟随器)

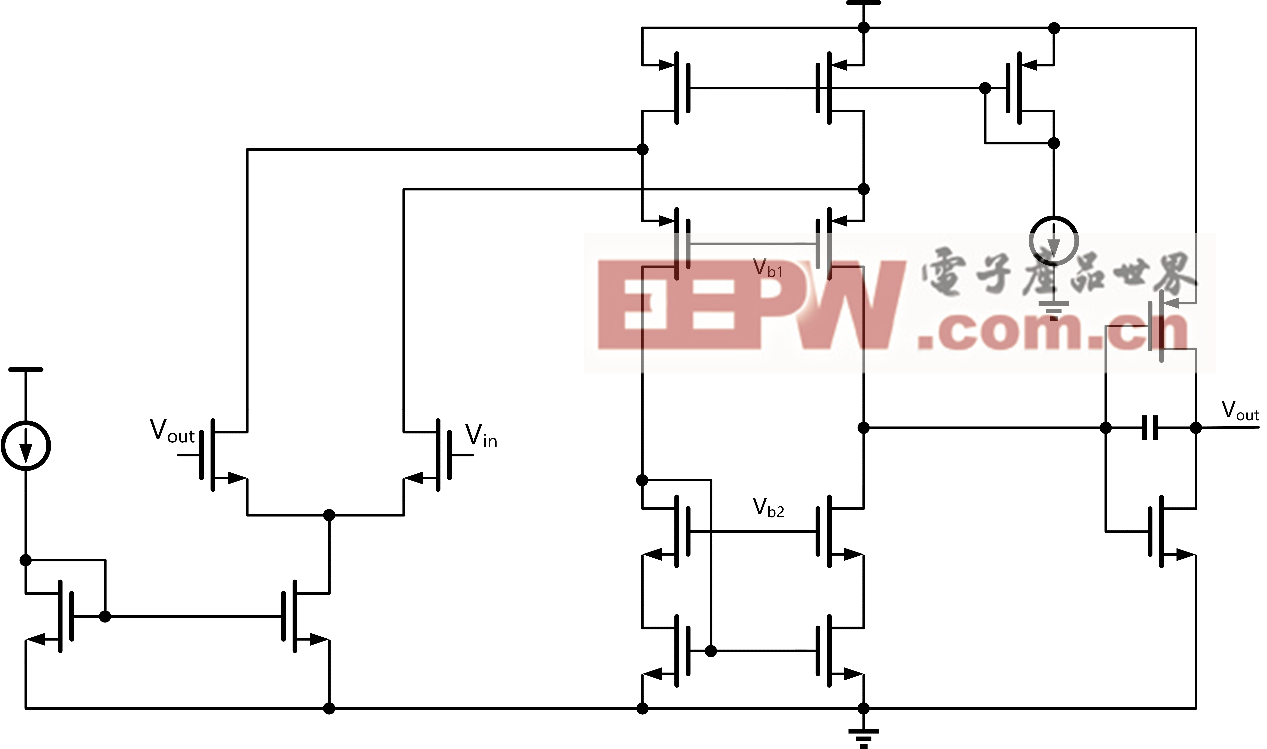

由于本设计采用电荷转移型AFE,其原理是用一个小的待测电容收集电荷。因此不能直接将AFE接入DAC,给电容阵列充放电。因此,需要设计一个跟随器来做AFE和ADC之间的隔离。普通的跟随器误差远远超过1LSB,为此,高精度跟随器在本设计中被提出。

如图3通过使用套筒型折叠共栅运放作为第一级来提高增益,同时,运放的输出级接形成推挽结构的连个mos管,提高摆率的同时提高其驱动能力。此外,将电路接成负反馈,实现单位增益,从而实现输入输出的跟随。

图3 高精度跟随器结构

2.4 AFE仿真测试结果

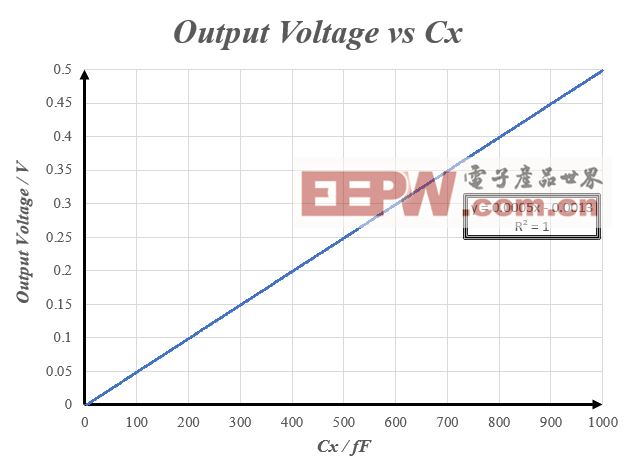

图4.1所示是AFE在增益为2时,输入电容从0到1 pF的扫描结果, 可以看出输入电容在0~1 pF范围内,输出电压的线性度较好,根据Excel的线性拟合工具可知,输入输出之间的表达式为:

Vout = 0.000 5 Cx - 0.001 3

R² = 1

另外,在增益为2时,1 fF对应0.5 mV的电压输出。

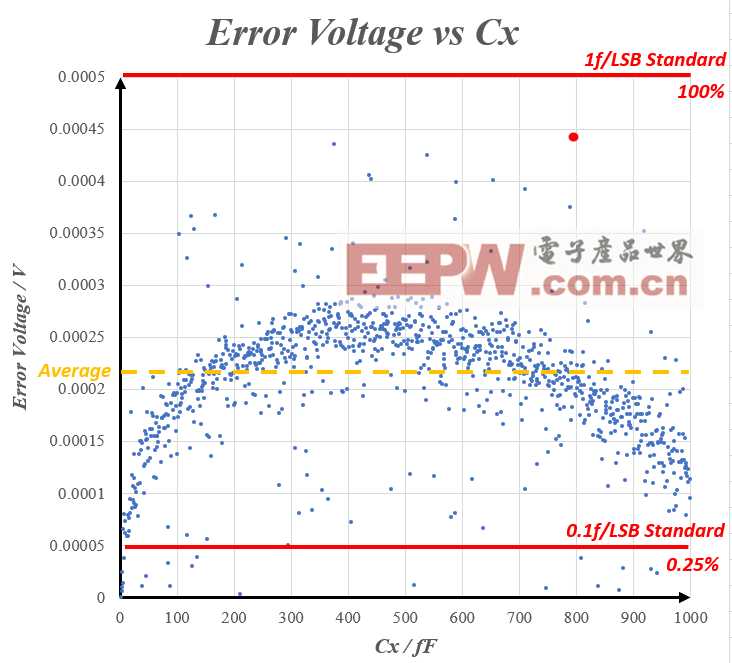

根据图4(a)所示的扫描结果,计算与理想输入输出表达式(Vout = 0.000 5 Cx)之间的误差可得图4(b)的误差散点图,可以发现,按照赛题要求的1 fF / 1 LSB精度,本设计的AFE可以100%满足,且99.5%以上的待测电容测量误差小于0.5 LSB,给后续的设计留足了余量。

将测试数据统计如表1所示。

平均误差/mV | 0.2 |

最大误差/mV | 0.44 |

平均误差/LSB | 0.416 |

最大误差/LSB | 0.83 |

(a)待测电容1000点扫描结果 (b) 误差测试结果

图4 仿真测试结果图

3 芯片仿真结果总结

3.1版图总体设计

高动态范围的电容检测电路CDC内部集成了前端AFE模块,ADC模块,还有数字控制逻辑等模块,把电容量转成电压量再通过ADC模数转换输出数字量,这过程中涉及到数字信号与模拟信号的影响,数字控制部分与模拟部分之间会出现相互干扰引入噪声,所以版图设计过程中需要对电路进行合理布局,降低模块之间的串扰,提高系统稳定性与适配性。

在进行电路版图设计尤其是数模混合电路版图设计的时候,要遵循布局布线的一些基本原则。

在布线原则中,需要满足各层金属的最小线宽与间距要求,同时关键信号尽量避免长走线,同时避还要考虑天线效应等问题,连线的时候应该每一层都选择走相同方位的走线,层与层之间走线应选择交叉走线避免平行

在布局上,首先对于那些在电路中的处于等电位的 MOS 管的端口,要尽可能让它们共用有源区部分,让连线最短,并且要减少版图的面积;对于数字电路部分与模拟电路部分要区分开,并且可以加上隔离保护环,可以在电源上分开数字部分与模拟部分,区分电源地与数字地。比如让比较器,运放等部分与和它们相关联的偏置电路远离数字模块,本次作品中采用了额外的LDO对比较器部分进行供电,同时用保护环作为模块进行隔离操作。

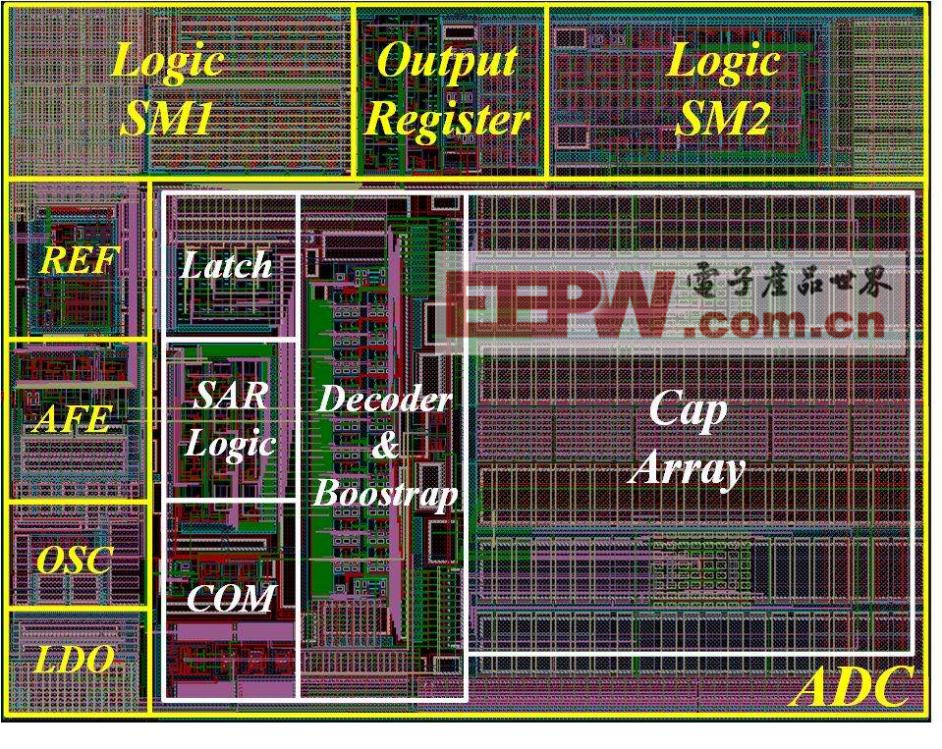

本次版图验证采用的是GF的0.18um工艺库。如图5.1所示,是版图的总体布局规划,主要以信号流为准,从左边AFE输入,输出信号接入右边ADC进行测量,ADC输出通过左上方数字逻辑控制后从上端输出结果。

版图左边端口CS为被测电容接入点;ES为External start为电容测试使能信号,高电平有效;Twice_Finsih为数据输出有效信号,当输出为高电平时表示输出数据有效;D0~D11为输出数据位。整体版图是由数字和模拟两大部分组成,ADC位12位的SAR ADC,版图将比较器与AFE等模拟部分电路放在左下角,与数字电路部分区分开,右边为电容阵列。

图5为整个CDC系统的版图layout(布局)图,芯片整体面积为760 μm×990 μm,ADC部分面积为560 μm ×800 μm,AFE模块面积为90 μm × 155 μm,Control Logic(控制逻辑)部分面积为220 μm × 410 μm。总共使用到电容136.38 pF,电阻1 210 kΩ。

图5 版图总览

3.2 CDC参数扫描测量结果

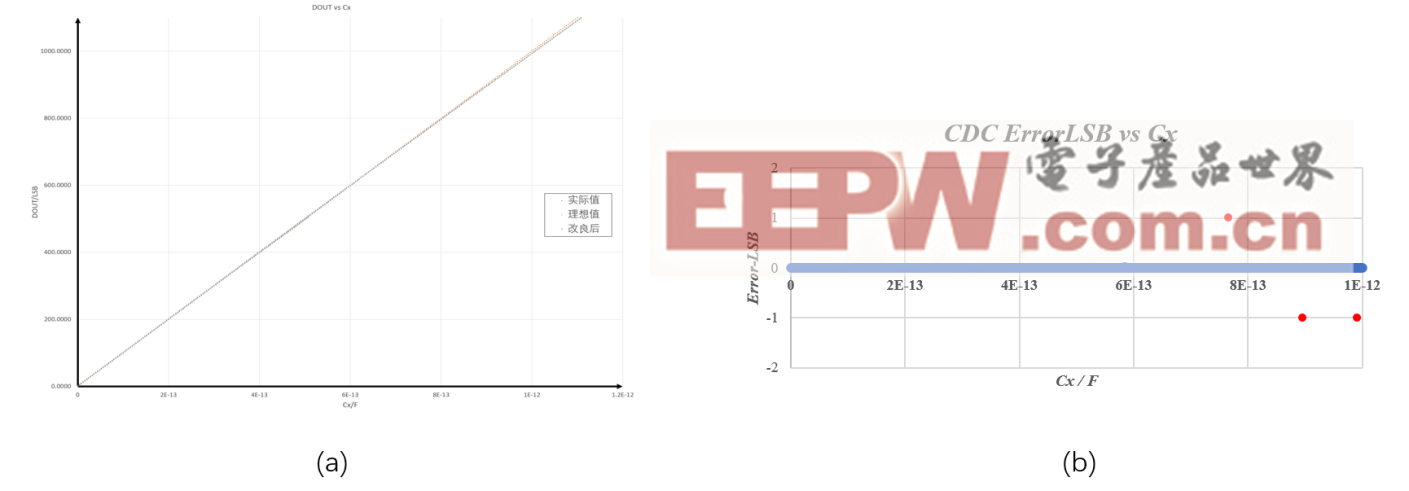

图6(a)为本次设计CDC输入电容参数扫描结果。扫描范围从1 fF~1 pF,扫描步进为4 pF,图中3条线分别对应实际值,理想值与改进值。

根据Excel提供的拟合工具,R2为1,线性度较好,与AFE的测试结果类似,说明后级并没有引入误差。

图6 CDC参数扫描结果:(a) 输入电容参数扫描结果 (b) 输入电容参数扫描结果偏离理想值的情况

结果分析:首先,上述两图中改良前的结果与第4节中提到的AFE测试结果变化趋势相同,即在整个量程内只有1LSB以下的误差;为了增大待测电容的测量范围,配合展望中提出的补偿电容方法,本文提出了多档增益测量技术,并因此将CDC的测量范围拓展到了2 pF,1 000 fF以下的误差值控制至小于1LSB,而(1~ 2) pF范围内的误差控制在了2LSB以内。

最终将本文设计的CDC性能指标列出,如表2所示。

表2 本文所设计的CDC性能指标

本文设计CDC性能指标 | |

粗测量范围 (误差<2LSB) | 0~2 pF |

细测量范围 (误差<1LSB) | 1 fF ~ 1 pF |

精度 | 1 fF |

1 pF内最大误差 (温度:27℃) | 1LSB |

1 pF内平均误差 (温度:27℃) | -0.001LSB |

工作电压范围 | 2.5~3.5 V |

4 结语

本作品设计了高动态范围的电容测量电路,该电路实现在较大范围内对变化量较小的电容进行检测并且输出的功能,且具有高精度的特性。在此基础上对电容检测电路的各个模块及整体电路进行了仿真测试、数据分析以及版图设计。

本作品设计的电容检测电路包括电荷转移型AFE与SAR ADC。提出了多档增益测量技术,并因此将待测电容在400 fF以下时检测的误差值控制至小于1LSB。该电荷转移型AFE能实现在1 fF ~ 1 pF范围内的电容检测。此外,设计了11位低功耗低速率 SAR ADC。SAR ADC的比较器应用了失调电压消除技术,将比较器失调电压降低至1LSB以内,避免对ADC造成误差。提出了高精度的跟随器并将其应用于AFE和ADC之间做为匹配中间级,该跟随器能驱动大电容并具有高精度的特性。

本作品的设计参数如下表所示:电容检测电路能够实现从1 fF到1 pF的电容检测并且满足设计指标。

性能指标 | 比赛要求 | 本电路设计参数 | 是否达到设计要求 |

工作温度 | -40~125 ℃ | -40~125 ℃ | √ |

工作电压 | 2.5~3.6 V | Typ.:3.3 V Range:2.5V~3.6V | √ |

工作电流 | <1 mA | Converting maximum IVDD=IAFE+IADC : 700 μA Typ. IADC = 200 μA | √ |

电容检测范围 | 1 pF | 2.048 pF | √√ |

电容检测精度 | 1 fF | 1 fF | √ |

单次测量时间 | <20 ms | 400 μs | √√ |

参考文献:

[1] 沈易. 新型混合结构逐次逼近型CMOS模数转换器关键技术研究[D].西安电子科技大学,2019.

[2] 刘佳欣. 基于噪声整形的高能效模数转换器芯片关键技术研究[D].电子科技大学,2018.

[3] LI B, et al.A High-Sensitivity Signal Conditioning Interface for Capacitive Touch Key Using ΔΣ Modulation.

[4] 胡云峰.用于SAR ADC的高能效电容阵列DAC研究[D].广州:华南理工大学,2017.

[5] 王浩.低功耗电荷重分配式CMOS逐次逼近型模数转换器研究[D].西安:西安电子科技大学,2016.

[6] 胡云峰,李斌,吴朝晖.应用于SAR ADC的高能效电容阵列DAC[J].华南理工大学学报(自然科学版),2015,43(09):47-53+66.

[7] 梁宇华. 低功耗逐次逼近型CMOS模数转换器的研究[D].西安电子科技大学,2015.

附:赛后感想

1)报告、ppt写详细很重要,前两者是体现工作量的唯一方法。

2)拿奖拼的是需求指标,按照性能排名和奖项分配确定奖项。

3)想冲国奖,一开始就要将目标定到解决全部需求,不能想着附加题没什么人做。

4)赛前积累,类似国电赛,在比赛之前要有积累,p管n管输入的运放都要有,高增益的、高带宽的都要有,后仿必须解决。

5)团队合作,没有团队合作=止步初赛,团队=1个项目组。

6)在解决工程学术问题上,研究生和本科生差距较大,本科想拿奖全靠项目组积累和低保。

7)比赛能拿到很多,能得到更多,非科班想入门,全靠项目积累经验。

8)2021年:定目标(国赛、省赛)→找论文找结构,评估可行性(1个月以上),每周开会汇报,分享预研成果→原理图和版图同步进行。

*基金项目:2019年国家级大学生创新训练项目(201911078019);

获得“第四届全国大学生集成电路创新创业大赛-艾为杯“全国二等奖。

作者简介:麦伟健(1999—),男,主要从事模拟IC电路与人工智能交叉算法的学习。

(本文来源于《电子产品世界》2020年12月期)

评论