一种上电复位自关断电路

王依波(电子科技大学 电子科学与工程学院,四川 成都 610054)

本文引用地址:https://www.eepw.com.cn/article/201908/404228.htm摘 要:介绍了一种低功耗的上电复位电路(POR),针对以往上电复位电路的上电复位时间较短和功耗较高的问题,提出了一种新的上电复位自关断电路,最后在Cadence仿真环境中,给出了该电路在0.13 µm工艺下的仿真结果。结果表明该电路可适用于各种上电时间,并且功耗较低。

0 引言

上电复位电路通过检测电源电压的变化来控制芯片进入初始工作状态,当电源电压上升到正常工作电压之前,低电平复位的上电复位电路需要会产生一个低电平,使芯片处于复位状态,防止芯片非正常工作影响性能;在电源电压上升到正常的工作电压之后,上电复位电路就会维持一个高电平,确保芯片处在正常工作的状态。

由于上电复位电路的应用十分广泛,在不同的应用场景下对于电源上电的时间要求也不同,文献[1]所提出的上电复位电路是一种常见的结构,基于RC充电原理,该电路结构简单,功耗低,但是无法在电源电压上电较慢的情况下使用,并且抗干扰能力较低。而像文献[2]中提出的基于电平检测的上电复位电路,虽然能够满足较大范围的上电时间,但是结构复杂,通常包括带隙基准,比较器等模块,电路设计复杂且功耗高。

针对上述问题,本文提出了一种上电复位自关断电路,在不同的上电时间下都能正常工作,并且功耗极低。

1 上电复位自关断电路原理

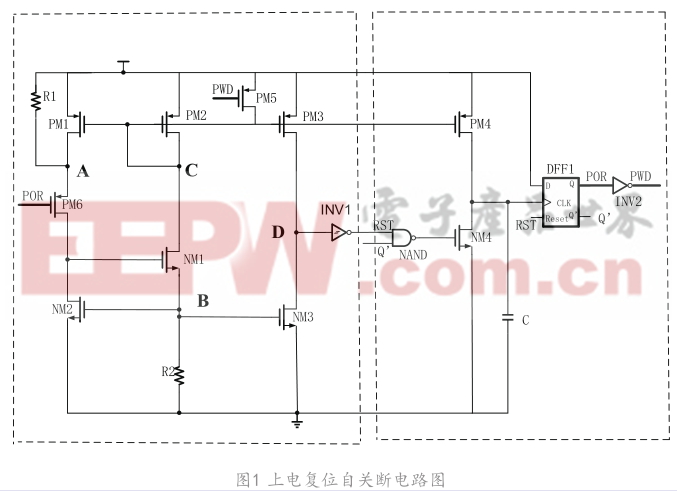

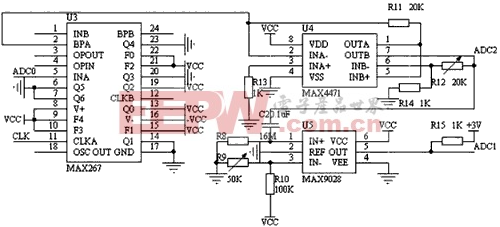

本文提出的上电复位自关断电路结构如图1所示,包括上电复位信号产生模块,信号锁存模块和电源关断模块。电路的具体实现如下:上电复位信号产生电路是基于MOS管的阈值电压对电源电压进行检测。R1电阻作为电路的自启动模块,防止上电复位模块进入死锁状态;MOS管PM1~PM3、NM1~NM3和电阻R2共同组成了电压检测电路。

假设PMOS管的阈值电压为V tp ,NMOS管的阈值电压为V tn 。当电源电压开始上电之前,输出的POR信号一直保持低电平状态,对芯片进行复位操作;开始上电后,在电源电压升到到V tn 之前,电路中除了节点A、C、D在通过PMOS管进行充电外,没有其他变化;当电源电压达到V tn 时,NM1导通,流经NM1的电流将节点B的点位拉低,该电流同时被PM1和PM3镜像,然后节点C的点位开始拉高到电源电压,并且跟随电源电压变化。当电源电压达到2V tn 时,NM2导通,然后节点B的电压随着电源电压升高而升高,假设节点B的电压变化为 ∆v ,则流经PM2的电流变化∆v/R2,该变化通过电流镜反映到PM3所在的支路。但是因为NM3的漏端电流变化相对于∆v是成平方率关系,所以当NM3的电流占主导时,节点D的电压会被快速拉到地。经过施密特反相器整形后,得到一个高电平。

流过NM2和NM3的电流如下:

流过PM1和PM3的电流如下:

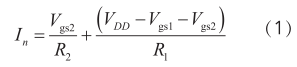

其中,V gs1 和V gs2 分别是NMOS管NM1和NM2的栅源电压,当电源电压逐渐升高到In >Ip时,节点D的点位保持为地,经过施密特反相器得到一个高电平,将此时的电源电压值定义为上电复位电压的阈值,用POR vt 表示。由公式(1)(2)可以得出

由于在该电路结构中NM2只工作在饱和区,所以

由上电复位信号产生电路所产生的信号,经过施密特反相器反向并整形,输出的上升沿 的阶跃信号用来做D触发器的复位信号,D触发器脱离复位状态后,RST信号和Q`信号经过与非门逻辑输出一个低电平将NM4关断,然后电容C开始充电,D触发器的时钟信号CLK变为高电平,Q输出端输出带上升沿高电平信号,并进行锁存,产生最终的上电复位信号POR。上电复位信号POR和经过反相器INV2后作为电源关断控制信号PWD用来将上电复位信号产生电路关断,减小整个电路的静态功耗。

2 电路仿真结果

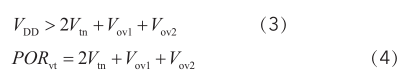

基于第1节的原理,在Cadence仿真环境中采用GSMC 0.13 µm CMOS工艺下将电路实现,并针对不同的电源上电时间进行功能仿真和功耗仿真。为了便于描述,选取典型的仿真结果如图2所示。由此可见,随着电源电压的逐渐升高,电路所产生的上电复位信号由低电平迅速升高为高电平,使芯片脱离复位状态。在POR信号稳定以后,在电源电压为1.2 V的情况下,整个电路的电流只有1.5 nA左右。

3 结论

随着芯片集成度的逐步提高,对于功耗的要求也越来越严格,从低功耗高和适用于多种应用环境的角度出发,本文提出了一种新的上电复位电路,在上电复位完成之后,将整个电路关断,达到低功耗的目的。该电路适用范围广,功耗低,可靠性强,可以适用于各种芯片的复位操作。

参考文献

[1] Suat U. Ay, et al. A nanowatt cascadable delay elementfor compact power-on-reset (POR) circuits[C].2009 52ndIEEE International Midwest Symposium on Circuits and Systems,Cancun,Mexico.2009:62-65.

[2] Lai X,Yu W,Li G, et al. A low quiescent current and resettime adjustable power-on reset circuit[C].InternationalConference on ASIC,Himeji,Japan.2015:559-562.

本文来源于科技期刊《电子产品世界》2019年第9期第61页,欢迎您写论文时引用,并注明出处。

评论