板载电源设计的一些规范总结

热插拔

本文引用地址:https://www.eepw.com.cn/article/201812/396198.htm1、热拔插系统必须使用电源缓启动设计

热拔插系统在单板插入瞬间,单板上的电容开始充电。因为电容两端的电压不能突变,会导致整个系统的电压瞬间跌落。同时因为电源阻抗很低,充电电流会非常大,快速的充电会对系统中的电容产生冲击,易导致钽电容失效。如果系统中采用保险丝进行过流保护, 瞬态电流有可能导致保险丝熔断, 而选择大电流的保险丝会使得在系统电流异常时可能不熔断,起不到保护作用。所以,在热拔插系统中电源必须采用缓启动设计,限制启动电流,避免瞬态电流过大对系统工作和器件可靠性产生影响。

LDO

1、在压差较大或者电流较大的降压电源设计中,建议采用开关电源,避免使用 LDO

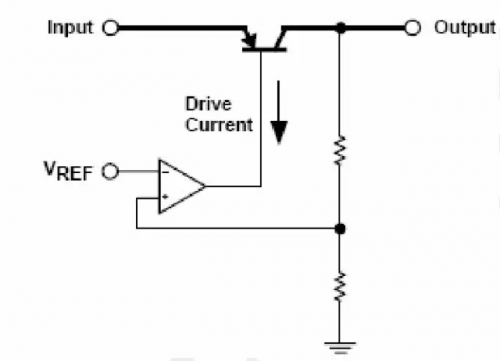

采用线性电源(包括 LDO)可以得到较低的噪声,而且因为使用简单,成本低,所以在单板上应用较多。FPGA 内核电源、某些电路板上射频时钟部分的电源等都使用线性电源从更高电压的电源上调整得到。线性电源的基本原理如图所示。输出电压经过采样后和参考电源(由晶体管带隙参考源或者

齐纳二极管提供)进行减法运算,差值经过放大后控制推动管上的电压降

V dropout =V output -V input , 使得当 V input 变化或者负载电流变化导致

V output 变化时,通过 V dropout 的变化保证 V output 的稳定。

由图中可见,负载电流全部流过调整管,而输入电压和输出电压之间的差异全部都加在调整管上。调整管上耗散的功率为 V dropout *I。当电压差较大时,或者负载电流较大时,稳压器将承受较大的功率耗散。

LDO必须计算热耗并满足降额规范

另外,输入的电源提供的功率为 V input *I,即采用线性电源时电源功率的计算不能使用负载电压和电流的乘积计算,必须采用线性电源输入电压和负载电流的乘积计算采用线性电源时电源功率的计算不能使用负载电压和电流的乘积计算,必须采用线性电源输入电压和负载电流的乘积计算。必须经过计算和热仿真确保系统的正常工作。

例如采用 1 只 TO-263 封装的 LDO 将电压从 3.3V 降到 1.2V,负载电流为 1.5A,负载上耗散的功率为 1.8W。此时 LDO 上承担了 2.1V 压降,耗散的功率 3.15W,3.3V 电源提供的功率为 4.95W!

封装的热阻约为 40℃/W,则如果不采取任何散热措施,则温升能够达到约 120℃。对 LDO 必须通过热仿真确定合适的散热措施,并且在 3.3V 电源在预算中必须能够提供 1.5A 的电流(或者 5W 以上的功率) ,保证系统的工作正常。 (对于线性电源的原理参见参考文档《电源是怎样炼成的》PPT教程 。 )

采用开关电源能够达到很高的效率,对大电流及大压差的场合,推荐采用开关电源进行转换。如果电路对纹波要求较高, 可以采用开关电源和线性电源串联使用的方法, 采用线性电源对开关电源的噪声进行抑制。

2、LDO 输出端滤波电容选取时注意参照手册要求的最小电容、电容的 ESR/ESL 等要求确保电路稳定。推荐采用多个等值电容并联的方式,增加可靠性以及提高性能

LDO 输出电容为负载的变化提供瞬态电流,同时因为输出电容处于电压反馈调节回路之中,在部分 LDO 中,对该电容容量有要求以确保调节环路稳定。该电容容量不满足要求,LDO 可能发生振荡导致输出电压存在较大纹波。

多个电容并联,以及对大容量电解电容并联小容量的陶瓷电容,有利于减少 ESR 和 ESL,提高电路的高频性能,但是对于某些线性稳压电源,输出端电容的 ESR 太低,也可能会诱发环路稳定裕量下降甚至环路不稳定。

滤波电容

1、 电源滤波可采用 RC 、LC 、π 型滤波。电源滤波建议优选磁珠,然后才是电感。同时电阻、电感和磁珠必须考虑其电阻产生的压降

对电源要求较高的场合以及需要将噪声隔离在局部区域的场合, 可以采用无源滤波电路。 在采用无源滤波电路时,推荐采用磁珠进行滤波。

磁珠和电感的主要区别是,电感的Q值较高,而磁珠在高频情况下呈阻性,不易发生谐振等现象。

电感加工精度较高,而磁珠加工精度相对较低,成本也较便宜。在选择滤波器件时,优选磁珠。选择电阻和电容构成无谐振的一阶 RC 低通滤波器,但是该电路只能应用于电流很小的情况。负载电流将在电阻上形成压降,导致负载电压跌落。无论是采用何种滤波器,都需要考虑负载电流在电感、磁珠或者电阻上的压降,确认滤波后的电压能够满足后级电路工作的要求。例如在某单板锁相环路设计中采用了一阶 RC 滤波器,滤波电阻选择12 欧姆。锁相环中 VCXO 的工作电流约为 30mA,在滤波电阻上产生 300mV 的压降,额定电压 3.3V的 VCXO 实际工作电压只有不到 3V,易发生停振等现象。在某光口子卡上,发生过某型号光模块当光纤插上时 SD(光检测)信号上升缓慢,不能正确反映实际情况的问题。经过检查发现滤波电感的直流电阻约为 3 欧姆, 光模块工作电流约为 100mA, 电感上的压降导致光模块的工作电压只有约 2.9V 左右,在该型号光模块上会出现 SD 上升缓慢的故障。

另外,对于滤波电路,应保证电感、磁珠或者电阻后的电容网络能够保证关心的所有频率下,都能够保证低阻抗。必要时应采用多种容量的电容并联,并局部铺铜的方式达到目标阻抗。 (参见时钟驱动芯片滤波电路设计部分) 。在某单板上,采用了磁珠和 0.1u 电容为时钟驱动芯片提供滤波。经过测试,时钟驱动芯片管脚上的纹波高达 1V 以上。采用多电容并联的方式可以有效地为时钟芯片提供去耦。

2、 大容量电容应并联小容量陶瓷贴片电容使用

大容量电容一般为电解电容,其体积较大,引脚较长,经常为卷绕式结构(钽电容为烧结的碳粉和二氧化锰) 。这些电容的等效串联电感较大,导致这些电容的高频特性较差,谐振频率大约在几百 KHz到几 MHz 之间(参见 Sanyo 公司 OSCON 器件手册和 AVX 公司钽电容器件手册) 。小容量的陶瓷贴片电容具有低的 ESL 和良好的频率特性,其谐振点一般能够到达数十至数百 MHz(参见参考文献《High-speed Digital Design》以及 AVX 等公司陶瓷电容器件手册) ,可以用于给高频信号提供低阻抗的回流路径,滤除信号上的高频干扰成分。因此,在应用大容量电容(电解电容)时,应在电容上并联小容量瓷片电容使用。

3、输入电容

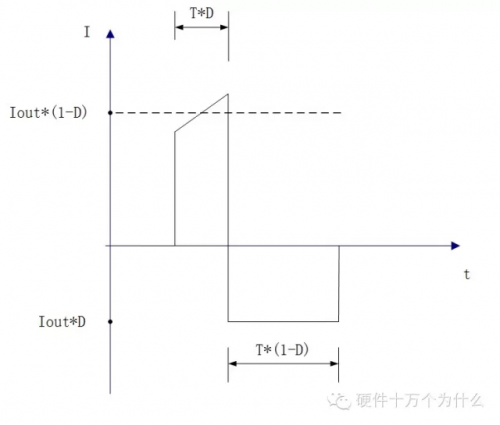

计算输入电容的纹波电流,这个推导的过程,利用到积分公式。通过分析和推导,可以对电路的工作原理有比较透彻的理解。

如果考虑输出纹波电流。那么电容上的纹波电流的波形为:

评论