AVR单片机IO口结构和上拉和下拉电阻的作用

为搞清IO结构,首先看看上拉和下拉电阻的作用。

本文引用地址:https://www.eepw.com.cn/article/201811/394646.htm一、上拉电阻

上拉就是将不确定的信号通过一个电阻钳位在高电平!电阻同时起限流作用!下拉同理!

上拉电阻是用来解决总线驱动能力不足时提供电流的。一般说法是拉电流,下拉电阻是用来吸收电流。

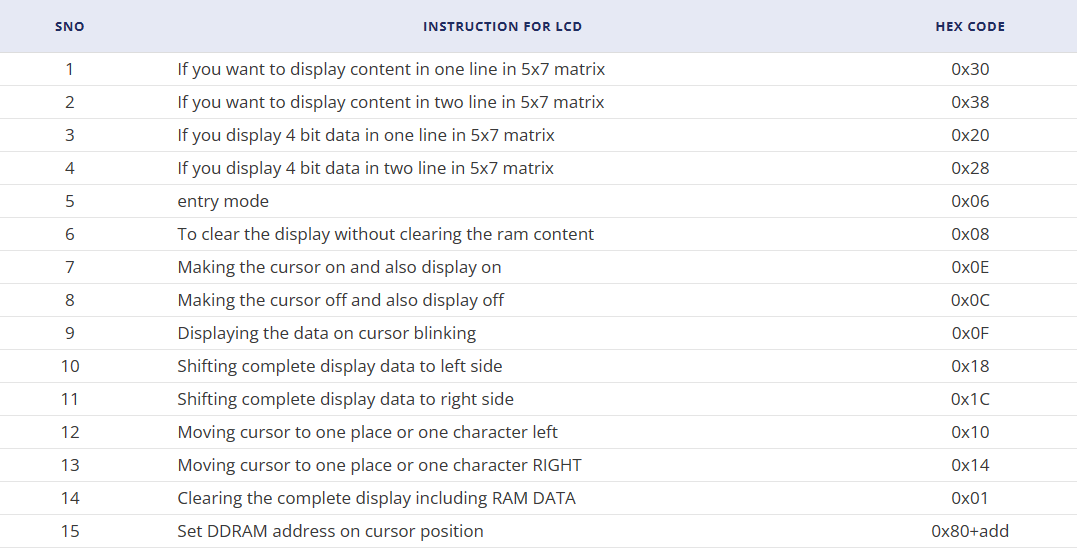

1、在用TTL电路驱动CMOS电路时,若TTL的高电平低于CMOS要求的高电平的门限值(1,TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平 是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是 0.4V。 2,CMOS电平: 1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。),此时需用上拉电阻来提升输出高电平的电压值 。

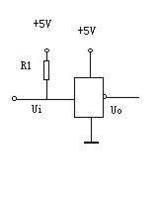

2、OC门必须外加上拉电阻,才能使用。(OC门:三极管的叫集电极开路,场效应管的叫漏极开路,简称开漏输出。具备"线与"能力,有0得0。 )

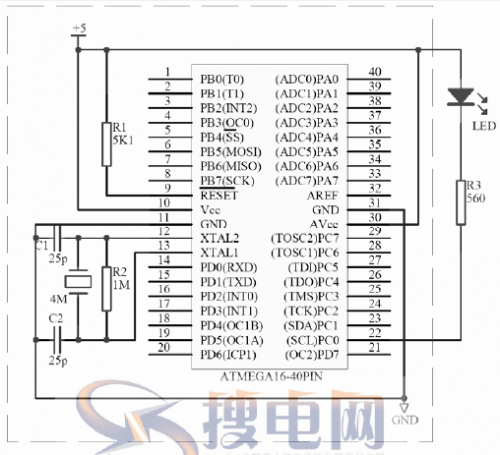

3、为加大输出管脚的驱动能力,单片机的引脚常接入上拉电阻,(AVR单片机可配置是否接上拉,51单片机P1 P2 P3均带上拉,P0口不带,所以用P0口做按键,液晶等应用时要自己加上上拉电阻,否则无法使用切记)

4、CMOS芯片上为防止静电破坏,不用的管脚不能悬空,需要接上拉电阻降低输入阻抗,提供泄荷通路。

5、提高总线的搞电磁干扰能力,悬空就容易就电磁干扰。

二、上拉电阻阻值的选择

1、为节约功耗或使灌电流足够大,阻值要大,电流小。

2、为确保足够的驱动电流,阻值要小,电流大。

3、对于高速电路,过大的上拉电阻可能导致边沿变得平缓。

基于以上三点,一般选取上拉阻值为1K-10K。

三、上拉阻值的计算

OC门输出高电平时是一个高阻态,其上拉电流要由上拉电阻来提供,设输入端每端口不大于100uA,设输出口驱动电流约500uA,标准工作电压是5V,输入口的高低电平门限为0.8V(低于此值为低电平);2V(高电平门限值)。

选上拉电阻时:

500uA x 8.4K= 4.2即选大于8.4K时输出端能下拉至0.8V以下,此为最小阻值,再小就拉不下来了。如果输出口驱动电流较大,则阻值可减小,保证下拉时能低于0.8V即可。

当输出高电平时,忽略管子的漏电流,两输入口需200uA

200uA x15K=3V即上拉电阻压降为3V,输出口可达到2V,此阻值为最大阻值,再大就拉不到2V了。选10K可用。COMS门的可参考74HC系列

设计时管子的漏电流不可忽略,IO口实际电流在不同电平下也是不同的,上述仅仅是原理,一句话概括为:输出高电平时要喂饱后面的输入口,输出低电平不要把输出口喂撑了(否则多余的电流喂给了级联的输入口,高于低电平门限值就不可靠了)

在数字电路中不用的输入脚都要接固定电平,通过1k电阻接高电平或接地。

四、51型单片机IO口

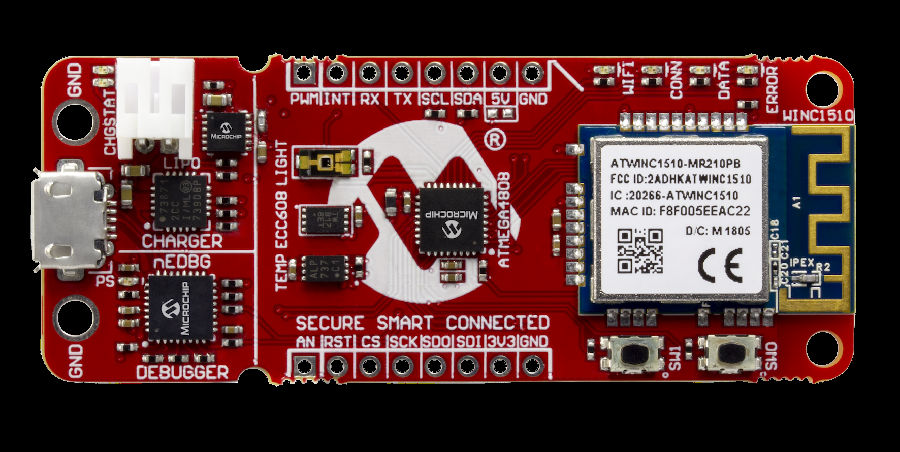

AVR的IO是真正双向IO结构,由于大部分网友都是从标准51转过来的,受标准51的准双向IO和布尔操作概念影响,没能掌握AVR的IO操作,所以有必要撰文说明一下

其实采用真正双向IO结构的新型MCU很多,常用的有 增强型51,PIC,AVR等,

先简单的回顾一下标准51的准双向IO结构

这种准双向IO结构的特点是

1 输出结构类似 OC门,输出低电平时,内部NMOS导通,驱动能力较强(800uA);输出高电平靠内部上拉电阻,驱动能力弱(60uA)。

2永远有内部电阻上拉(P0口除外),高电平输出电流能力很弱,所以即使IO口长时间短路到地也不会损坏IO口

(同理,IO口低电平输出能力较强,作低电平输出时不能长时间短路到VCC)

3作输出时,输出低电平可以推动LED(也是很弱的),输出高电平通常需要外接缓冲电路(所以LED多为共阳接法)

评论