逻辑门电路的传播速度

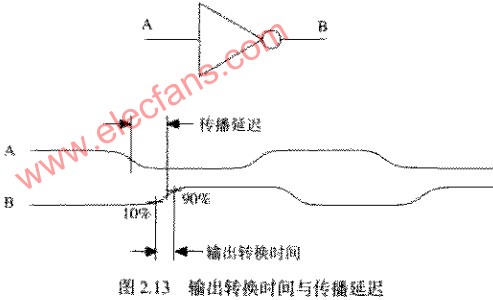

理论上的数字逻辑设计重点关注的是逻辑门电路的传播延迟。相比之下,高频电子工程中的许多实际的问题通常只取决于一个更细微的指标:最小输出转换时间。图2.13举例说明了这一差别。

本文引用地址:https://www.eepw.com.cn/article/201809/388876.htm

较快的转换时间会导致返回电流,串扰和振铃等等与传播延迟无关的问题成倍地增加。如果逻辑产品系列的最小转换时间比传播延迟快得多,那么系统设计时会面临不必要的麻烦,因为相应器件封装,电路板布局设计和连接器都必须适应器件的快速转换时间,而小的传播延迟只有利于逻辑时序。假设有两种逻辑产品系列具有相同的最大传播延迟参数值。其中输出转换时间最慢的将会更便宜,而且更好用。

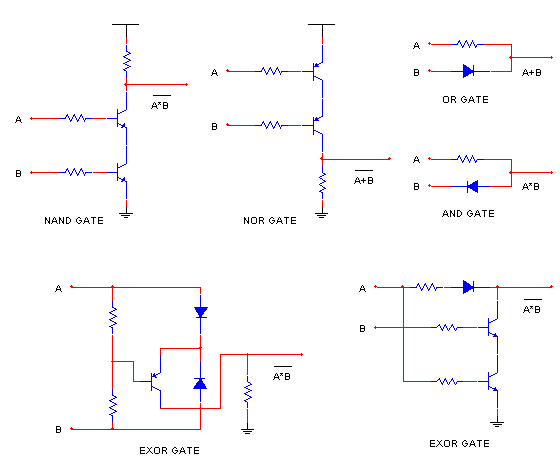

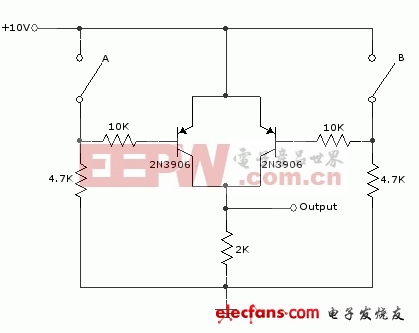

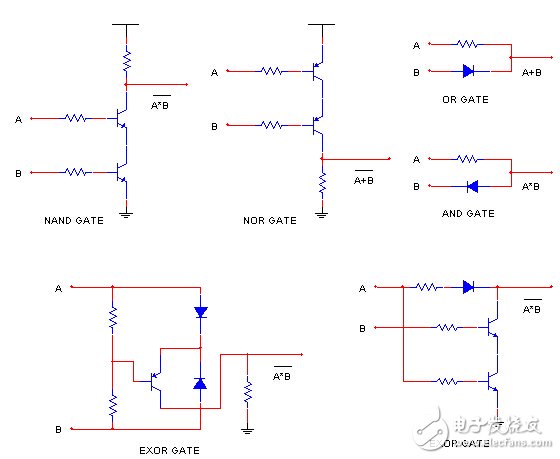

许多逻辑产品系列有多种速度-功率组合可以选用。TTL系列包括LS和S等种类。所有CMOS系列都表现出引人注目的功率-速度关系:从而使任何CMOS系统的功耗与它的时钟速率成正比。ECL系列产品可以在近乎两倍于MECL 10KH系列的速度下工作,但是也消耗了两倍的功率。

制商更强调速度和功率的折衷,因为这样可以使数据手册看上去更体面。他们经常不标出器件最小转换时间。这一个参数非常难于控制,除非制造过程中嵌入特殊的电路以减缓输出转换的速率。

这种限定转换时间的电路已经逐渐地开始进入一些逻辑系列产品,自从1971年MECL 10K系列产品出现以来,所有ECL系列都已经内置了边沿减缓的电路。出现于1990年的FCT系列产品是第一个内置了边沿减缓机制的CMOS电路。从那以后,其他的制造商也采用了这种方法。

这快的转换时间分别通过两种特定方式导致问题的产生:由电压突变产生的影响和由电流突变产生的影响。

评论