Achronix与Mentor共同打造以高等级逻辑综合(HLS)与FPGA技术的连接推动5G应用新发展

FPGA技术因为具有其并行执行、运算性能高、功耗低、可重配置以及相比ASIC开发周期短等优点,目前在各个领域中都有广泛的应用。但是随着FPGA器件资源容量的不断提高,逻辑设计的规模也越来越大,传统的逻辑代码设计变得十分复杂,开发周期也愈发漫长。由此,在2018年8月,基于现场可编程门阵列(FPGA)的硬件加速器件和嵌入式FPGA(eFPGA)半导体知识产权(IP)领导性企业Achronix半导体公司(Achronix Semiconductor Corporation)日前宣布:该公司FPGA技术系列产品已获得其合作伙伴、西门子旗下的Mentor公司的支持,将持续为其提供优化的高等级逻辑综合(HLS)流程。 HLS的引入,对于提高FPGA开发效率,提高算法的收敛、迭代速度,有着非常明显的效果。

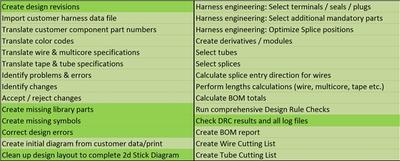

本文引用地址:https://www.eepw.com.cn/article/201808/391383.htm该集成开发环境使设计人员能够使用Mentor的Catapult®HLS和Achronix的ACE设计工具快速的用C ++实现FPGA设计。此项合作首先已可用于5G无线应用,以减少整体开发工作并提高结果的质量(QoR),它适用于任何面向Achronix技术的设计。

“Mentor功能强大的Catapult工具和Achronix的嵌入式FPGA技术结合在一起,可为那些其SoC设计需要高性能FPGA技术的公司提供了真正独到的价值组合,而这些SoC可以使用经过验证的、基于C语言的设计流程来进行配置,”Achronix负责市场营销的副总裁Steve Mensor评论道。 “这种组合型解决方案很好地证明了Mentor和Achronix工程团队之间的紧密合作关系。 我们首先面向的目标应用是5G无线,但是在其他许多需要最快开发时间的细分市场应用中,这项整体解决方案的独特功能都有其价值。“

“我们高兴地欢迎Achronix加入Mentor OpenDoor计划,并乐于成为Achronix合作伙伴计划的活跃成员。 这种开放且相互配合的合作伙伴关系具有非常高的战略意义,并已经被证明是有益于我们的共同客户,“Mentor公司Calypto Systems业务部市场营销总监Ellie Burns说到。 “Achronix eFPGA提供了极强大的功能,它能够适应一款具有现场可编程能力的SoC的后期变化和新要求。 再加上Catapult HLS和C ++的验证速度,芯片设计人员现在可以在几天而不是几周或几个月内轻松地从算法更改转化为全新的低功耗、高性能硬件。“

将Catapult添加到Achronix设计流程

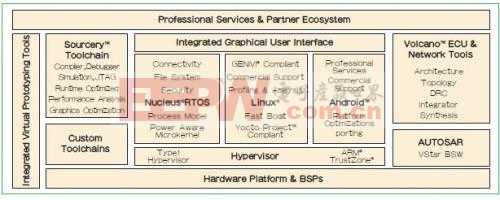

将Catapult HLS添加到Speedcore嵌入式FPGA技术设计流程,可使设计人员能够在IP开发的后期阶段进行算法更改,并优化算法和数字微架构。 集成化的验证环境支持为已生成寄存器传输级(RTL)的代码去重用软件测试,从而将对专用RTL测试台的需求减少80%以上。

Achronix ACE设计工具支持Catapult的RTL构造和原生语句。 目前,用于Achronix的Speedcore eFPGA产品及其Speedster独立FPGA芯片的Achronix逻辑库已被集成到流程中。

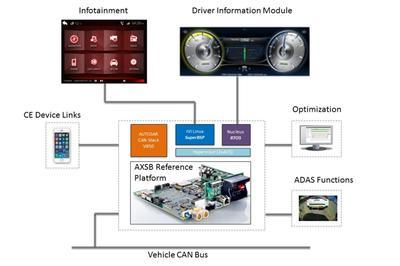

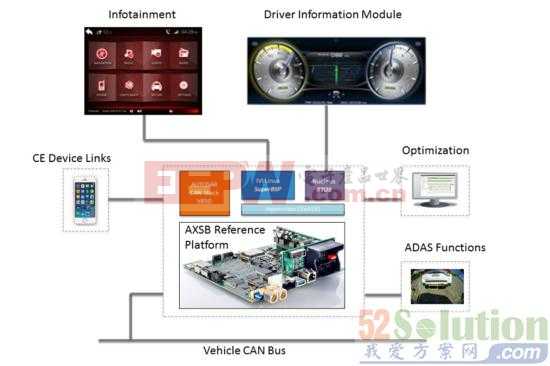

Achronix的高性能和高密度FPGA技术可用于数据中心计算、网络和存储中的各种硬件加速应用,5G无线基础设施及网络加速,先进驾驶员辅助系统(ADAS)和自动驾驶汽车。

Achronix经过Mentor公司的高等级逻辑综合(HLS)流程支持后不断优化的FPGA技术,和之前相比在性能开发、功能实现等方面都有着很大的进步,并且能使芯片设计的过程中低功耗和高性能,让更多的研发人员,甚至算法设计人员,可以更加容易的使用FPGA完成设计。也更能发挥出FPGA并行的优势,并且此项合作也应用到5G无线应用中,必将对今后5G技术产生重大影响。

评论