基于40 nm CMOS工艺的高速SAR ADC的设计

作者 魏祎 电子科技大学 微电子与固体电子学院(四川 成都 610054)

本文引用地址:https://www.eepw.com.cn/article/201802/376171.htm魏祎(1993-),男,硕士生,研究方向:大规模集成电路与系统。

摘要:基于40 nm CMOS工艺,设计了一种高速逐次逼近型模数转换器。本设计采用了非二进制冗余DAC技术来缓解ADC对建立时间和建立精度的要求,来提高ADC量化的准确性;采用带有预放大级的高速比较器来提高比较器的精度,同时减小后级Latch的回踢噪声,采用了两级Latch来进一步提高比较器的速度;采用基于锁存器的锁存单元来提高SAR逻辑控制电路的速度,并且采用了异步时序控制,不需要外部时钟,有利于提高SAR ADC的速度,并降低了设计的复杂度。设计的SAR ADC在160 MHz的采样频率下,在不同输入信号频率下均可以实现12 bit的量化精度,SFDR均在83 dB以上。

0 引言

随着智能设备的普及和通信技术的不断发展,消费者对智能互联的需求变得越来越迫切。这就要求通信网络要有更快的数据速率。而更高的数据传输速率就要求更大的带宽。因此通讯接收机就需要更快的数据转换器,将模拟的无线通信信号转换为数字信号,供DSP芯片进行处理。模数转换器(Analog-to-Digital Converter,ADC)作为连接模拟系统和数字信号处理系统的桥梁起着关键的作用。

在同样精度与速度要求下,与快闪型、折叠内插型、流水线型等ADC相比,SAR ADC结构简单、功耗低、易于集成等特点,因此得到了广泛的应用[1-2]。

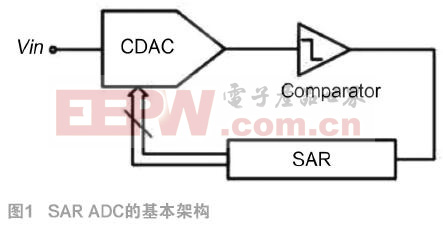

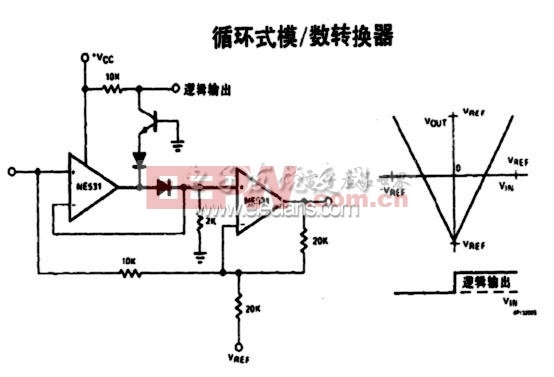

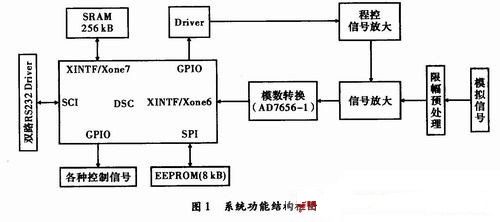

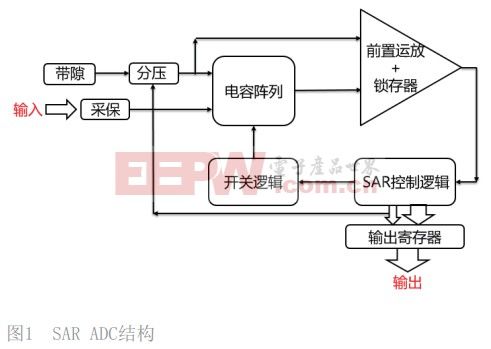

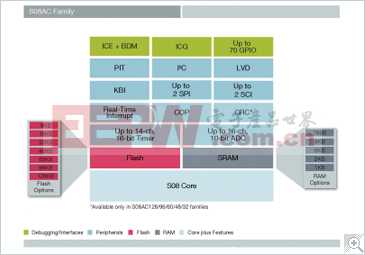

常见的SAR ADC主要由自举采样开关、DAC、比较器和SAR逻辑电路组成,其基本架构如图1所示。其中DAC主要采用电容阵列构成的CDAC。一个N位的SAR ADC的工作原理是采用二进制搜索算法确定输入信号所在的量化区间。首先,输入信号通过采样开关存储在DAC中;然后通过比较器对输入信号和DAC产生的参考电压进行比较,将比较结果输出到SAR逻辑电路,SAR逻辑控制电路根据比较结果去控制DAC中的开关切换,使DAC进一步产生逼近输入信号的参考电压;最后当每一位都比较完成后,DAC的输出电压将收敛到与输入信号相差不超过1/2 LSB(1LSB=VFS/2N)的范围,比较器的每一位输出码组成最终的N位输出码。

本设计采用了非2进制冗余DAC技术、静态锁存比较器、基于锁存器的SAR逻辑控制电路,在CMOS工艺下实现了12 bit的高速SAR ADC的设计。

1 DAC的设计

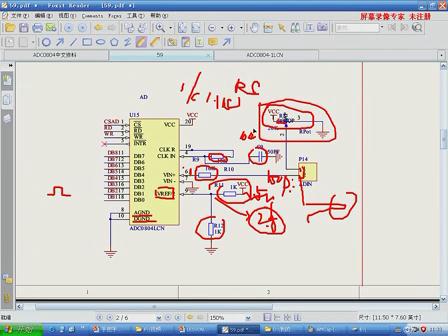

DAC为非二进制传统电容阵列,阵列基底小于2。由于DAC阵列总电容很小,为抑制电荷注入,采用下极板采样方式。为保证12 bit动态范围,选取定基底radix=1.877, 以13位电容阵列的方式来实现12 bit的SAR ADC。电路结构如图2所示。

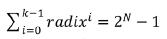

非二进制冗余DAC技术缓解了ADC对建立时间和建立精度的要求[3]。在传统的二进制电容阵列里,电容的值都是以2为基底,ADC的转换编码和输入信号之间是线性映射的关系。如果将电容阵列的基底设置成小于2,则转换编码和输入信号之间不再是线性映射,这种非线性映射恰恰为DAC的建立提供了冗余,可一定程度放宽DAC的建立精度,同时建立时间也大大缩短。一个N位的非二进制SAR ADC,假设以radix作为电容阵列的基底,由于radix <2,继续使用N位电容进行量化将导致ADC不足以提供N位精度的动态范围,假设使用k位电容进行量化,则需满足

(1)

(1)

根据式(1),如果利用13位电容来实现12位ADC,则基底至少为1.8772。冗余发生在量化编码为0111…111和1000…000之间,只要输入信号在此冗余范围,不管高位量化值是0还是1,最终都能被准确地表示,换言之,只要DAC能够建立到对应的冗余范围内,最终就能正确完成量化[4]。

2 SRA ADC的工作原理

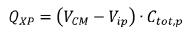

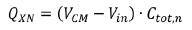

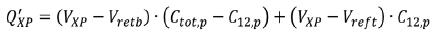

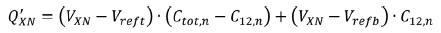

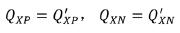

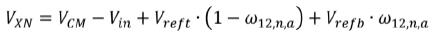

在采样阶段,采用下极板采样的方式,DAC差分输出端接共模电压VCM,所有电容下极板分别接输入信号Vip和Vin,此时差分DAC输出端的电荷:

(2)

(2)

(3)

(3)

为了减小采样开关的非理想效应,先将VCM开关断开,再将自举采样开关断开,完成对输入信号的采样。采样完成后即进行第一次量化。以差分DAC的P端为例,首先将上极板从共模电平VCM断开,然后将除MSB电容外所有电容的下极板切换到Vrefb,MSB电容下极板切换到Vrefb,DAC建立完成即进行第一次比较,此时,上极板电荷:

(4)

(4)

互补DAC的N端的切换方式和P端相反,其切换后上极板电荷:

(5)

(5)

根据上极板电荷守恒:

(6)

(6)

可得第一次比较时:

(7)

(7)

(8)

(8)

其中定义模拟权重:

假设第一次比较结果D12=1,即VXP<vxn,则

3 比较器的设计

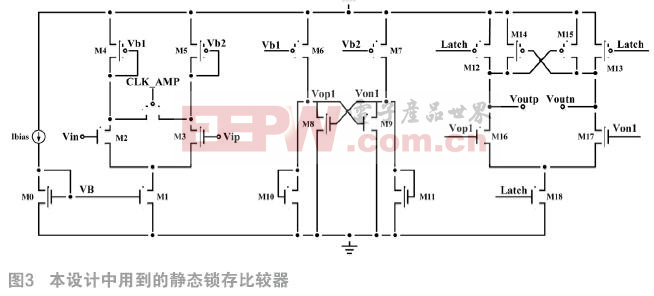

本设计中的比较器采用静态锁存比较器加一级动态锁存器的结构,其结构如图3所示。静态锁存比较器采用的再生单元是A类交叉耦合对[5],比较器的工作电流决定了其转换速度。第一级为预放大级,对输入信号进行放大,输出电流通过镜像注入再生单元,差分输入对管的漏端与再生节点之间存在隔离,回踢噪声较小。比较器采用异步时序控制,当比较器产生比较结果后对比较器进行复位操作。

本设计中SAR ADC的输入信号为800 mVpp,一个LSB为195 mV。考虑到Latch的比较速度与输入信号的关系,预放大级的增益设计为20 dB。在实际工作时,比较器的工作速度很快,因此预放大级需要有足够的带宽。本设计中预放大级的-3 dB带宽为1.8 GHz。

4 SAR逻辑控制电路的设计

采用同步结构的SAR逻辑需要额外的控制时钟。对于一个N位同步SAR ADC而言,量化过程需要N个时钟周期,采样过程需要一个到多个时钟周期,假设为一个时钟周期,则ADC的采样率为外部时钟频率的1/(N+1),由于采样时钟必须要保证精度且由外部时钟分频得到[6-7],因此在同步设计里首先要保证(N+1)倍于采样率的外部时钟的精度,不但相当困难,而且十分不经济。

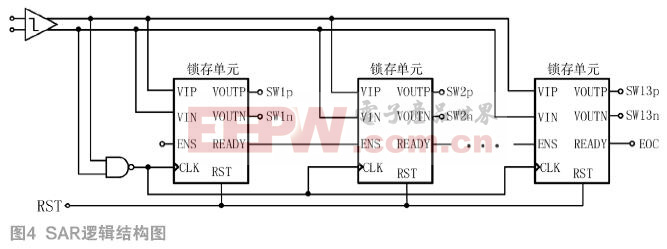

因此本设计采用异步时序控制的SAR逻辑。SAR逻辑控制电路由13个锁存单元及对应的DAC开关控制信号产生电路组成,如图4所示,本设计共有13个锁存单元。

VIN和VIP接收比较器的输出,ENS接收来自前一级的使能信号,CLK为锁存单元的控制时钟,控制内部的锁存器,RST为复位信号,锁存单元对比较器的结果进行锁存后,经过逻辑电路产生VOUTP和VOUTN作为DAC开关的控制信号,来控制电容下极板的切换。其工作流程为,当比较器产生比较结果后,将比较结果输出到SAR单元,同时将比较结果通过与非门来产生锁存单元的控制时钟,控制锁存单元对比较器的输出结果进行锁存,锁存完成后随即产生一个使能信号,开启下一级锁存单元,等待下一次比较器的结果。当最后一级锁存单元锁存比较器结果后,产生的READY信号作为最终量化数据并行输出的控制信号,并用于产生SAR逻辑控制电路的复位信号,同时将DAC的电容上极板接到VCM,等待下一个采样周期的到来。

5 SAR ADC仿真结果

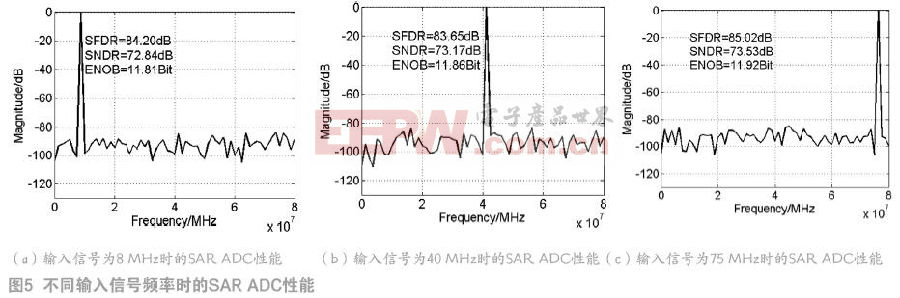

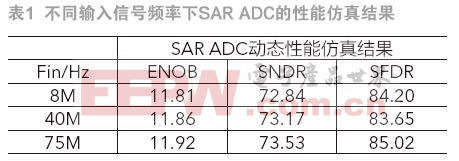

在采样频率Fs=160 MHz时,在不同输入信号频率下对SAR ADC进行仿真。输入信号为差分的正弦波,差分摆幅为800 mVpp,参考电压Vreft=800 mV,Vrefb=400 mV。通过Matlab对ADC的输出数据进行FFT处理后,得到SAR ADC在不同输入信号频率下的动态性能如表1所示。

SAR ADC在不同输入信号频率时的性能仿真结果统计如表1所示。

由仿真结果可以看出,本ADC的设计实现在160MHz的采样频率下能够完成13次量化,并保证了12位的量化精度。

6 结论

本设计采用了非二进制冗余DAC技术来缓解ADC对建立时间和精度的要求;采用带有预放大级的高速比较器来提高比较器的精度,并减小后级Latch的回踢噪声;SAR逻辑控制电路采用基于锁存器的锁存单元来提高SAR的速度,并且采用了异步时序控制,不需要外部时钟,有利于提高SAR ADC的速度,并降低了设计的复杂度。

经过仿真验证,本文设计的SAR ADC在160 MHz的采样频率下,在不同输入信号频率下均可以实现12 bit的量化精度,SFDR均在83 dB以上。

参考文献:

[1]Y. Chai, J. T. Wu. A CMOS 5.37-mW 10-bit 200-MS/s dual-path pipelined ADC[J]. IEEE Journal of Solid-State Circuits, 2012, 47(12): 2905-2915

[2]Y. Zhu, C. H. Chan, S. W. Sin, et al.. A 34 f J 10b 500 MS/s partial-interleaving pipelined SAR ADC[C]. Symposium on VLSI Circuits, Honolulu, 2012, 90-91

[3]杜翎.基于非二进制量化算法的逐次逼近模数转换器的设计[D].电子科技大学,2016.

[4]王伟.分辨率可配置型高速SAR ADC的研究与设计[D].电子科技大学,2016.

[5]C. C. Liu, C. H. Kuo, Y. Z. Lin. A 10 bit 320MS/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2015, 50(11): 2645-2654

[6]L. Du, S. Wu, M. Jiang, et al.. A 10-bit 100MS/s subrange SAR ADC with time-domain quantization[C]. International Symposium on Circuits and Systems, Melbourne VIC, 2014, 301-304

[7]Y. Zhu, C. H. Chan, S. W. Sin, et al.. A 34 f J 10b 500 MS/s partial-interleaving pipelined SAR

ADC[C]. Symposium on VLSI Circuits, Honolulu, 2012, 90-91

本文来源于《电子产品世界》2018年第3期第61页,欢迎您写论文时引用,并注明出处。

评论