GPIO内部结构、工作原理及相关寄存器详解(以STM32为例)

1. STM32实物图:

本文引用地址:https://www.eepw.com.cn/article/201801/374607.htm

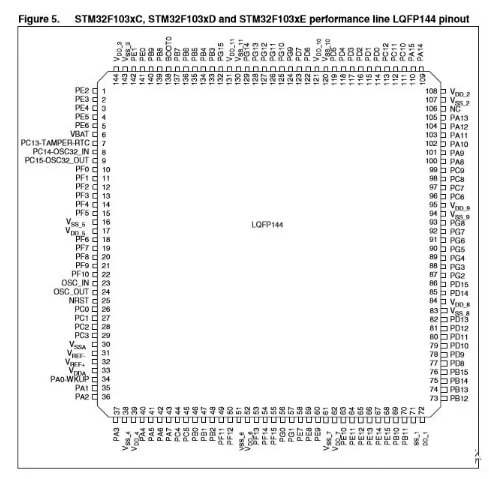

2. STM32引脚分布图:

STM32F103ZET6:共144个引脚,7组IO口,每组16个IO口

7*16=112个IO口(这7组IO口分别为GPIOA,GPIOB…GPIOG)

例如:PGIOA包含PA0,PA1,PA2…PA15,每组16个IO口

二,IO口的基本结构和工作方式

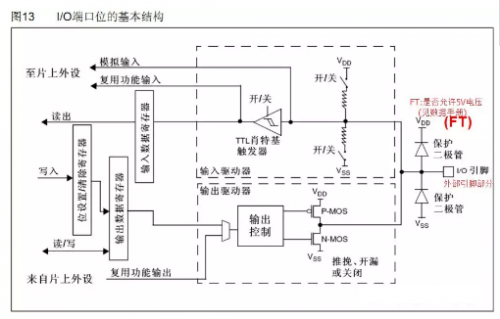

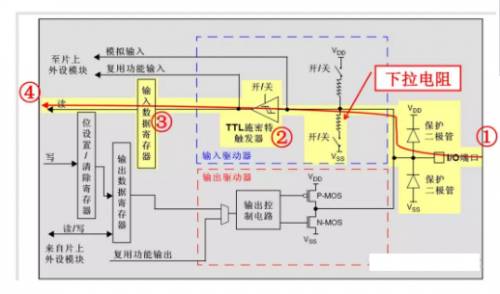

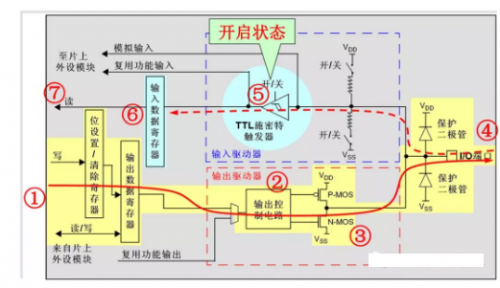

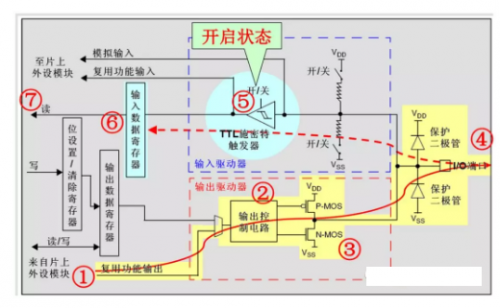

1. STM32F1系列IO口的基本结构()IO口内部电路结构)

右侧I/O引脚部分为芯片暴露在外部的引脚

每个引脚在数据手册都有说明是否支持(识别))5V电压

三,PGIO的8种工作方式

4种输入模式

输入浮空

输入上拉

输入下拉

模拟输入

4种输出模式

开漏输出

开漏复用功能

推挽输出

推挽复用功能

可配置3种最大翻转速度

2MHz

10MHz

50MHz

四,八种工作方式讲解

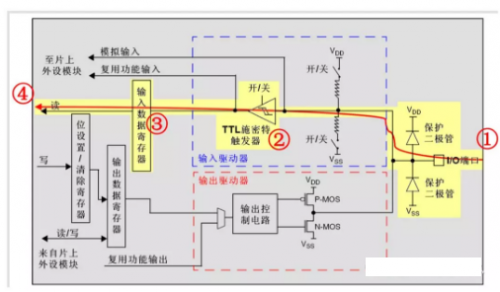

1,GPIO输入工作模式1-输入浮空模式

1)外部通过IO口输入电平,外部电平通过上下拉部分(浮空模式下都关闭,既无上拉也无下拉电阻)

2)传输到施密特触发器(此时施密特触发器为打开状态)

3)继续传输到输入数据寄存器IDR

4)CPU通过读输入数据寄存器IDR实现读取外部输入电平值

在输入浮空模式下可以读取外部输入电平

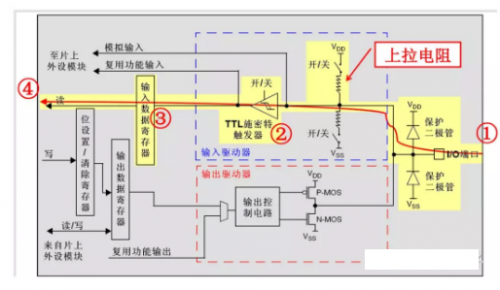

2,GPIO输入工作模式2-输入上拉模式

和输入浮空模式相比较,不同之处在于内部有一个上拉电阻连接到VDD(输入上拉模式下,上拉电阻开关接通,阻值约30-50K)

外部输入通过上拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取

3,GPIO输入工作模式3-输入下拉模式

和输入浮空模式相比较,不同之处在于内部有一个下拉电阻连接到VSS(输入下拉模式下,下拉电阻开关接通,阻值约30-50K)

外部输入通过下拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取

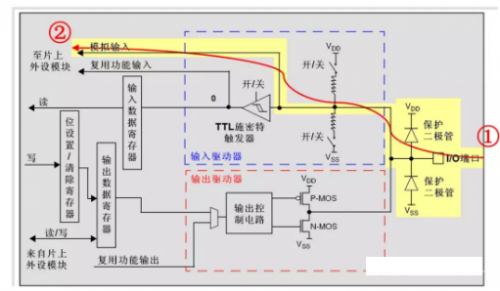

4,GPIO输入工作模式4-输入模拟模式

上拉和下拉部分均为关闭状态(AD转换-模拟量转换为数字量)

施密特触发器为截止状态

通过模拟输入通道输入到CPU

IO口外部电压为模拟量(电压形式非电平形式),作为模拟输入范围一般为0~3.3V

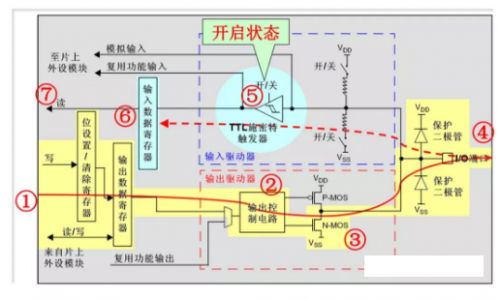

5,GPIO输出工作模式1-开漏输出模式

1,CPU写入位设置/清楚寄存器BSRR,映射到输出数据寄存器ODR

2,联通到输出控制电路(也就是ODR的电平)

3,ODR电平通过输出控制电路进入N-MOS管

-ODR输出1:

N-MOS截止,IO端口电平不会由ODR输出决定,而由外部上拉/下拉决定

在输出状态下,输出的电平可以被读取,数据存入输入数据寄存器,由CPU读取,实现CPU读取输出电平

所以,当N-MOS截止时,如果读取到输出电平为1,不一定是我们输出的1,有可能是外部上拉产生的1

-ODR输出0:

N-MOS开启,IO端口电平被N-MOS管拉倒VSS,使IO输出低电平

此时输出的低电平同样可以被CPU读取到

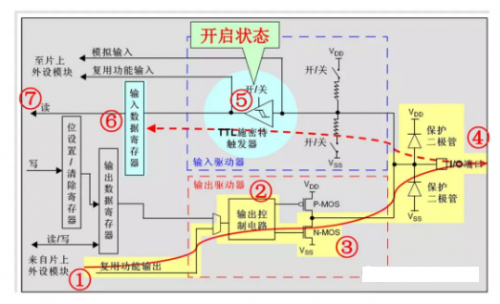

6,GPIO输出工作模式2-开漏复用输出模式

与开漏输出模式唯一的区别在于输出控制电路之前电平的来源

开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的

开漏推挽输出模式的输出电平是由复用功能外设输出决定的

其他与开漏输出模式相似:

控制电路输出为1:N-MOS截止,IO口电平由外部上拉/下拉决定

控制电路输出为0:N-MOS开启,IO口输出低电平

7,GPIO输出工作模式3-推挽输出模式

与开漏输出相比较:

输出控制寄存器部分相同

输出驱动器部分加入了P-MOS管部分

当输出控制电路输出1时:

P-MOS管导通N-MOS管截止,被上拉到高电平,IO口输出为高电平1

当输出控制电路输出0时:

P-MOS管截止N-MOS管导通,被下拉到低电平,IO口输出为低电平0

同时IO口输出的电平可以通过输入电路读取

8,GPIO输出工作模式4-复用推挽输出模式

与推挽输出模式唯一的区别在于输出控制电路之前电平的来源

开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的

开漏推挽输出模式的输出电平是由复用功能外设输出决定的

9,推挽输出和开漏输出的区别:

推挽输出:

可以输出强高/强低电平,可以连接数字器件

开漏输出:

只能输出强低电平(高电平需要依靠外部上拉电子拉高),适合做电流型驱动,吸收电流能力较强(20ma之内)

五,STM32-IO口相关寄存器

每组GPIO包含系列7个寄存器(7组GPIO共包含7*7=49个寄存器)

两个32位配置寄存器

GPIOx_CRL 低16位

GPIOx_CRH 高16位

两个32位数据寄存器

GPIOx_IDR 输入数据寄存器

GPIOx_ODR 输出数据寄存器

一个32位置位/复位寄存器

GPIOx_BSRR

一个16位复位寄存器

GPIOx_BRR

一个32位锁定寄存器

GPIOx_LCKR

六,STM32-IO口相关寄存器讲解

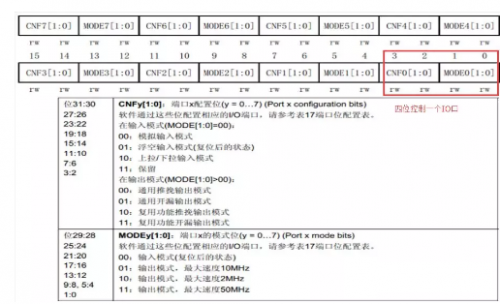

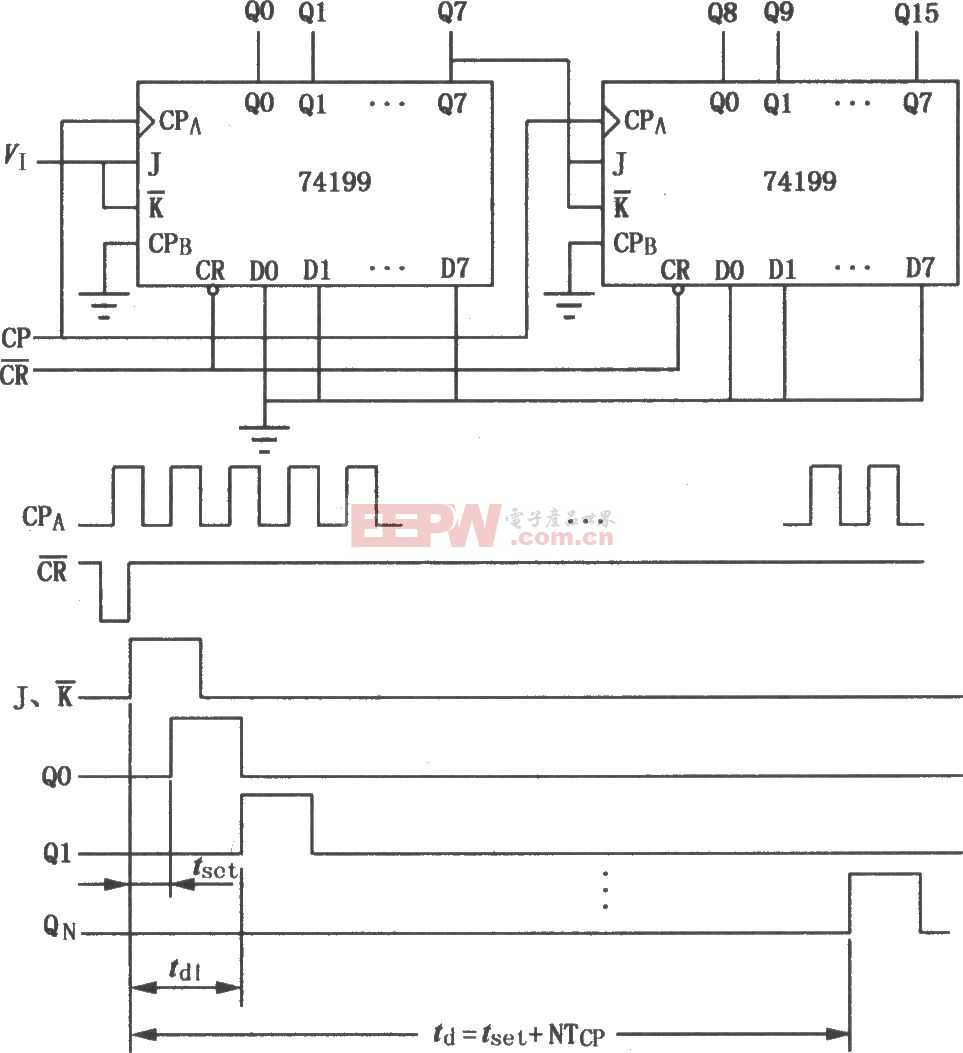

1,端口配置寄存器:

STM32每组GPIO位16个IO口,每4位控制一个IO口,所以32位控制8个IO口

分为低16位:GPIOx_CRL和高16位:GPIOx_CRH共32位控制一组GPIO的16个IO口

如图:以端口配置寄存器低16位为例,每四位控制一个IO口(高16位同理)

MODEx的2位 : 配置IO口输出/输出模式(1种输出+3种不同速度的输出模式)

CNFx的2位 : 配置IO口输入/输出状态下(由MODEx控制)的输入/输出模式

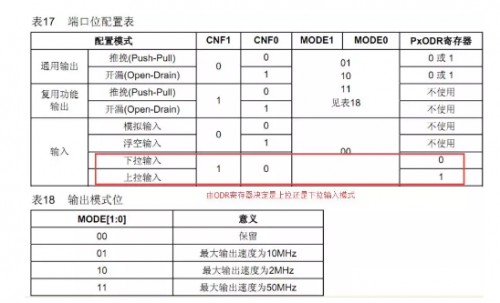

以GPIOA_CRL为例,配置IO口PA0 -> MODE0=00(输入模式) CNF0=10(上拉/下拉输入模式)

此种配置下到底是上拉还是下拉输入模式还需由ODR寄存器决定

关于上拉/下拉的控制我们将在下面-数据寄存器-中介绍ODR输出寄存器时详细说明

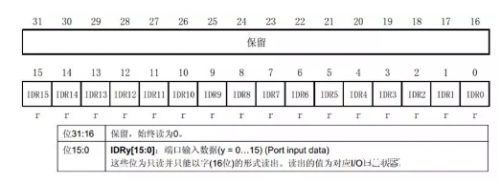

2,数据寄存器(以输入数据寄存器GPIOx_IDR为例)

每一组IO口都具有一个GPIOx_IDR的32位寄存器(实际只使用低16位,高16位保留),即16位控制16个IO口,每一位控制一个

如图:IDR寄存器共32位,0~15位代表一组IO口16个IO当前值

这里我们已经了解了输入/输出数据寄存器,现在说下上面提到的问题:

当IO口配置为输入模式且配置为上拉/下拉输入模式(即MODEx=00 CNFx=10时),ODR决定到底是上拉还是下拉

1)当输出模式时,ODR为输出数据寄存器

2)当输入模式时,ODR用作区分当前位输入模式到底是上拉输入(ODRx=0)还是下拉输入(ODRx=1)

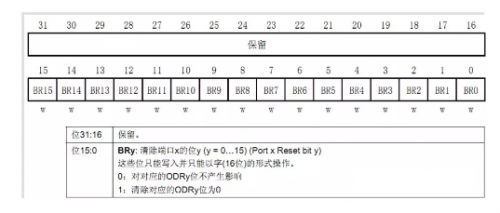

3,端口位设置/清除寄存器(GPIOx_BSRR)

BSRR寄存器作用:

BSRR寄存器为32位寄存器,低16位BSx为设置为(1设置0不变),高16位BRx为重置位(1:清除0:不变)

当然,最终的目的还是通过BSRR间接设置ODR寄存器,改变IO口电平

4,端口位清除寄存器(GPIOx_BRR)

GPIOx_BRR寄存器作用同GPIOx_BSRR寄存器高16位

一般我们使用BSRR低16位和BRR的低16位(STM32F4系列取消了BSRR的高16位)

5,锁存寄存器:使用较少暂不分析

七,端口的复用和重映射

1,端口的复用:

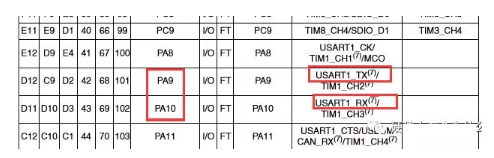

大部分IO口可复用为外部功能引脚,参考芯片数据手册(IO口复用和重映射)

例如:STM32F103ZET6的PA9和PA10引脚可复用为串口发送和接收功能引脚,也可复用为定时器1的通道2和通道3

端口复用的作用:最大限度的利用端口资源

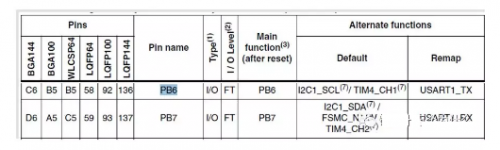

2,端口的重映射:

串口1默认引脚是PA9,PA10可以通过配置重映射映射到PB6,PB7

端口重映射的作用:方便布线

3,STM32所有的IO口都可作为中断输入(51单片机只有2个端口可以作为外部中断输入)

评论