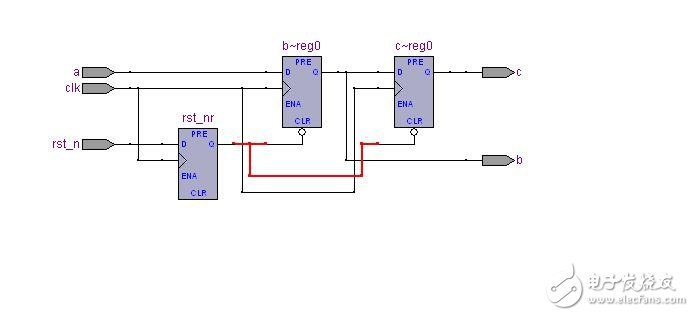

异步复位,同步释放的方式,而且复位信号低电平有效

一、特点:

同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。用Verilog描述如下:

always @ (posedge clk) begin

if (!Rst_n)

...

end

异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。用Verilog描述如下:

always @ (posedge clk,negedge Rst_n) begin

if (!Rst_n)

...

end

二、各自的优缺点:

1、总的来说,同步复位的优点大概有3条:

a、有利于仿真器的仿真。

b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

他的缺点也有不少,主要有以下几条:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

2、对于异步复位来说,他的优点也有三条,都是相对应的:

a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

缺点:

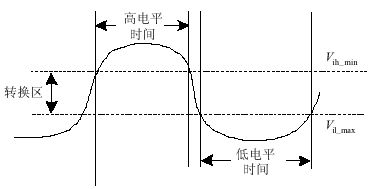

a、在复位信号释放(release)的时候容易出现问题。具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

b、复位信号容易受到毛刺的影响。

三、总结:

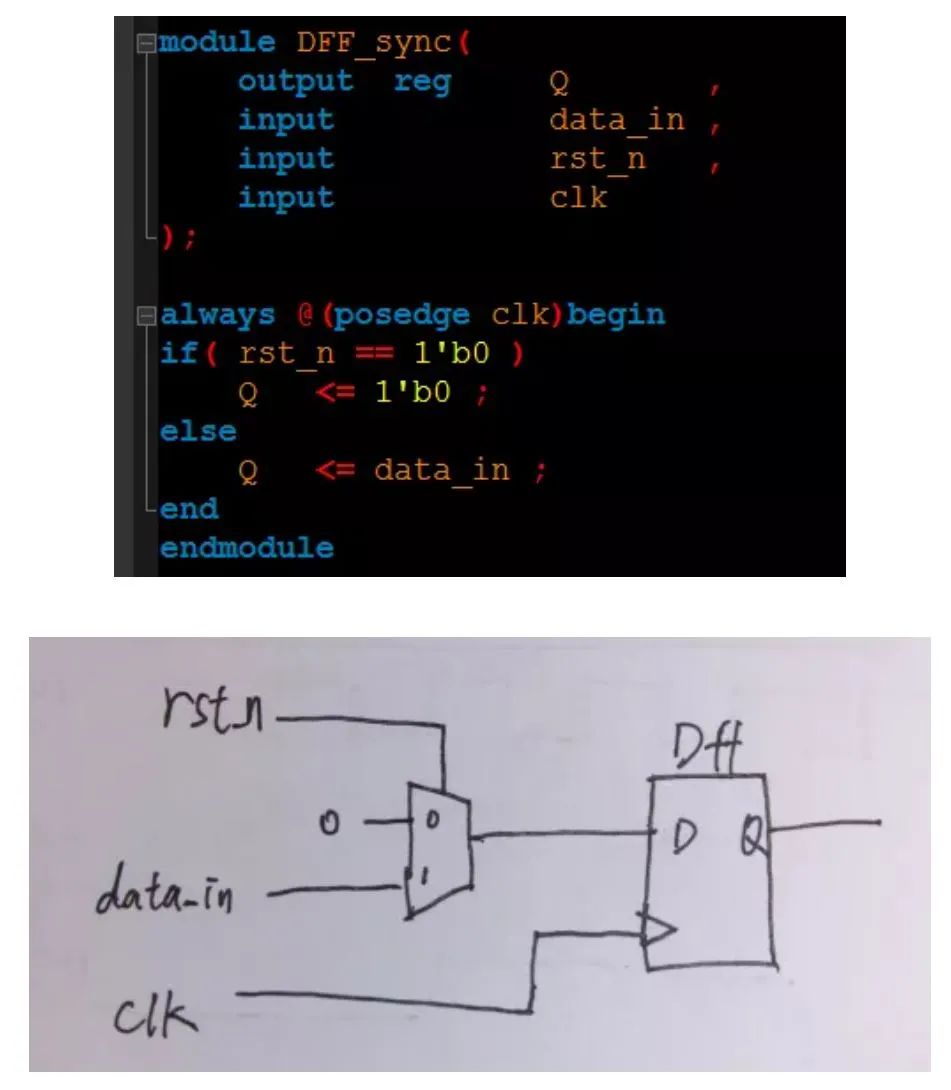

所以说,一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。这样就可以两全其美了。

always @(posedge clk or negedge rst_n)

if(!rst_n) b = 1b0;

else b = a;

我们可以看到FPGA的寄存器都有一个异步的清零端(CLR),在异步复位的设计中这个端口一般就是接低电平有效的复位信号rst_n。即使说你的设计中是高电平复位,那么实际综合后会把你的复位信号反向后接这个CLR端。

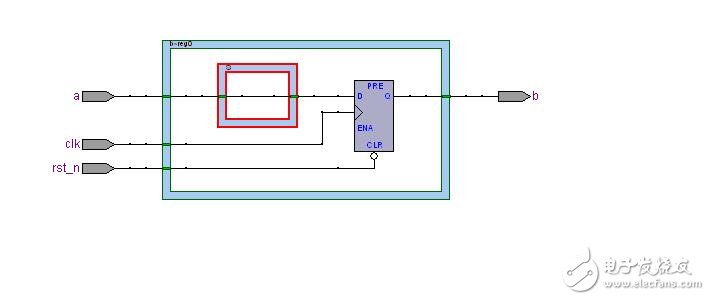

一个简单的异步复位的例子

always @ (posedge clk or negedge rst_n)

if(!rst_n) b = 1b0;

else b = a;

我们可以看到FPGA的寄存器都有一个异步的清零端(CLR),在异步复位的设计中这个端口一般就是接低电平有效的复位信号rst_n。即使说你的设计中是高电平复位,那么实际综合后会把你的复位信号反向后接这个CLR端。

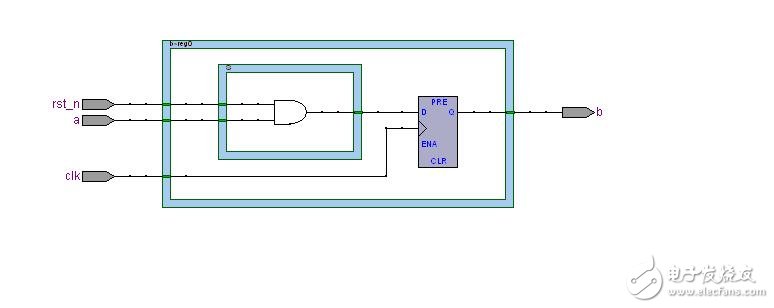

一个简单的同步复位的例子

always @ (posedge clk)

if(!rst_n) b = 1b0;

else b = a;

和异步复位相比,同步复位没有用上寄存器的CLR端口,综合出来的实际电路只是把复位信号rst_n作为了输入逻辑的使能信号。那么,这样的同步复位势必会额外增加FPGA内部的资源消耗。

那么同步复位和异步复位到底孰优孰劣呢?

只能说,各有优缺点。同步复位的好在于它只在时钟信号clk的上升沿触发进行系统是否复位的判断,这降低了亚稳态出现的概率;它的不好上面也说了,在于它需要消耗更多的器件资源,这是我们不希望看到的。FPGA的寄存器有支持异步复位专用的端口,采用异步复位的端口无需额外增加器件资源的消耗,但是异步复位也存在着隐患,特权同学过去从没有意识到也没有见识过。异步时钟域的亚稳态问题同样的存在与异步复位信号和系统时钟信号之间。

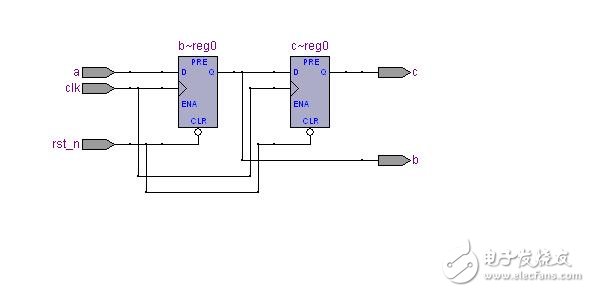

再看下面一个两级寄存器异步复位的例子

always @ (posedge clk or negedge rst_n)

if(!rst_n) b = 1b0;

else b = a;

always @ (posedge clk or negedge rst_n)

if(!rst_n) c = 1b0;

else c = b;

如此一来,既解决了同步复位的资源消耗问题,也解决了异步复位的亚稳态问题。其根本思想,也是将异步信号同步化。

评论