以太网端口保护需要智能化策略

除了合适的器件爬电距离和电气走线间隙之外,良好的以太网端口设计实践还需要过压和过流保护器件。算出印制电路板(PCB)的爬电距离和电气间隙之后,我们必须为以太网I/O连接的两端都选择保护器件,即线路(RJ-45)侧和驱动器(物理层或PHY)侧。

本文引用地址:https://www.eepw.com.cn/article/201706/352991.htm以太网保护器件一般是多通道瞬态电压抑制器(TVS)二极管阵列,在各种保护技术中,这种阵列可以提供最低的箝位电压。它们提供了各种各样的小形封装,从用于单端口保护的单个器件到保护多条线路的多个器件。这些器件全部整合在一个封装内,从而最大限度降低了对电路板的空间要求。

TVS二极管阵列在以下情况下使用:被保护的PHY电路需要低箝位电压、典型值为0.4pF至5pF的低电容以及0.1μA至25μA的低漏电流;必须对多条线路提供保护并且电路板空间有限时;由于各种威胁因素而出现瞬态电压时。

必须为以下四种主要的过压电气威胁选择具有合适特性的TVS二极管阵列:雷击引起的浪涌、静电放电(ESD)、电快速瞬变(EFT)和电缆放电事件(CDE)。低电容在这些器件中尤其重要,它可以避免信号失真,特别是在吉比特以太网电路中。

TVS二极管阵列必须连接在一起,以确保能够充分地抑制这些威胁因素。根据实际情况,它们应尽可能靠近电气威胁的进入点,同时将相同的地参考作为要保护的PHY。

威胁抑制可能需要考虑其他的设计因素,比如使用保险丝,将电源线旁路电容接地(靠近PHY电源输入引脚),以确保实现正常的电源滤波。应根据IEC或其他相关标准对PCB原型进行测试,以验证PCB布局是否具有合适的爬电距离和电气间隙。这在出现电力故障和浪涌情况时,有助于防止电弧形成,并使TVS二极管阵列能够有效地抑制这些事件的发生。

爬电距离和PCB走线间隙

为了防止以太网PCB上出现介电击穿和火花,线路侧和地应设置足够的爬电距离和走线间隙。爬电距离是两个导电部件之间或者一个导电部件与设备的边界面之间沿绝缘体表面所测得的最短路径。

足够的爬电距离可以防止漏电起痕,该过程会在绝缘材料表面产生局部衰减的部分传导通路,从而在绝缘表面或附近产生放电。

漏电起痕的程度取决于两大因素:PCB材料的相对漏电起痕指数(CTI)以及诸如高度、湿度和污染物等环境因素。CTI指标提供了在标准测试时由于漏电起痕引起故障的电压的数值。IEC 112标准给出了漏电起痕和CTI的全面说明。

电气间隙是两个导电部件(比如电路板走线)之间或者导电部件与设备的边界面之间在空中测得的最短距离。电气间隙有助于防止部件之间由于空气电离而产生的介电击穿。介电击穿水平还受PCB CTI等级、工作环境的相对湿度、温度和污染程度的影响。

板级设计人员经常会在计算爬电距离和电气间隙时考虑峰值工作电压,不过还需要考虑电气瞬态过程。有些瞬态电压甚至高达几千伏。

实验室测试表明,要耐受2kV的瞬态电压,FR4电路板走线间距应至少为25mil。不过,对于标准以太网双绞线为5mil、走线宽度为5mil的以太网板布局,该电气间隙可能太大了。

这是瞬态保护的另一个重要原因:降低高压使间距可以更小,即高压会由于TVS二极管阵列的箝位作用而得到抑制。在UL 60950-1标准中,表2K表明,2.8kV的最小电气间隙为8.4mm(330mil),1.4kV的最小电气间隙为6.4mm(252mil)。不过这针对的是稳态电压,而不是针对发生浪涌时快速上升的dv/dt。因此,通过TVS保持走线之间的电势差对于电路板布局来说至关重要。

了解瞬态事件的特性和极性有助于指导设计人员开发出最好的以太网端口保护方案。有了这种理解之后,就可以很好地把握如何定位和连接保护器件。

雷击引起的浪涌

大多数标准、建议或法规都将共模(纵向)浪涌要求界定为最低抗扰度级别。这些共模事件可以转换成差分(金属)事件。因此,有些标准、建议和法规还可以定义差分浪涌要求抗扰度级别。GR-1089-Issue 6,2 IEC 61000-4-5和ITU K20/21对波形的产生和测试过程有所介绍。

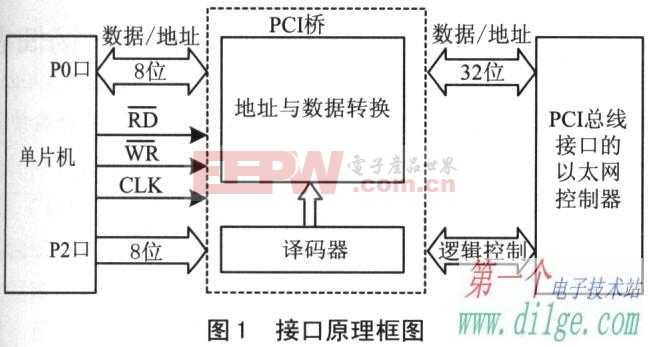

图1显示了这两种案例的测试装置。在差分模式下,两个导体或引脚(即J1和J2)连接在测试设备的正负两端,因此在RJ-45端口处插入的浪涌事件仅出现在这两个导体之间。大部分能量都在图2所示的线路侧保护装置TVS1(x2)中耗费。不过,有些能量也会通过变压器耦合,在变压器的驱动器侧产生共模或差分事件。

图1:在差分测试中,两个导体或引脚连接测试设备的正负两端。

对于共模测试而言,单个导体或数据线路本身将会相对于地进行测试。波形发生器输出将被连接到所有的导体或引脚(J1、J2、J3和J6),其地参考将连接至PCB地参考。请务必注意这可能并不是与PHY GND相同的参考点,而取决于应用程序的具体设计。

很多情况下,PHY GND与PCB的模拟地都是隔离的。这是使用耦合变压器的一个优势。在这种情况下,变压器上应只耦合很少的能量。不过由于绕组间电容的影响,TVS1与变压器相结合不会阻止所有的能量传送至PHY端。这些能量将通过变压器的磁性元件经由电容耦合到其驱动器侧,这些能量可能会在以太网PHY出现共模或差分事件(或者两者同时出现)时产生。

为符合IEEE 802.3标准的隔离要求,图2中的线路侧保护器件TVS1可能不会将其接地引脚(2、3、6和7)接地。尽管根据IEEE 802.3对UL-60950-1的引用,这种接地连接可被允许。如图2所示,TVS2始终将其I/O引脚连接至差分对。

图2:在两个引脚之间的RJ-45端口处出现浪涌事件时,大部分能量在线路端保护装置中耗散,而部分能量则通过变压器在变压器驱动器侧产生共模或差分事件。

不过,与线路侧保护器件不同的是,该器件将其接地引脚连接至局部地平面,并将其参考引脚连接至PHY VCC(Littelfuse公司建议使用这种配置)。如果未连接接地引脚的话,TVS2就会仅成为差分保护器件,并会潜在地允许具有破坏性的共模事件通过未箝制的PHY。

静电放电

静电放电(ESD)是小电路走线和器件的常见威胁。静电放电是由人体的静电电荷传输到电路所引起的,瞬态电压峰值高达15kV并不常见。在不太严重的情况下,ESD可能会导致错误的电路操作或者之后将发展成彻底故障的潜在缺陷。

ESD抑制器必须具有极快的响应时间,频繁地处理持续时间较短的高峰值电压和电流。TVS二极管阵列是箝位器件,可将瞬态电压限制在设定值。TVS的低动态电阻使其能够在超出其箝位阈值时,将这些高压ESD事件箝制在极低的电平(想想I×R)。一旦瞬态电压降到TVS器件的反向断态电压以下,TVS器件就将停止传导。

根据IEC61000-4-2标准,进行抗ESD测试的设备将通过接触和空气放电来进行测试。在测试中注入ESD的方法非常之多,比如IEC61000-4-2标准中给出的一些方法。但是在任何情况下,ESD脉冲都是以RJ-45连接器线路侧的共模事件出现,因为此放电事件以地为参考。保护器件被连接在一起,并根据上文讨论的共模事件进行测试。

电快速瞬变

根据IEC61000-4-4,进行抗EFT测试的设备与进行共模雷击浪涌的测试非常相似。在图3所示的较典型的配置中,所有的导体(或引脚)都连接至测试发生器的正极端,并相对GND产生浪涌。

图3:在电快速瞬变(EFT)测试的典型配置中,所有的导体/引脚都连接至测试发生器的正极端。施加的浪涌是以地为参考施加的。

若不是在以太网供电(PoE)应用中,就不需要使用耦合电容器,在以太网供电应用中,33nF的电容值应该就已足够。如果数据线路具有良好均衡,那么双绞线对之间就只有很少的差分能量或者不存在差分能量。不过,变压器的耦合电容还是会将共模能量传送到驱动器端,尽管能量有所减少。

电缆放电事件

电缆放电事件(CDE)在产生方式和波形特性方面都不同于ESD。CDE事件一般是在PVC包覆的CAT5非屏蔽双绞线(UTP)电缆拉在尼龙地毯或者瓷砖地板上时发生的,因为这种地板会导致电荷在电缆上逐渐聚集。同样,通过导管或者其他网络电缆铺设时,电荷也会在电缆上聚集。双绞线电缆由于储存了电荷,因此就像电容一样。

不过,只有当电缆无终端,并且电荷不会立即耗散时(即电缆的两端未插入系统),电荷才会逐渐聚集在一起。新型CAT5和CAT6电缆的介电泄漏极低,往往可以将电荷保持很长一段时间。在相对湿度较低的环境中,电荷保持时间会延长。

当带电的UTP电缆插入RJ-45网络端口时,将有很多可能的放电通路。这种瞬态电流会选择电感最低的通路,可能是位于穿过Bob Smith交流终端或者硅器件的变压器中的两条PCB走线之间的RJ-45连接器。这样,以太网收发器或者上述提到的任何器件都会受损。

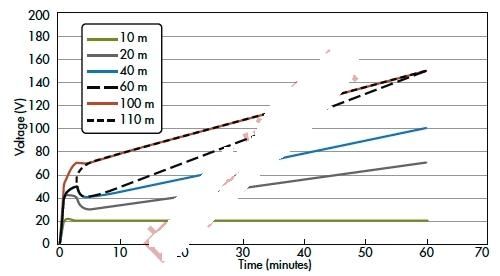

电荷量取决于电缆的长度(图4)。研究表明,无终端的双绞线电缆可以累积高达几千伏的电荷。对于电缆长度超过60m的系统,应采取额外的CDE预防措施。

图4:不同长度的CAT5以太网电缆的电压主要是由于静电电荷随时间的积累而形成。本图显示了长度从10m至110m的电缆的特性曲线。

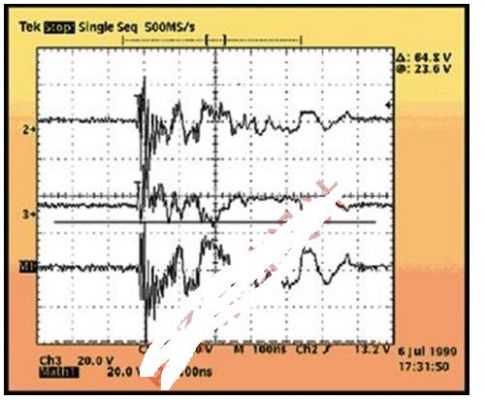

CDE波形并不像上文所述的任何一种其他的威胁。根据耦合机制的不同,CDE可以是差分的,也可以是共模的。虽然它可能有很大变化,不过其一般特性是具有表现电压和电流驱动的高能量。波形在数百纳秒的时间内展开,同时实现快速极性翻转(图5)。在这个实验中,PHY的发送器受到损坏,无法发射网络上的封包。

图5:图示显示了在25ft双绞线被充电至1.5kV后,以太网PHY的发送器引脚处的破坏性CDE波形。

系统设计人员可以按照上文所述,通过理想的布局实践(器件爬电距离和走线间隙)来最大限度地防止CDE。TVS二极管阵列有助于将IC和其他敏感器件中的能量转移。变压器电路还有助于防止出现共模瞬变。

需要记住的是,IEEE 802.3标准主张,2.25kVdc和1.5kVac的隔离电压可以防止由CDE产生的高压导致的连接器故障。为了防止发生这些事件时形成电弧,这些隔离要求适用于RJ-45连接器和隔离变压器。根据此IEEE 802.3文档中对UL-60950-1的引用,任何接地保护都可以从隔离测试中去掉,不过任何浪涌测试都需要重新安装这类接地保护。

在耦合变压器和RJ-45连接器之间的TeleLink保险丝(见图2线路侧保险丝),可以保护电路不出现过流浪涌。串火(power cross)事件和附近交流线路的浪涌耦合一般会导致出现这些浪涌。

保护器件的电路连接

TVS二极管阵列保护器件的大多数电路连接都在上文中雷击引起的浪涌部分有所介绍,这部分重点介绍了耗散瞬态能量的接地技巧。I/O连接如图2所示。

大多数TVS二极管阵列常见的剩余引脚一般都标注为VCC。该引脚应连接至以太网PHY电源轨(诸如5V、3.3V等),如图2中的驱动器(PHY)侧器件(TVS2)所示。请务必确保保护器件的断态电压或VRWM高于供电电压,以防止保护的稳态激活。

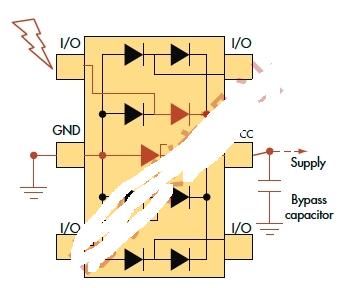

TVS二极管阵列采用多种半导体技术,从而使其能够提供两种保护(图6)。第一,它们通过二极管吸收瞬态电压,使电流绕开受保护的电路或器件。第二,雪崩或齐纳二极管将电压箝制至安全电平。

图6:以太网驱动器(PHY)侧TVS二极管阵列的内部连接显示了瞬变通路,通过雪崩二极管或齐纳二极管将瞬态电压从敏感电路中转移,并箝制到安全电平。

TVS二极管阵列在特定的浪涌电流波形测试中具有一个箝位电压。该箝位电压必须足够低,以保护以太网PHY,但也不能过低,否则会干扰正常的稳态信令。

通过将这类器件的VCC引脚连接至电源,TVS二极管阵列将由于电源和旁路电容提供的额外电流通路实现较低的箝位电压(参见图6中的红线)。它可以看作是一个电阻分压器,在这种电阻分压器中,瞬态电压进入控向二极管,并产生两条通路:一条通过内部TVS接地,一条通过旁路电容和电源接地。

结果表明,将VCC引脚连接至电源会实现更好的箝位性能,从而根据旁路电容的正确布局,为以太网PHY提供更好的总体保护。如果没有正确选择和放置此旁路电容,那么连接至电源轨将会引起瞬变损坏。

还应注意的是,某些二极管阵列具有展现回跳特性的内部TVS二极管,因此如果电源连接至外部,就可能受到损坏。在这种情况下,TVS二极管阵列的VCC引脚不应连接。

为VCC引脚加偏压的另一个好处是,它能够降低从I/O到GND的电容,而不是让它浮置或是断开连接。这对于防止信号加载和互调失真来说至关重要,特别是在吉比特以太网电路中。设计人员应参考用来保护以太网PHY的具体器件的数据手册,以便了解该电容的值,该值部分取决于VCC偏压电平。

器件选型参数

除了低电容之外,选择以太网保护器件时要考虑的另一个特性是动态电阻(RDYN)或者TVS器件处于活动或导通状态时的有效硅电阻。RDYN应该足够低,以确保具有快速响应时间和低箝位电压,即低I×R和R×C因数。

需要评估的其他器件因素包括反向断态电压(VRWM)、峰值浪涌电压、峰值浪涌电流定额(IPP)、ESD额定值、反向漏电流(IR)、箝位电压(VC)和峰值脉冲功率定额(PPK)。下表列出了图2中的保护装置的典型参数值。

除了这些选择标准之外,保护器件还必须适合电路板空间,并且能够提供适合可用安装和焊接设备的封装配置。主要考虑因素是选择一个能够保护以太网电路板及其器件,并且能够不出现故障地频繁实现这种保护的TVS二极管阵列。保护器件厂商会提供各种应用支持,帮助您在选型时做出明智的决策。

评论