确定运算放大器输出驱动能力的方法分析

在电路中选择运算放大器(运放)来实现某一特定功能时,最具挑战性的选择标准之一是输出电流或负载驱动能力。运放的大多数性能参数通常都会在数据手册、性能图或应用指南中明确地给出。设计者须根据输出电流并同时参考运放的其他各类参数,以满足数据手册中所规定的产品性能。不同半导体制造商所提供的器件之间,甚至同一家制造商所提供的不同器件之间的输出电流都存在很大区别,这使得运放的设计和应用变得更加复杂。本文将通过一些实例讲解如何根据运放的性能参数对所需进行设计的电路的驱动能力进行评估,从而帮助设计者确保自己所选择的产品,在所有情况下都具有足够的负载驱动能力。

本文引用地址:https://www.eepw.com.cn/article/201706/352023.htm哪些因素影响驱动能力

输出驱动能力是一系列内部和外部设定值或条件的函数。输出级的偏置电流、驱动级、结构和工艺都属于内部因素。一旦选择了一种器件来实现某一特定的功能,设计者就无法再改变这些影响输出驱动能力的内部条件。大多数低功耗运放的输出驱动能力较差,其中一个原因就是它们的输出级的偏置电流较小。另一方面,高速运放通常具有较高的驱动能力,可满足高速电路的低阻要求。高速运放通常具有较高的电源工作电流,这也会提高输出驱动能力。

传统上,集成化PNP级比NPN晶体管的性能要差。在这样的工艺下,PNP输出晶体管与NPN相比,越低的β值,意味着输出驱动能力会不平衡。满摆幅输出的运放通常会将晶体管的集电极作为输出管脚,性能较差的PNP管会导致提供源电流(source current)的能力比提供阱电流(sink current)的能力差。对于非满摆幅器件,情况恰好相反,由于大多数器件使用PNP晶体管的发射极输出,大大地影响了阱电流特性,因此它们输出阱电流的能力较差。而且,当估计器件的输出电流能力时,器件之间的性能波动也应考虑在内。因此设计者在基于典型的数据手册规范选择器件的同时,还必须考虑限值和最小规范,以确保所使用的每个器件在生产时都具有足够的驱动能力。

除上面所列的内部因素之外,一些外部因素也会影响驱动能力。其中一些能够被控制,以优化输出驱动能力,而其余的就很难控制。下面列出了影响输出驱动能力的外部因素:相对于相应电源电压的输出电压余量(相对于电源电压的差值);输入过驱动电压;总电源电压;直流与交流耦合负载;结温。

输出驱动能力通常以输出短路电流的形式给出。此时,制造商指定当输出接地(在单电源供电的情况下为1/2电源电压,称作Vs/2)时所能提供的电流值。制造商可能会提供两个数值,一个代表源电流(通常前面会有+),另一个代表阱电流(通常前面会有-)。在负载上电压摆幅很小的应用中,输出级驱动器相对于电源电压(源电流为V+,漏电流为V-)会有很大的电压差,此时用户能够使用这一数据来有效地预测此运放的性能。试想运放带一个很大负载并且该负载被一个接近地(或在单电源情况下为Vs/2)的电压驱动的情况。如果放大级的负载是逐步变化的,能向负载提供的电流将与运放数据手册中输出短路电流所给出的电流值一致。一旦输出开始随之改变,将发生两个情况:运放的输出电压余量减小;运放的输入过驱动电压减小。

由于前一个原因所能提供的输出电流将减小,这还与运放的设计有关,如后者中所述,过驱动电压的减小也会引起输出电流的减小。

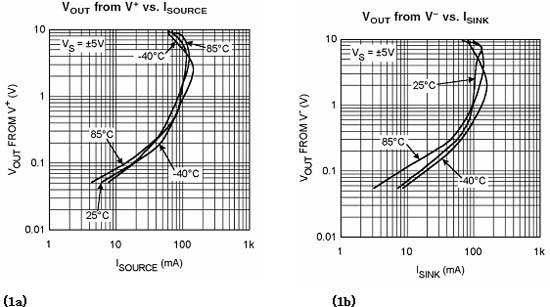

另一种更有用的确定电流能力的方法,是使用输出电流和输出电压图。图1显示了美国国家半导体公司的LMH6642的输出电流和输出电压图。对于大多数器件,通常会对源电流(图1a)和阱电流(图1b)这两种情况分别给出一张图。

图1:LMH6642的输出特征。

使用这种图,就能够估算出对于给定的输出摆幅运放所能提供的电流。这些图由半导体制造商提供,用来显示放大器的输出电流能力与输出电压之间的关系。

请注意,在图1中,描述了来自V+的Vout与输出源电流的关系,以及来自V-的Vout与输出阱电流的关系。用这种方法来表示数据的原因之一是,和输出电压相对于地的表示方法相比,它能被更容易地应用于单电源或双电源操作。另一个原因是由于电压余量比总的电源电压对于输出电流的影响要大得多,因此对于任意的电源电压,即使在数据手册上找不到精确对应的条件,这种数据手册示方法也能使设计者通过一组最接近的曲线来进行粗略的计算。

图1能够用来预测一个给定负载上的电压摆幅。如果坐标轴是线性的,设计者只需要在图1的特征曲线上加上一条负载曲线,通过这两条曲线的交点就能确定电压摆幅。但如图所示,很多情况下,尤其当运放是满摆幅输出时,两条坐标轴都使用对数坐标,以使得在输出电流很小、输出只有几毫伏的情况下,曲线也能有较好的分辨率。在对数坐标下,负载曲线不再是一条简单的直线,将不容易画出。那么如何才能预测一个给定负载的输出摆幅呢?

如果设计师愿意花些时间在器件性能和外部电路要求之间反复进行摆幅预测,会得到一个十分精确的结果。这里,我将利用一些实例说明如何进行这种预测。

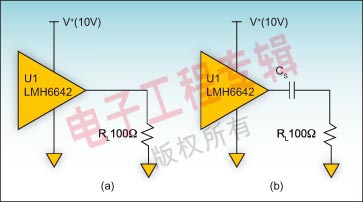

图2:预测给定负载上的输出电压摆幅的实例。

考虑如图2a的应用,其中LMH6642被用来驱动一个RL=100Ω并与Vs/2(1/2电源电压)相连的负载。假设此情况下LMH6642的输出被偏置在Vs/2或5V:

问题是设计师能够使用图1中所示的LMH6642的数据来估计可能的最大输出摆幅吗?答案是肯定的。

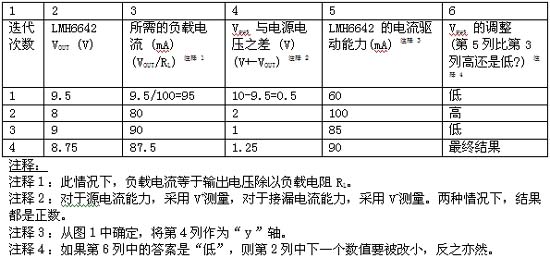

为了估计摆幅,要创建一张表(表1),它由输出摆幅的初始猜测值开始(第2列),接着是对猜测值的一系列修正(比较第3列和第5列,结果由第6列显示)。

表1: 使用迭代来预测图2a的输出摆幅(LMH6642)。

重复这一过程,直至在所给的条件下,器件特性与负载要求一致,便在第2列的底部得到了最终的结果,这样就完成了对摆幅的估算。因此,表1中的反复结果显示,图2a中的电路能在100Ω的负载上产生最高8.75V的电压。转换成峰峰值是7.5VPP{=(8.75-5)V x 2=7.5VPP}。

下面列出了表1中所使用方法的一些注意事项:对于图2a中的电路,只能提供源电流。因此,只使用了图1a。在每种情况下,在图1中假设最差的温度情况来计算第5列的数值。第5列中的数值是在图1a中将第4列的值作为y轴,然后从图中读出的。第2列中的最终结果,也就是第4次迭代的值,还是一个近似解,因为第3列(87.5mA)中的数值仍比第5列(90mA)低。但是,图中的分辨率已经不允许再对这个结果进行细调。

现在我们对刚才讨论的实例稍做变化,假设LMH6642的输出负载不变,但信号经过交流耦合的情况,如图2b所示。预测输出摆幅的方法与前面相同,只是由于交流耦合负载只能看到信号的摆幅,输出电压的直流分量(偏置)被交流耦合电容阻挡,因此表中的一些条目(第3列)需要被修改。此外,还要注意交流耦合负载需要LMH6642的输出能接受和提供电流(与图2a中只需要输出提供电流的应用不同)。因此,选择源电流和漏电流特征中较小的一个数值,填入表2中的第5列。

表2:使用迭代预测图2b的输出摆幅。

第2列中的最终结果(9.6V)对应于交流耦合负载上9.2VPP{=(9.6-5)V*2=9.2Vpp}的输出摆幅,像所预期的那样,要比前面所讨论的直流耦合负载的实例中的值(7.5VPP)大,原因是没有直流负载。

使用这些可选的输出能力图估算摆幅的过程,与前面给出的实例十分相似,都是使用反复方式对初始的猜测值进行细调。

如何测量输出参数

运放数据手册中的输出参数通常用一些根据合理数量的单位计算出的图来表示。数据手册中的图可以说是属于线性工作区,因为它们显示的是闭环工作条件下的典型特征。当然,大多数运放是在闭环条件下工作的,但是在某些特定的应用中,也需要在开环条件下工作。这意味着运放不能像通常那样,保持输入端之间的电压差为0。这是由于快速的输入变化要求运放的输出在很短的时间内改变。这就是说,环路是开放的,同时输出向最终值变化,在这段时间内,输入端之间会有一个很大的电压差。一旦达到最终的输出值,输入电压差又会再次减小到非常接近于0V(即输出电压除以运放很大的开环增益)。

像前面所解释的那样,一些运放由于架构的原因,在开环条件下能明显地提供更高的电流。但是在被用来在一个负载上维持一定量的电压摆幅这样的稳定正常的闭环条件下,输出电流能力必须在很小的输入过驱动电压条件下被确定。输入过驱动电压要大于运放输入级的输入失调电压,但不能太大,否则会影响电流能力。

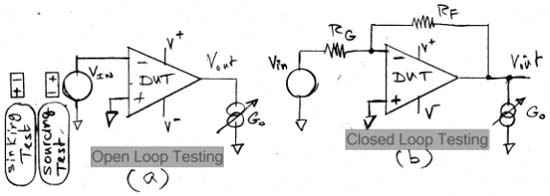

为了得到输出特征图,制造商会使用开环或闭环结构进行测量。只要遵循输入过驱动电压的要求,得到的结果是相同的。如图3a所示,在测量开环输出电流时,待测器件(DUT)的输出连接一个可变的电流源(或电流沉)发生器(Go),并由双电源供电。

图3:测量输出特征。

只需在输入端施加足够的差分电压,来克服输入失调电压并产生输出(对于源电流能力的测试,朝向正电源;对于输出阱电流的测试,朝向负电源)。此电压被称作输入过驱动电压(VID)。大多数运放需要大约20mV左右的输入过驱动电压来达到完全电流输出能力。为了支持较小的输出失真,在指定输出电流时,输入过驱动电压应小于+/-20mV。在这些条件下,输出电流源(电流阱)发生器可以在适当的范围内进行扫描,并且记录每个扫描点的输出电压。将输出电压(直接给出或是与之对应的电源电压之间的关系)与对应的发生器的输出电流画在图上,就得到了输出特征图。如果允许电流源(电流阱)发生器提供一个足够大的电流,最终得到的点的输出电压会精确地等于V+和V-之和的1/2(在电源对称的系统中就是地)。这一点对应的电流值就是数据手册上的输出短路电流,大多数运放的数据手册中通常会提供这个数值。如图1所示,输出短路电流大约为100mA,与之相对应的纵轴坐标为5V(对于+/-5V的电源)。

图3b中的设置与图3a中的相似,也能被用来测量输出特征。两种设置的差别在于,在图3b的电路中,DUT的环路通过RF和RG闭合。为了测量一个给定VOUT下的输出电流能力,需要设置适当的VIN来得到所需的VOUT。Go会一直增大直到达到所需的输入过驱动电压(VID)(通常小于+/-20mV,并大于输入失调电压,其值可以通过VOUT的下降(ΔVOUT)测得)。RF和RG的数值已知情况下,输入过驱动电压(VID)与VOUT下降之间的关系为:

VID= ( VOUT/(1+RF/RG),其中( VOUT是由于Go增大所引起的VOUT的变化

例如,当RF=10K、RG=1K时,如果Vin =-0.3V,则输出将为3V。所需的20mV的输入过驱动电压对应于由Go的电流变化所引起的输出电压220mV{=20mV * (1+10)= 220mV}的改变,或VOUT= 2.78V。

值得注意的是,一些专门为低功耗应用所设计的高压摆率的电压反馈运放,在前端使用了压摆率增强电路。这样能使运放节省功耗,并产生高速的大信号输出摆幅(换句话说就是高压摆率)。例如美国国家半导体公司的两款高速运放LM7171和LMH6657。为了达到上述目的,大输入摆幅增加了向内部补偿节点的电容所提供的电流,这一电容通常是用来限制运放压摆率的。因此,这一类器件的压摆率与输入过驱动电压相关。

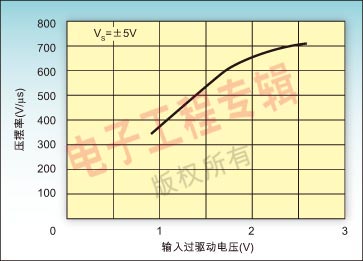

图4:LMH6657的压摆率与输入过驱动电压的关系反映出压摆率的增强。

图4是LMH6657数据手册中所给出的压摆率与输入过驱动电压的函数关系。

因此,在输入过驱动电压和输出压摆率较大的情况下,这类器件的输出电流能力也得到了提高。

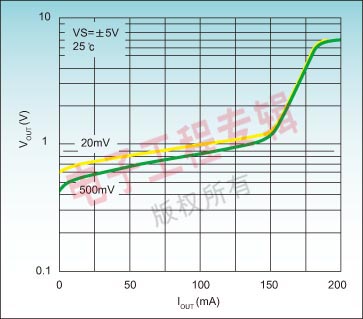

图5:两个不同的输入过驱动电压下,LMH6657的输出提供电流特征。

图5显示了在两个不同的输入过驱动电压下,LMH6657的输出提供电流能力(IOUT)与输出电压之间的关系,从中可以看出,较大的输入过驱动电压增大了输出电流(图中表现为对于相同的IOUT,输出电压到电源电压的余量要小)。这里没有给出接受电流特征,但结果是相似的。

与常规的电压反馈运放相比,更需要确保这类器件的输出特征被正确地理解。通过增大输入过驱动电压能够得到额外的输出驱动能力。但是,当进行像在负载上维持一个稳态摆幅这样的失真很小的闭环工作时,却需要很小的输入过驱动电压(前面已经提到过+/-20mV)。在输入过驱动电压很大的条件下指定的输出能力只能用于瞬态行为,此时输出尚未达到最终值,一旦输出达到最终值,输入过驱动电压就会下降到20mV以下。因此,当在稳态输出电流而不是瞬态行为十分重要的应用中,评估这类器件的性能时,需要注意输入过驱动条件。

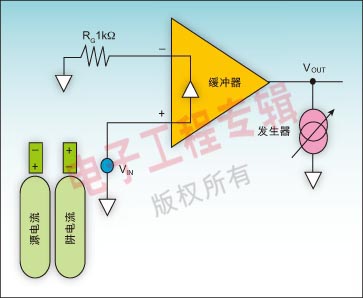

电流反馈(CFB)运放的输出特征的测量方法与上面所给出的方法十分相似。图6显示了进行这一测量时所使用的设置。

图6:测量CFB运放的输出特征。

CFB的结构是由一个位于正向和反向输入端之间增益为1的缓存器构成的,电阻RG使得电流能够流过反向端口。设置VIN的值大于输入失调电压,电流就会从反向输入端口流出,并且输出会向正电源电压V+增长(即会尽可能地靠近V+)。像前面所解释的电压反馈(VFB)运放的情况一样,电流发生器Go会对一系列适合DUT的电流值进行扫描,得到输出提供电流能力与输出电压之间的关系。通过颠倒VIN的极性并将Go设置成向DUT的输出管脚提供电流,就能够确定接受电流能力。注意,对于CFB结构,输入过驱动电压对于输出特征的影响比VFB结构要小。

输出能力和运放的宏模型:

美国国家半导体公司向用户提供的Pspice宏模型,能够很好地预测运放的许多参数,输出特征是其中之一。对于我们一直在讨论的LMH6642,图7给出了由美国国家半导体公司的Pspice模型所预测的输出特征。

在建立Pspice宏模型时,我们力图使图7中所示的模型曲线与图1中所示的典型的器件特性相符合。但是,仔细观察就会发现,图7中的曲线与图1中的典型特征曲线相比还是过于理想化。对于我们努力想要建模的参数来说,Pspice宏模型只能提供有限的精度。此外,通常而言,Pspice的输出电流模型,没有包括内置压摆率增强特性的器件中过度的输入过驱动电压会增强输出驱动能力的效应。

只要运放的宏模型中包括了这一行为,使用Pspice模拟能够直接快速地估计出一系列电阻负载上的输出电压摆幅(而不是像图7中显示的输出能力)。当LMH6642工作于图1A所示的电路条件下,附录B中所示的Pspice仿真文件是一种得到一系列电阻负载上的最大输出摆幅的可行方法(电阻范围为60~100欧姆,步长为10欧姆)。图8显示了Pspice所产生的结果图。

从这幅图中,设计者能够直接读取所指定的不同负载的输出电压摆幅,并画出如图9所示的摆幅与负载的关系图。对于一个100欧姆的负载,将Pspice所预测的9.48V的摆幅(如图9所示)与前面的迭代分析所预测的8.75V(如表1所示)的摆幅进行比较。当将Pspice的结果与数据表上的典型规格进行比较时,出现大约8%的差距是很普遍的情况。

作者:

Hooman Hashemi

首席应用工程师

美国国家半导体公司

评论