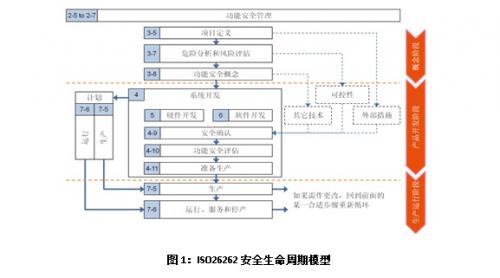

基于图像识别的汽车电子高级辅助驾驶系统的挑战与解决方案

作者:陈东华 飞思卡尔半导体

本文引用地址:https://www.eepw.com.cn/article/201706/350570.htm1 趋势

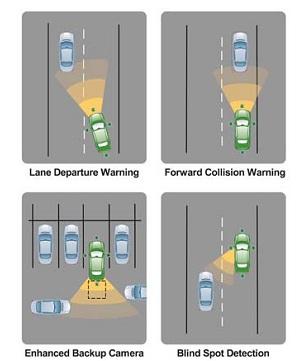

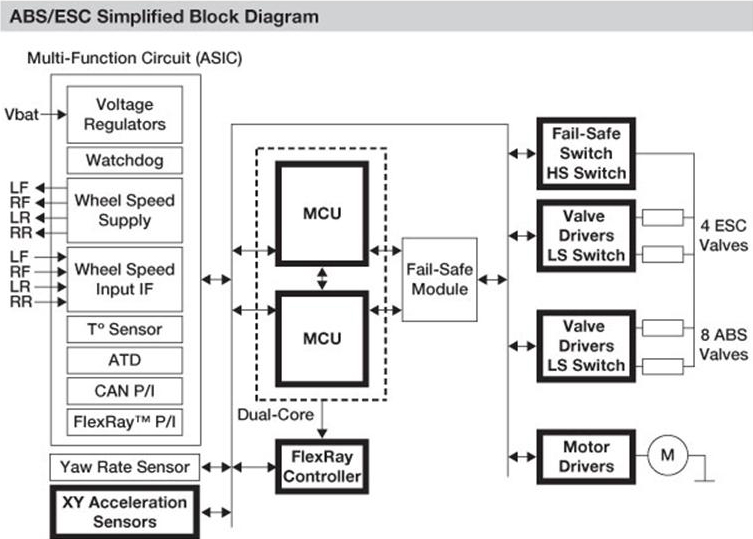

汽车电子业界现已开始采用智能图像处理来将多个摄像头采集来的数据进行同步,有效的给车辆提供了“看”和“识别”周围环境的能力。众多的厂商也都在为创建更安全的驾驶环境这一共同的目标而努力。飞思卡尔推出的带有APEX技术的图像识别处理器(ICP)使得下一代的智能安全车辆更易实现。ICP可以在智能视觉系统中实现实时的嵌入式图像和视频分析相关的应用,比如:带物体检测和图像校正的增强智能后视摄像头(EBC)、车道偏离警示系统(LDW)、碰撞缓冲技术(CAS)、盲点检测(BSD)等。

图 1 高级驾驶辅助系统

2 挑战

基于图像识别的高级驾驶辅助系统设计的挑战则在于,如何设计一个平台,能够持续的提供足够的处理性能,来满足计算密集类应用的需求,又能提供低功耗来避免散热的问题。在提供高性价比的低成本的解决方案同时,能够让系统设计者能够设计出比较小尺寸的封装。这样的智能的系统可能还需要集成图像传感器单元与智能摄像头互联(如果需要的话)。这样的集成了图像处理功能的图像传感器而搭建出来的智能摄像头系统,可以被用在车内多个不同的场合,比如安装在后保险杠作为可进行物体检测的增强型的智能后视摄像头、安装在侧后镜来进行盲点检测、安装在后视镜后面来进行前向的防撞检测和车道偏离检测、或者搭配其他的摄像头模块来实现360o环视效果。另外,这种分布式的智能摄像头模块不会增加车辆中央控制台的负担,不需要额外的系统资源开销。

市场分析报告显示,高级驾驶员辅助系统(ADAS)应用的增加将非常迅速,若干年后不仅是在高端车上,甚至在更多的普通低端的车辆上都会安装这样的应用。另外考虑到以上提到的每个应用都需要越来越多的计算性能,需求也非常的类似,目前也有趋势是越来越多的ADAS应用将会采用同样的硬件平台。这就提出了一个问题--目前的DSP和FPGA的方案是否适合呢?

DSP算法执行的最大的瓶颈之一在于需要从外部的内存区载入数据,才能保持对数据的读写访问。传统的DSP仅提供了有限的并行处理机制,而且为了满足处理能力的需求,通常需要的主频也越来越高。当时钟频率提升得越来越高时,系统的功耗也会越来越大,同样导致散发出的热量也越来越多。FPGA提供了相对于DSP更多的并行度,但是通常编程也会变得越来越困难,而且经常需要采用一个RISC来对数据做后处理。FPGA功耗更大,封装尺寸也更大,在系统的总体成本上也相对更高。

3 图像识别的未来: 多核并行处理

飞思卡尔基于多核并行处理机制的图像识别处理器系列(ICP)恰好弥补了DSP和FPGA的缺点。图像识别处理器在单位面积仅毫瓦功耗的情况下提供了更多的性能,并且集合了低功耗、高性能、小尺寸、完整软件开发平台等众多特性,给开发者提供了非常有竞争力的低成本方案。

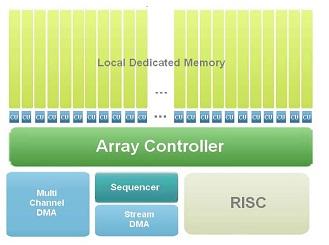

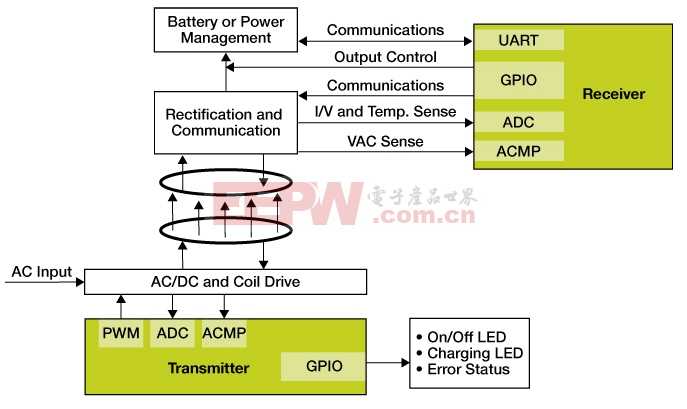

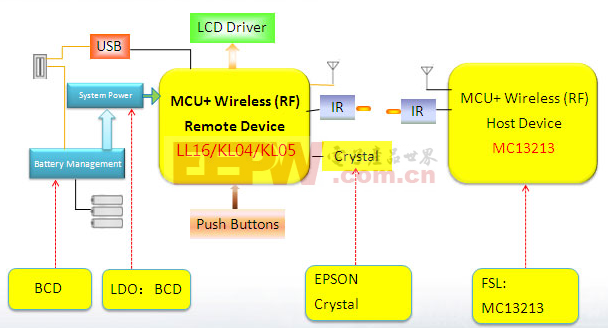

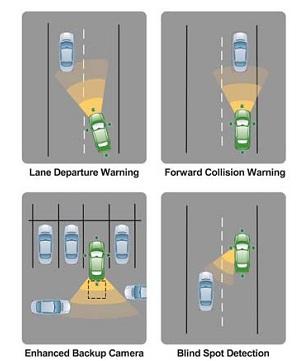

飞思卡尔的图像识别处理器的核心为APEX,如图2所示。这是一个多核的架构,由一个标准的RISC内核和一个矩阵处理引擎(APU)组成。RISC主要负责非并行的算法的处理并且管理算法的执行。APU则侧重于处理大量并行的单指令多数据(SIMD)的矩阵运算,通常是指图像处理和分析算法中比较底层并且运算量大的并行运算。除了RISC和APU,APEX架构中配备了直接内存存取流(DMA流)以便于进行高效的数据搬移,另外还提供了一个序列器来自动高效的按照顺序执行操作来实现效率的最大化。而应用层的程序则完全运行在图像识别处理器中的第二个RISC内核,该内核是独立运行于APEX之外的。

图 2 可编程的并行架构(APEX)

APEX灵活可扩展,可以通过增加处理元素(带有专用内存的计算单元的组合)的数量而线性的增加APU并行处理的能力。这样做不仅可以在较低的时钟频率下增强运行性能和并行操作度,而且还有利于降低功耗,减少热量的产生。处理元素是由计算单元(CU)组成的,每个CU都有自己本地专用的内存。一旦图像数据被从外部内存即系统内存取出并按照数据流的方式存入APU的内存中,则这些数据将一直存在本地内存中,所有的图像操作也将是基于这些本地的内存数据进行操作,直到所有的处理都完成后才会将这些数据按照数据流的方式存回到系统内存中去。通过这种将内存与APU的执行单元进行绑定的方式,我们大大减少了图像处理中对外部内存的访问次数,在不需要提升系统的时钟频率的情况下就能满足计算性能的要求,对降低功耗和提升性能也有非常大的帮助。

另外,APEX模块与ICP的其他模块耦合较弱。也就是说APEX内核的运行频率和SOC的其他部分的运行频率是无关的,因此系统的其他的这些部分可以运行在更低的时钟频率下,以便更好的节省系统的功耗。芯片采用了堆叠技术将外部内存也封装在内部,因此整个芯片的封装尺寸做得更小。得益于芯片的小封装和低功耗,整个板级设计尺寸也可以做得很小。

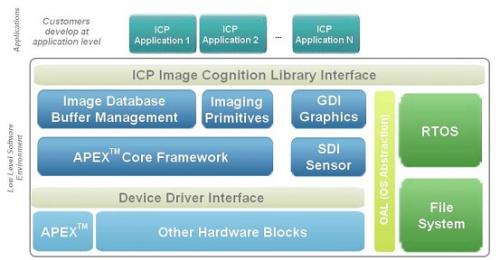

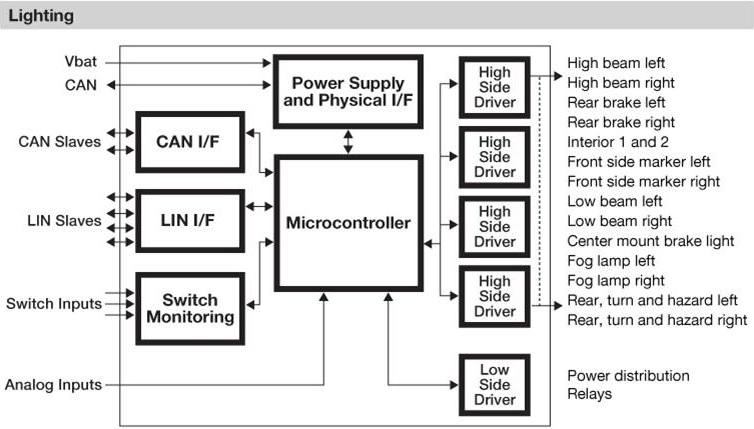

图 3 图像识别处理器软件架构

通过并行处理器内核,以及独特的软件可编程的数据流框架,飞思卡尔的ICP系列图像识别处理器能够轻松调度复杂的向量运算并且将数据搬移的搬移最小化。若在DSP执行同样的操作,则将占用更高的外部数据访问带宽,导致更高的功耗,产生更多的热量。APEX灵活可编程。飞思卡尔为应用开发提供了如图3 所示的软件框架。利用SIMD和软件框架,APEX能够达到FPAG一样的并行度,和DSP一样的编程的灵活性 。通过调用软件框架中已经过优化的图像识别库中现有算法的API接口,APEX能够更有效的充分利用算法本身所具备的自动流水线的特性来减少算法的复杂度,并且多核系统的均衡以及多核的同步这些复杂问题对于开发者来说也被隐藏起来了。APEX的可编程特性也使得用户可以添加自定制的算法到现有的算法库中。

飞思卡尔的ICP图像识别处理器的高并行度,且具备高带宽算术逻辑运算单元(ALU)的架构确保了这样的平台可以提供足够的空间和性能,基于同样的硬件上可以实现多种不同的应用。灵活的开发平台和软件开发套件(SDK)使客户能够更方便的对APEX进行编程,来实现更具有竞争力和差异化的应用。这样的多核并行的架构平台之所以成为开发者青睐的选择,不仅是因为表面看得到的性能、功耗和尺寸的优势,更是因为在将来的图像处理应用的开发中,现有的代码的复用将确保项目开发可以更快更便捷。

更多关于汽车电子的技术资讯,欢迎访问 与非网汽车电子技术专区

评论