高成本效益的实用系统方法 解决QFN-mr BiCMOS器件单元测试电源电流失效问题

摘要

本文探讨一套解决芯片单元级电测试过程电源电流失效问题的方法。当采用QFN-MR(四边扁平无引线–多排引脚封装)的BiCMOS (双极互补金属氧化物半导体)芯片进入量产预备期时,电源电流失效是一个进退维谷的制造难题。

本文介绍了数种不同的失效分析方法,例如,数据分析、实验设计(DOE)、流程图分析、统计辅助分析和标杆分析,这些分析方法对确定问题的根源有很大的帮助,然后使用统计工程工具逐步滤除可变因素。

本项目找到了电流失效问题的根源,并采用了相应的解决措施,使电源电流失效发生率大幅降低,与主要竞争对手旗鼓相当。最终,这个项目只通过优化公司内部资源,就提高了封装测试总体良率,而没有增加额外制造成本。

这些改进措施还提高了产品质量,降低了客户投诉质量问题的风险。在全部解决措施落实到位后,随着量产成功,该项目节省制造成本38.25万美元。

1.0 前言

为了能够在技术快速变化的半导体工业中生存,不管是企业内部用户,还是外部市场客户,半导体厂商必须在客户心目中树立良好的形象,这是半导体企业保持市场竞争力和品牌价值所面临的最大挑战。“满意度”是建立良好客户关系的关键要素。相反,不能让客户满意的业务是无法持续下去的。

QFN-MR(四边扁平无引线–多排引脚封装)是意法半导体卡兰巴工厂产量的最大的产品,对公司财务业绩贡献率很高(按照全球评估标准)。

不过,为同一客户生产同一产品,有些外包厂(外包厂1和外包厂2)在产品质量上却更胜一筹,这迫使卡兰巴工厂必须自我改进。

产品1是QFN-MR产品,在量产预备阶段,电测试电源电流总失效率不合格,总良率损失达到5.2%。产品 1是意法半导体卡兰巴工厂的一个新产品线,需要给大客户留下交货快的印象,但是不能牺牲产品质量,因此,需要找到造成产品缺陷的主要原因。事实上,解决这些问题将会给卡兰巴工厂量产类似产品平台带来改良机会。

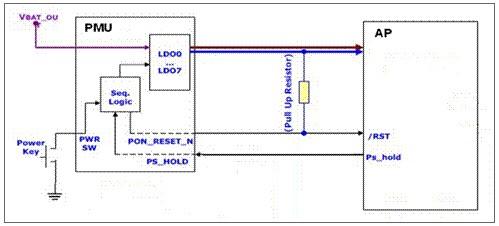

1.1产品1配置

产品1是一款采用VPLGA封装的BiCMOS芯片,用于控制硬盘驱动器的电机运行。这里VPLGA代表超薄格栅阵列四边扁平无引线–多排引脚塑料封装,封装厚0.90 mm,引脚88个。目标应用包括纤薄型电子设备和计算机硬盘驱动器的电机控制。

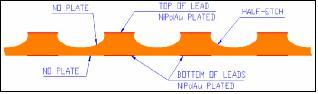

图1是产品1的封装示意图。

图1:VPLGA88产品配置 / POD

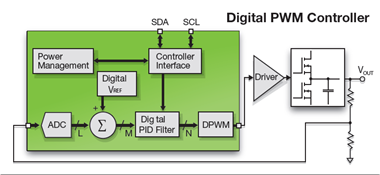

1.2BiCMOS半导体制造技术

图2:BiCMOS半导体制造技术

BiCMOS芯片由五层组成。NiPd (镍钯金)是最后一层金属层,互连线就打在这一层上。

1.3 QFN-MR无胶带引线框架封装

无胶带四边扁平无引线封装是一种引线框架封装载体(平台),利用后工序蚀刻,在载体上形成引脚面积。与其它的类似微型封装相比,无胶带QFN封装给意法半导体卡兰巴工厂带来更好实惠,例如,引线框架成本低,支持多排引脚,兼容铜线,无胶带载体,晶片切割速度快。

图3:无胶带QFN引线框架配置

1.4 产品1封测全部流程

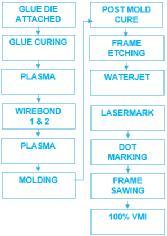

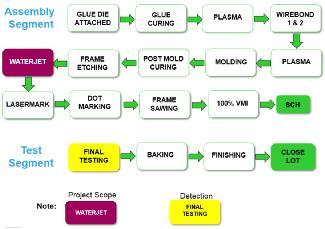

图4:1.4 产品1封装流程

图4所示是产品1的封装流程,该流程在产品开发和认证测试阶段制订,基于现有封装流程,采用相同的芯片制造技术和材料。

1.5 产品1线路应力表现

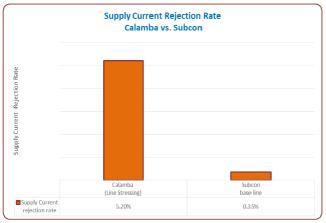

图5:电源电流抑制比对比

在产品1量产预备初期,最终测试的电源电流抑制比是5.20%,远超外包厂的0.35%。上面的柱形图是意法半导体卡兰巴工厂与外包厂的电源电流抑制比的比较图,两者之间的巨大差距对意法半导体卡兰巴工厂的未来业务发展构成重大威胁。

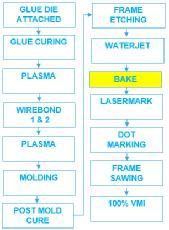

1.6 标杆分析和比较分析

运用标杆分析和比较分析法寻找意法半导体卡兰巴与外包厂在产品制造上的不同之处。需要说明的是,外包厂在水刀工序后还有烘烤工序。

图6:意法半导体与外包厂的制造流程比较

在开始分析的时候,我们发现烘烤工序是主要不同之处。在清洗等湿法工序后,需要进行烘烤工序,除掉单元内的湿汽。初步分析结果显示,烘烤是最终测试电源电流失效的主要因素,就是这个巨大发现让项目组开始专注这个工序的探究。

同样地,项目组还做了微流程图,以确定项目探究范围。

图7:微流程图分析/封装流程图

1.7 问题描述

在量产预备期,产品1电源电流抑制比是 5.20%,被归为封装工序固有湿法工序造成的潮湿性风险。

2.0 实验部分

2.1 材料:

§水刀

§QFN无胶带引线框架封装

§BiCMOS晶片

§塑料单元

§检查与测试设备

2.2 实验重点放在主要根源即水刀工序上:

确定问题根源并采取相应的纠正措施至关重要,研究方向主要放在湿法工序上,基于微流程图分析,水刀工序最有可能是潜在变异的根源。

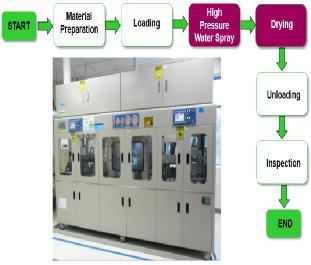

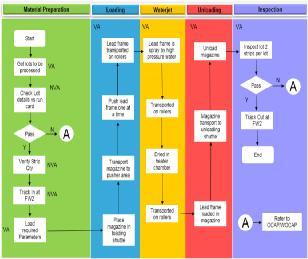

2.3 剖解水刀工序:

为更好地了解水刀工序,需要逐步分析记录点,观察从材料制备、装卸到检查的整个单元工序。

图8:水刀工序详细流程

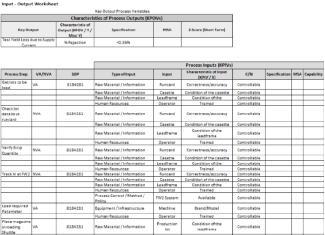

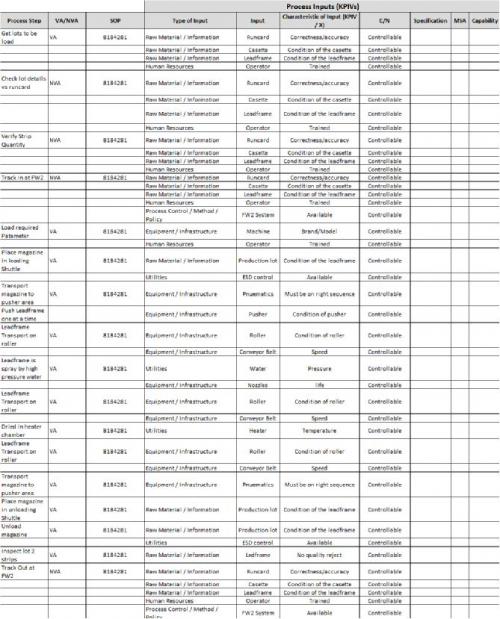

2.4 识别输入变化:

运用输入输出方法深挖变化因素。经过深入研究,42个KPIV变量被确定为重要的X因素,如图9所示。(详图见附录A)

图9:输入-输出工作单

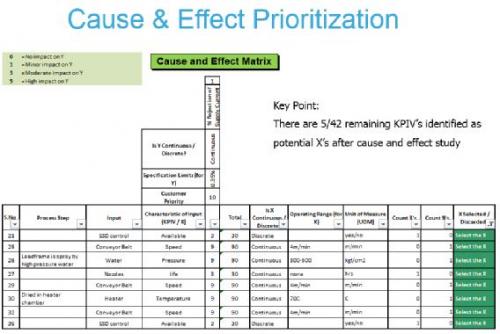

2.5 优先考虑因果关系:

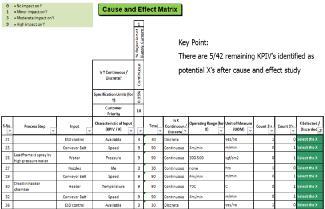

运用因果(CE)矩阵确立输入变量与X因素的内部关系,如图10所示。

(详图见附录B)

图10:因果矩阵

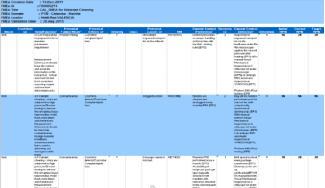

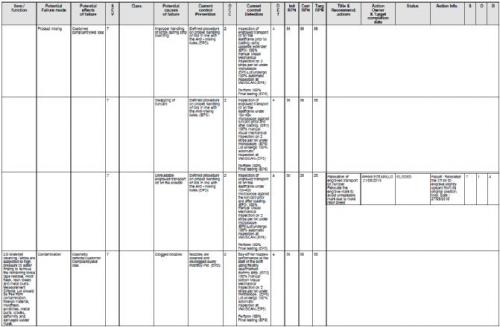

2.6 FMEA:

项目组还运用FMEA故障模式和影响分析法重新考虑变量关系。因为电源电流没有故障模式,所以考虑从因果矩阵导出的全部KPIV变量,如图11所示。(详图见附录C)

图11:故障模式和因果矩阵

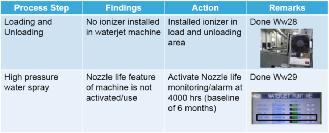

2.7 两个速效方案:

在完成上面的分析后,立即发现两个(2)速效方案。

图12:临时措施矩阵

实验结果分析

A.流程图

·这个项目覆盖18个流程工序。

·15个工序或83%是VA(增值),3个工序或17%是(无增值)

·未发现隐藏工厂

·在输入-输出工单中发现42个潜在X’因素。

B.因果矩阵

·运用因果优先性分析法找到5个潜在的X因素。

C.FMEA

·因为电源电流最初没有被识别为故障模式,所以5个潜在X因素都被视为高风险。

D.速效方案

·发现2个速效方案

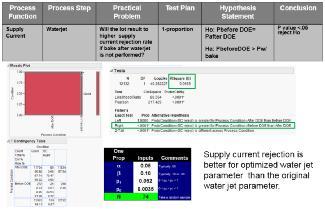

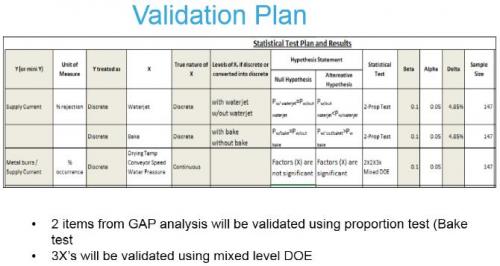

3.1 验证方案

图13:验证方案矩阵

•运用比例测验法验证GAP分析法产生的两个(2)项目(烘烤测试)

•运用混合水平DOE法验证三个X。

(详图见附录D)

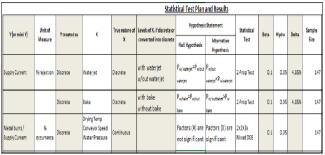

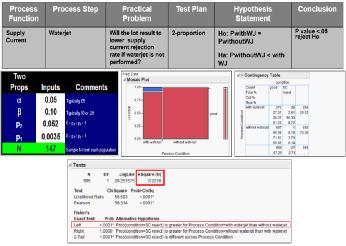

3.2 统计检验

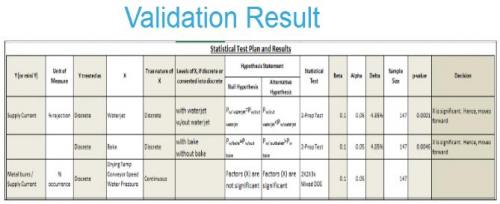

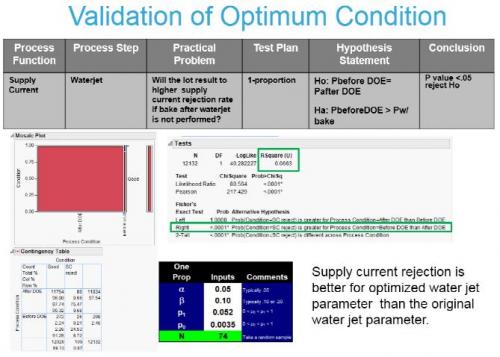

通过观察图14的统计假设检验结果不难发现,水刀后面的烘烤工序影响电源电流抑制比。

实用性结论:电源电流抑制在无水刀工序时较低,R-square值为22.78%,可信度高于95%。如果不采用水刀工序,电源电流抑制比较低。

图14:假设检验

3.3 验证方案

图15:验证结果

验证结果(图15)显示,电源电流抑制比受水刀后面的烧烤工序影响,因此,如果无水刀工序,则抑制比会降低。

根据已发现的关键X因素,例如,输送带速度、烘烤温度和水刀压强,项目小组运用试验设计方法进一步改进水刀工序。

(详图见附录E)

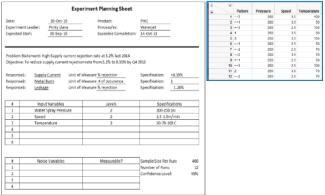

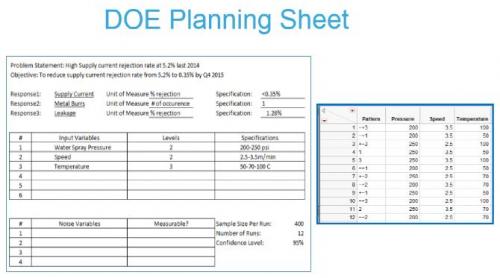

3.4 试验设计(DOE)

运用试验设计法分析输送带速度、烘烤温度和水刀压强参数,目标是确定和设置使电源电流失效率最小化的最优参数。

图16所示是试验设计方案,用于优化水刀关键参数。

图16:试验设计方案和结果

(详图见附录F)

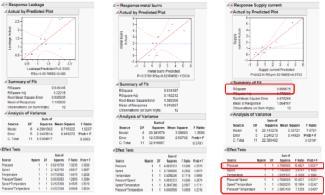

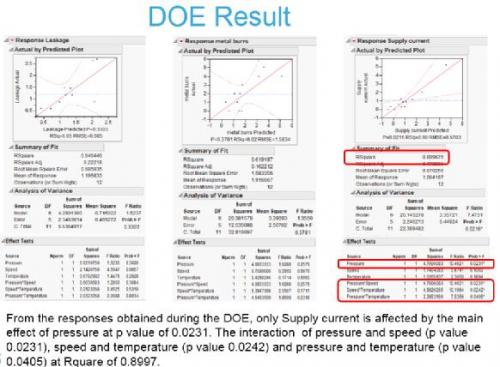

从试验设计结果看,当P值是0.0231时,压强是影响电源电流抑制比的主要因素。当R-Square值是0.8997时,压强与速度交互作用(P值是0.0231)、速度与温度交互作用(P值是0.0242)、压强与温度交互作用(P值0.0405)是影响电源电流抑制比的主要因素。

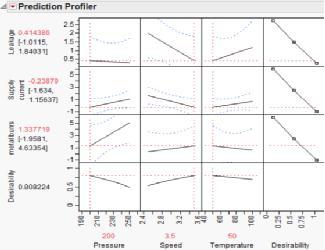

根据图17预测剖析图给出的最优设置,最大理想参数是在压强 = 200psi, 速度 = 3.5m/min,温度 = 50 degC时取得的,在这些参数条件下,电源电流抑制比为-0.238+/-1.156,泄漏为0.414+/-1.84,金属毛刺为1.338+/- 4.63。

在P值 = 0.0231时,压强是影响电源电流失效的主要因素;在P值 = 0.0231时,压强与速度交互作用也是主要因素;在P值 = 0.0242时,速度与温度交互作用是主要因素; 在P值 = 0.0405时,压强与温度交互作用是主要因素,可信度高于95%。

试验统计发现,当P值 > 0.05时,这些主要因素及交互作用不影响泄漏比和金属毛刺。

图17:预测刻画器剖析表

观察预测刻画器报表不难发现,当压强为200psi,速度为3.5m/min,温度为50 degC时,电源电流抑制比、泄漏和金属毛刺三个参数取得最优值。

3.5 试验设计(DOE)结论

在P值 = 0.0231时,压强是影响电源电流失效的主要因素;在P值 = 0.0231时,压强与速度交互作用也是主要因素;在P值 = 0.0242时,速度与温度交互作用是主要因素; 在P值 = 0.0405时,压强与温度交互作用是主要因素,可信度高于95%。

试验统计发现,当P值 >0.05时,这些主要因素及交互作用不影响泄漏和金属毛刺。

图18:结果验证矩阵

(详图见附录G)

3.6 水刀是如何影响产品1电源电流失效的?

了解失效机制知识有助于提高统计结果的准确性:

•封装渗透率或高速水分子引起的摩擦磨损效应随水刀压强升高而提高。

•高温鼓风机(相同压强)使气体分子动能更强,增强摩擦磨损效应。

•胶带速度效应最有可能影响摩擦磨损(接触速度),不过只限于鼓风机区,无水环境会逐渐消耗摩擦磨损效应。

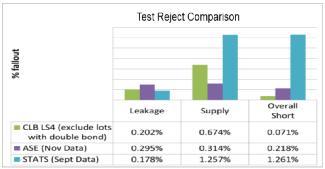

3.7 实现结果

意法半导体卡兰达工厂取得0.35%的电源电流抑制比(外包厂基准),较试验前的5.2%有巨大改进。

图19:电源电流抑制比趋势分析

图20:意法半导体卡兰巴工厂与外包厂比较表

总结:

a.泄漏

-意法半导体卡兰巴工厂(0.202%)好于外包厂1的生产批次(0.295%),外包厂2为 0.178%.

b.电源电流

-意法半导体卡兰巴工厂(0.674%)好于外包厂2的生产批次(1.25%),外包厂1为 0.314%.

c.Over-all short (SBL 0.5%)

-意法半导体卡兰巴工厂(0.071%)好于外包厂1的生产批次(0.218%)和外包厂2的1.261%。

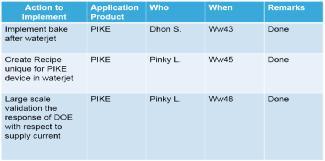

3.8 改正预防措施

为将取得的改进效果保持下去,需要落实下面的措施并密切监视落实情况:

图21:改正预防措施矩阵

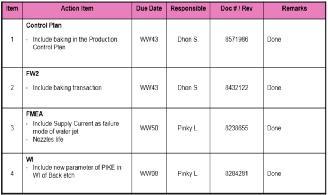

3.9 文档资料

所有分析活动和知识都写成文档保存,以便在产品量产期间参考。控制方案、FMEA、作业指导、包括烘烤的新流程均制成文档保存。

图22:文档资料名单

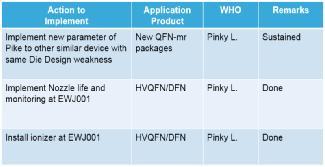

3.10 推广方案

为了最大限度利用这个研发项目的价值,需要将项目组在研究过程中所积累的全部知识经验推广到其它的QFN-MR产品制造过程。

图23:推广表

3.11 成本节省

在对改正措施的效果进行验证后,项目组还估算了这些措施可以节省的成本。

经意法半导体卡兰巴工厂IE核准,总计节省成本38.251万美元。

4.0 结论

本文论述了深度分析统计方法可有效解决最终测试过程中的电源电流失效问题。运用统计分析知识和对数据和缺陷现象的了解,有助于找到缺陷的真正根源。综合试验设计降低了水刀工艺对电流失效的负面影响。引入烘烤工序显著降低了单元电测试期间的电流抑制比发生率。失效率连续降低以及产品电测试良率总体提高,充分证明了验证纠正措施的正确性及其效果。

5.0 建议

建议长期落实已认可的纠正措施,以稳定电源电流性能。六个西格马方法论(逐步深挖问题,识别并验证问题根源,在使用现有资源且不大幅增加成本的前提下取得大幅改进)是解决制造难题的有效手段,在解决类似问题中应该推广这种方法。同时还推荐连续标杆分析法,这有助于企业改进流程,跻身业界前列。

6.0 鸣谢

本文作者向下列人士致以最真诚的谢意: Jun Bernabe、Mariver Limosinero、Addonyz Antonio以及封装部门的全体同仁,感谢他们在这个项目中给予的全力支持。

我们的家人、朋友、同事、同仁,这个项目的成功离不开他们的全力支持。

特别感谢我们全能的真主,始终保佑我们事业发展,生活如意。

7.0 参考文献

1.IC Assembly handbook

2.BSA (Build Sheet Assembly)

3.SAS – JMP

4.Water jet Machine Manual

5.Package Portfolio Technology Roadmap

8.0 关于作者

Antonio ‘Dhon’ Sumagpang毕业于菲律宾科技大学(马尼拉校区)电气工程专业(BSEE) ,学士学位。在半导体工业从业16年,拥有丰富的实际经验。在意法半导体卡兰巴工厂不同封装工序工作数年后,现任新产品导入高级工程师,新产品导入项目负责人。在第20届和第25届ANTS (ASEMEP国家技术研讨会)上先后两次荣获最佳技术论文奖。在质量竞赛中取得无数奖项,持有Green Belter证书。

Francis Ann “Pinky” Llana毕业于圣拉萨尔-巴科洛德大学化学工程(BSChE)专业,学士学位,拥有18年的半导体工业从业经验,现任意法半导体卡兰巴工厂高级封装工程师,负责湿法工艺,例如,铜层后工序蚀刻、化学去胶、凸点设计和电镀,在地区和国家质量竞赛中取得无数奖项,持有Green Belter证书。

Ernani D. Padilla毕业菲律宾东方大学,特许电子通信工程师,现任意法半导体卡兰巴工厂高级技术工程师,领导制造流程工程攻关小组,拥有注塑和等离子工艺方面专长,持有Neville Clark的blackbelt证书。

附录A

附录B

附录C

附录D

附录E

附录F

附录G

评论