基于Virtex-6 FPGA的三种串行通信协议测试及对比(一)

在高性能雷达信号处理机研制中,高速串行总线正逐步取代并行总线。业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试平台;然后设计并分别实现了三种协议的高速数据通信,测算了协议的实际传输速率;最后结合测试结果,从协议层次结构、链路数目、链路线速率、数据传输方式、协议开销、拓扑结构、设备寻址方式、应用领域等方面对三种协议进行了比较。本文研究工作可为三种协议的选用、测试和工程实现提供参考。

本文引用地址:https://www.eepw.com.cn/article/201612/326825.htm1引言

随着雷达带宽和AD采样率的提高,在高性能雷达信号处理机研制中,系统对数据传输带宽的要求不断增加,高速串行总线正逐步取代传统的并行总线。

Xilinx公司推出的Virtex-6系列FPGA,在片上集成了固化的GTX模块,以提供高速串行通信支持。同时Xilinx公司提供有多种串行通信协议IP核,便于用户进行开发。Aurora 8B/10B,PCI Express 2.0和Serial RapidIO 2.0是其中较为常用的三种协议。目前已有众多文献涉及到三种协议基于FPGA的实现方案。然而这些方案未能充分发挥协议性能,存在线速率较低(仅为2.5Gb/s)或未实现多通道绑定。针对上述问题,本文基于Virtex-6 FPGA,分别实现了三种协议在4x链路,5.0Gb/s线速率模式下的数据通信,测得协议的实际传输速率,并对三种协议的特点与应用进行了对比分析。

2测试平台简介

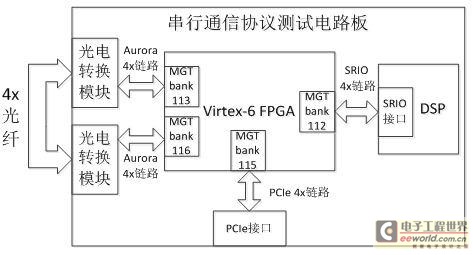

本文以实验室自行开发设计的PCIe光纤接收处理板(以下简称测试电路板)为测试平台。测试电路板的结构图和实物图分别如图1,图2所示。其中,FPGA选用XC6VLX240T-2FF1156,该芯片含20个GTX收发器,链路线速率可达6.6Gb/s.DSP选用TMS320C6678,该芯片含有SRIO接口,支持1x、2x和4x链路。光电转换模块选用FCBG410QB1C10,它包含4条链路,带宽可达40Gb/s.故而测试电路板的硬件设计符合本测试对数据传输速率的要求。

图1测试电路板模块结构和链路连接图

图2测试电路板实物图

如图3所示,将测试电路板插入服务器主板的PCIe插槽中,并将光纤接入测试电路板,完成测试平台的搭建。本测试中,PCI Express 2.0协议用于实现FPGA与服务器的数据通信,Serial RapidIO 2.0协议用于实现FPGA与DSP的数据通信,Aurora 8B/10B协议用于实现FPGA的光纤自发自收通信。由于三种协议都在物理层进行8B/10B编码,故在本测试工作模式下,它们的极限速率均为

图3测试平台搭建

3 AURORA 8B/10B通信测试

Aurora 8B/10B协议是Xilinx公司针对高速传输开发的一种可裁剪的轻量级链路层协议,通过一条或多条串行链路实现两设备间的数据传输。协议Aurora协议可以支持流和帧两种数据传输模式,以及全双工、单工等数据通信方式。

本测试中,Aurora 8B/10B IP核配置为双工、流模式,参考时钟频率250MHz.

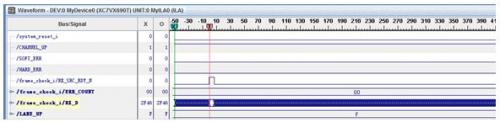

使用ChipScope软件观察FPGA相关信号如图4所示。观察RX_SRC_RDY_N可以发现,平均每4992周期出现7个周期的数据无效信号。由于接收数据时钟频率为250MHz,数据位宽为64bit,故本测试中,Aurora 8B/10B协议单向传输速率为,

图4 Aurora 8B/10B协议通信测试信号波形

下面分析协议理论传输速率和实际通信效率。该协议的帧格式比较简单,除2字节的起始标志,2字节终止标志和至多1字节的填装字符外,其余为数据部分。本测试采用的流模式是以无结尾的帧方式实现。故协议除8B/10B编码外,基本上不存在其他开销。故根据(1)式可得,协议的理论速率为2.0GB/s,协议的实际通信效率为99.75%.

4 PCI Express 2.0通信测试

PCI Express(简称PCIe)总线技术是取代PCI的第三代I/O技术。PCIe采用串行点对点互连,允许每个设备拥有专属的一条连接,不争夺带宽资源,同时保证了数据的完整性。PCI Express 2.0协议的链路线速率达到5Gb/s,最高支持32x链路。

本测试中,PCIe 2.0通信测试通过FPGA对服务器内存的DMA读/写操作来实现。

服务器方面,本测试选用Windriver软件进行PCIe驱动程序的开发。利用该软件提供的PCIe驱动程序及用户接口函数,编写符合本测试功能需求的程序。

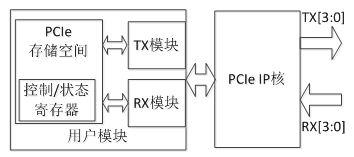

FPGA方面,本测试通过设计用户模块,实现对PCIe IP核的控制,完成DMA读/写操作。FPGA模块结构如图5所示。

图5 PCIe 2.0通信测试FPGA模块结构 为便于服务器对测试电路板FPGA进行控制,在FPGA的PCIe存储空间模块中,定义了若干控制/状态寄存器,这些寄存器的作用有:DMA读/写初始化,控制DMA读/写的启动与停止,标志一次DMA传输是否完成,设置一次DMA传输的数据量等。

服务器通过PCIe接口对测试板FPGA控制/状态寄存器进行读/写操作,来控制DMA的进程。每次DMA完成后,处理板FPGA会向服务器CPU发送一次中断。服务器对测试电路板FPGA DMA传输的控制流程如图6所示。

图6 PCIe 2.0 DMA传输控制流程图

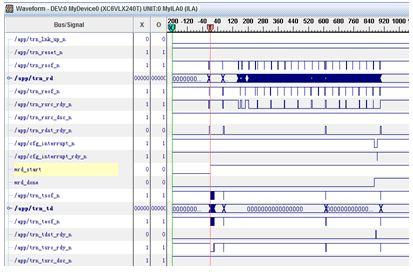

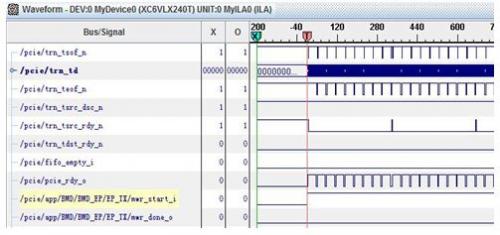

本测试将TLP包载荷数设为256Bytes(IP核允许的最大值),每次DMA传输的TLP包的数量为16384,故每次DMA传输的数据量为4MB.使用ChipScope软件观察FPGA内部的PCIe 2.0 DMA读/写相关信号,如图7,图8所示。本测试开发了PCIe读写功能测试软件,实现PCIe传输数据量和传输速率的实时显示。传输速率通过1s内DMA传输完成的次数来计算。测试结果如图9(a)、(b)所示。PCIe 2.0 DMA读的数据传输速率为1.770GB/s,DMA写的数据传输速率为1.820GB/s.

图7 PCIe 2.0 DMA读测试信号波形

图8 PCIe 2.0 DMA写测试信号波形

图9 PCIe 2.0 DMA读写速率测试结果(a)DMA读测试(b)DMA写测试

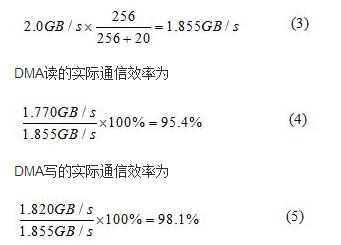

下面分析并计算本测试条件下PCIe 2.0 DMA读/写的理论传输速率和实际通信效率。

PCIe 2.0协议主要开销为8B/10B编码开销和数据包传送开销。PCIe总线以包的形式在不同器件之间交换信息。数据在进入处理层后会被封装一个包头,该包头长度在32bit地址下为12字节(本测试采用32bit地址)。当数据包进入数据链路层后,会添加2字节的序列号和4字节的LCRC字段。数据包进入物理层后,使用1字节的开始字符和1字节的结束字符将其封装成帧。

在DMA写测试中,FPGA每发送一次存储器写报文(含256字节数据)会带来20字节的额外开销。在DMA读测试中,FPGA向服务器发送存储器读报文,并由服务器返回完成报文(含256字节数据)。每返回一次完成报文会带来20字节的额外开销。由于PCIe 2.0定义了流量控制缓存管理机制,允许服务器返回完成报文的同时接收FPGA发来的存储器读报文,故DMA读测试中可忽略FPGA发送存储器读报文带来的开销。

故PCIe 2.0 DMA读/写的理论速率相同,均为

5 Serial RapidIO 2.0通信测试

RapidIO是针对嵌入式系统芯片间和板间互连而设计的一种开放式的基于包交换的高速串行标准,已在电信、国防等行业大量使用。

Serial RapidIO(简称SRIO)是物理层采用串行差分模拟信号传输的RapidIO标准。SRIO 2.0协议性能进一步增强,链路线速率可达6.25Gb/s,在电气层支持热插拔,并新添了控制符号和空闲模式功能。

本测试以测试电路板FPGA作为发起端,以测试电路板DSP作为目标端。通过FPGA向DSP发送SWRITE包,进行SRIO 2.0写测试,通过FPGA向DSP发送NREAD包,DSP向FPGA返回RESPONSE包,进行SRIO 2.0读测试。

评论