用于双极性输入的16位、125 MSPS单电源直流耦合型模拟前端

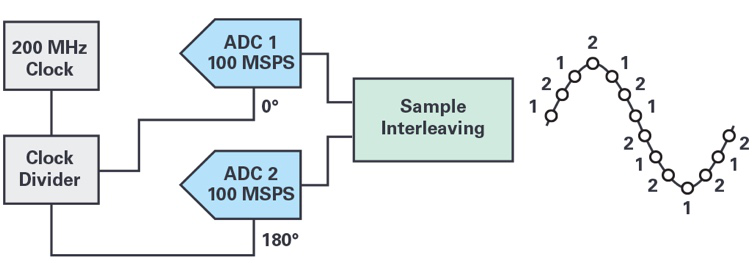

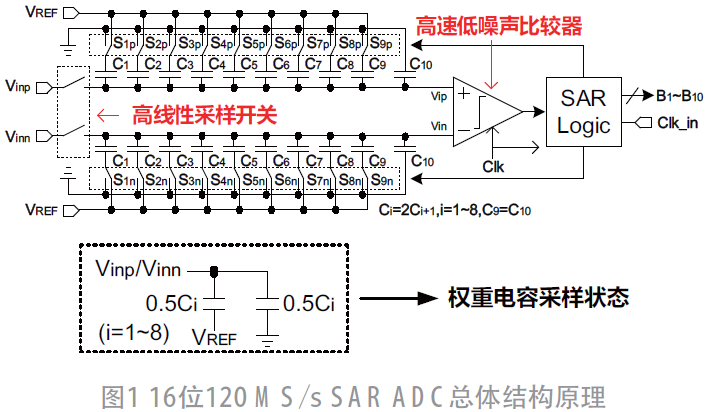

图1所示电路解决直流耦合单电源系统中双极性输入信号与差分输入、低压模数转换器(ADC)实现接口时经常遇到的问题。本技术使用两个电平转换电阻,通过控制输入共模电平,确保差分驱动放大器输入端具有正确的共模电平。通过对 ADA4930-1 差分驱动器的VOCM引脚施加正确的电压,单独实现输出共模电压。

这一灵活的方案允许 ADA4930-1差分驱动器采用3.3V单电源工作,同时16位、125MSPSADC AD9265 采用1.8V电源工作,以此最大程度降低总电路功耗。

在宽带应用中,目标频率范围通常包括直流。若要使差分输入ADC的动态范围最大,可适当增大典型输入信号,这便要求差分驱动器在较低的增益设置下工作。满足这些条件后,差分驱动器的输入共模电压还必须保持在额定范围内。

在直接耦合单电源应用中,经常需要对差分放大器的输入和输出共模电压进行独立控制;这些应用包括:处理具有高输入共模电压的解调器输出、直流器件连接差分器件的X射线应用,以及那些差分驱动器必须处理低数值输入共模电压的应用等。低输入共模电压应用可能包括单端或差分输入,输入可以是零输入、双极性输入或负输入。

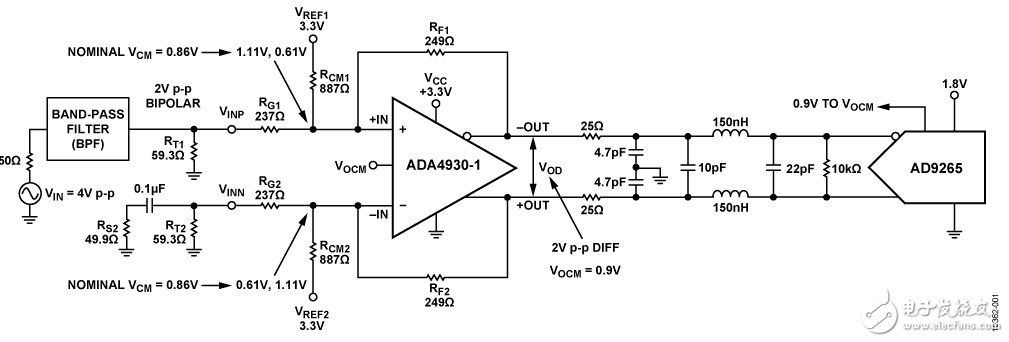

图1.高速、单端至差分ADC驱动器(原理示意图:未显示所有连接和去耦)

优势和特点

16位、125MSPS前端

双极性输入

应用:

通信

防务电子

电子测试和测量

雷达

电路描述

现代高速ADC通常由差分放大器驱动,以获得最佳性能。典型差分驱动器在增益小于等于2时可获得最佳交流性能,并且在单电源应用中,满量程输入信号频率超出ADC驱动器的输入共模电压范围。

为了避免使用差分放大器时的共模电压问题,必须仔细分析电路。针对 ADA4930-1 差分驱动器的设计公式与分析可在其数据手册内找到;而ADI公司的差分放大器计算器( DiffAmpCalc设计工具) 允许以节点分析的方式对电路进行完整分析,并将结果以图形格式表示。

图1中的电路使用 ADA4930-1因为它能在采用 3.3 V单电源的情况下输出0.9 V的共模电压(VOCM),该共模电平最为适合1.8 V ADC,如 AD9265。

为了优化噪声性能并尽可能减少其对信纳比(SINAD)的负面影响,选用的 RFx值为249Ω。然后,使用 DiffAmpCalc 软件设计工具,测得VIN至差分输出电压(VOD)的增益为0.511,从而确定RGx和RTx值。

图1中的输入信号来源于50ΩRF,并驱动带通滤波器。为了保持差分放大器源阻抗平衡,将0.1μF交流耦合电容与49.9Ω电阻串联,然后连接至未使用的输入,如图1所示。该电容的阻抗足够低,可用作70 MHz中心频率的交流短路信号。

采用3.3 V单电源并用于 ADA4930-1的输入共模电压范围为0.3 V至1.2 V。两个输入共模电阻RCM1和RCM2连接差分放大器输入引脚和基准电压 VREF1 与 VREF2确保满量程双极性输入信号下的输入共模电压不低于0.3 V。

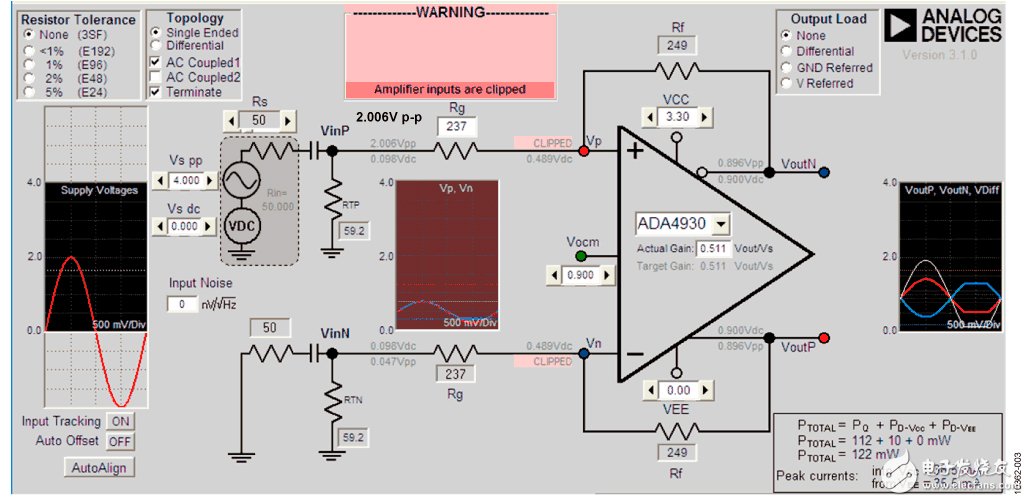

若没有共模偏置电阻,则 ADA4930-1的输入共模电压低于 0.3 V,采用满量程信号时会发生削波。

为方便起见,VREF1 和 VREF2分别连接 3.3 V单电源VCC与3.3 V电源的连接可提升标称输入共模电压,以适应输入信号摆幅。计算共模电阻的技巧可参见 ADA4930-1数据手册。

将小数值缓冲器电阻与差分放大器的输出串联使用是非常普遍的做法。这样做可以最大程度降低高频峰值,并将放大器输出与滤波器电容隔离。在图1所示电路中,这些值为25Ω。

3极点巴特沃兹低通滤波器有助于滚降二阶和三阶谐波,并降低ADC输入噪声。选择奇数阶滤波器,以便使最终滤波器电容与AD9265的输入电容并联。

巴特沃兹滤波器针对100MHz的截止频率、50Ω的输入阻抗和1Ωk的输出阻抗而设计。滤波器元件值四舍五入至标准值,并进一步优化,以获得最佳系统性能。

选择10Ωk电阻与ADC输入并联,其数值尽可能大,以便尽量减少信号路径上的衰减。 ADA4930-1与 AD9265距离很近,可最大程度降低70 MHz时的传输线路效应。因此,未采用驱动器输出与ADC输入间的传统端接方式。

驱动 AD9265时,应当注意不要过驱ADC输入。 ADA4930-1采用3.3 V电源时的最大输出为1.74 V,该值位于 AD9265的最大输入电压规格内。

共模电压分析

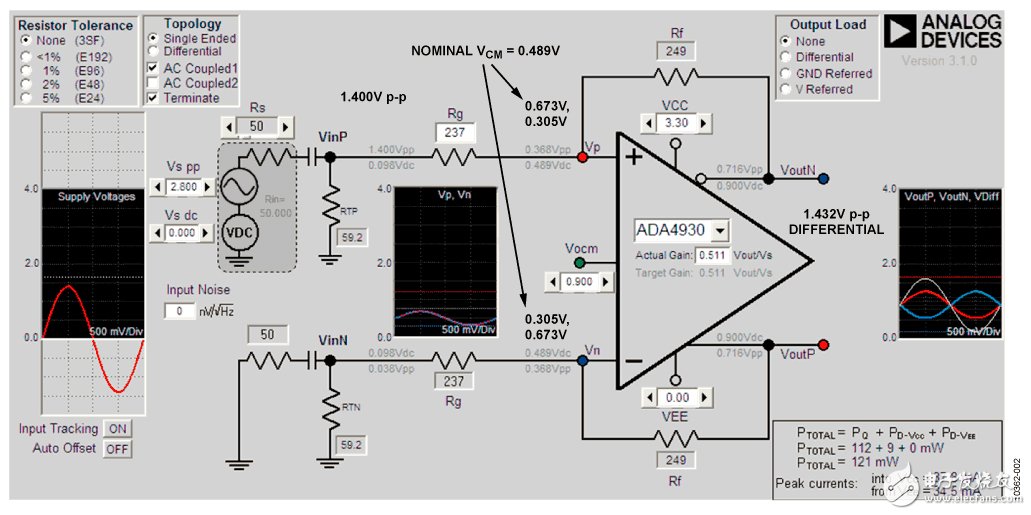

图2显示输入适当数值至DiffAmpCalc工具后,设计的基本切入点。注意,输入信号为1.4 V p-p,因此+IN和−IN输入的信号低至0.305 V。较大的信号会造成削波,如图3所示。

解决问题的方法之一是添加一个负电源,但由于不能超出5.5 V最大电源电压,因此不能使用±3.3 V电源。虽然可以采用一个+3.3 V、−1 V双电源系统,但这并不方便,而且会增加功耗。

如图1所示,加入的两个RRCMx电阻便是理想的解决方案,并且通过887Ω电阻可将 ADA4930-1上的标称共模电压从0.489 V上升至0.860 V。+IN和−IN输入的最大负摆幅和正摆幅现在分别是0.61V和1.11V,位于0.3V至1.2V的允许范围内。

图2.针对低电平输入信号的DiffAmpCalc设计分析,3.3V低电源,VOCM=0.9V

图3.针对满量程输入信号的DiffAmpCalc设计分析,3.3V电源,VOCM=0.9V,显示削波影响

电路性能

图4显示 AD9265评估板直接耦合至外部带通滤波器时的性能,中心频率为70 MHz,采样率为125 MSPS。 AD9265评估板的标准配置可采用一个RF巴伦将单端信号转换为差分信号。

图4.由巴伦驱动的AD9265Visual Analog FFT

图5显示了图1中使用AD9265和ADA4930-1且无887Ω偏置电阻的单电源设计。削波影响很明显。DiffAmpCalc也显示了这一削波影响(见图3)。

图5.ADA4930-1和AD9265 Visual Analog FFT移除RCM2和RCM2后显示削波影响

图6显示 ADA4930-1 采用3.3 V单电源供电时的性能,此时连接共模电阻RCM1 和 RCM2此外, AD9265 评估板上的巴伦和RC滤波器被移除,并以3极点巴特沃兹滤波器代替,如图1所示。

图6.ADA4930-1和AD9265 Visual Analog FFT 添加RCM1和CM2,如图1所示

以有效位数(ENOB)、SINAD和信噪比(SNR)作为品质因数,表1比较了图4、图5和图6的结果。

表1. ENOB、SINAD和SNR结果汇总

输入共模电阻的主要功能是独立转换输入共模电压,加入此电阻几乎不会对性能产生影响,如表1所示。例如,加入RCM电阻之前的ENOB是12.4,而加入以后则为12.1。根据图1中的配置,由于 ADA4930-1输出噪声密度为4.7 nV/√Hz,ENOB 的轻微下降可归结为本底噪声的轻微上扬。本数值采用DiAmpCalc工具计算得。因此,通过添加RCM1和RCM2两个电阻,即可单独控制ADC驱动器的输入和输出共模电平,同时保持出色的ENOB、SINAD和SNR性能。

常见变化

改变ADA4930-1的反馈和增益电阻是图1所示电路的变化形式之一。增加反馈和增益电阻至499Ω基本不会增加本底噪声,因此性能下降极少(见图7)。

图7.ADA4930-1和AD9265 Visual AnalogFFT,使用499Ω反馈和增益电阻

虽然改变增益和反馈电阻的影响不大,但ENOB则从12.1位下降至11.9位。

图1的另一种变化形式是使用替代型ADC,如 AD9255 (14位、125 MSPS)、 AD9258 (dual 14-bit, 125 MSPS)(双通道14位、125 MSPS)或 AD9268( 双通道16位、125 MSPS)。

对于需要双驱动器的应用,如基于双通道 AD9258 或 AD9268的I/Q接收器,可使用 ADA4930-2驱动器。

电路评估与测试

设备要求

需要使用以下设备:

带USB端口的Windows® XP、Windows Vista®(32位)或Windows 7(32位)PC

ADA4930-1YCP-EBZ评估板

AD9265-125EBZ评估板

HSC-ADC-EVALCZ FPGA数据采集套件

VisualAnalog软件

ADI公司的DiffAmpCalc工具

3.3 V、100 mA电源

0.9 V、100 mA电源

6 V、2 A壁装式电源(各两个)

125.127 MHz Wenzel晶体振荡器(器件号:500-25341)

70 MHz带通滤波器

125 MHz带通滤波器

RF源:Rohde & Schwarz SMA100A信号发生器

带BNC和SMA连接器的同轴电缆

软件安装

AD9265的 VisualAnalog软件可在 www.analog.com/visualanalog上找到;FPGA数据采集套件的使用指南可在 www.analog.com/fifo上找到。该软件兼容Windows XP (SP2)、Windows Vista和Windows 7(32位或64位)。下载 VisualAnalog软件并安装。

请先安装评估软件,再将FPGA数据采集套件连接到PC的USB端口,确保PC能够正确识别评估系统。

设置与测试

有关使用软件和运行测试的完整设置信息,请参考 UG-074用户指南 。图8显示测试设置的功能框图。

图8.测试设置功能框图

若要测试图1中的电路, AD9265评估板上的硬件需要经过下文所述的微小改变:

在J2安装SMA输入连接器INPUT−。

将T3和T6的巴伦移除。

将C2至C4、C15、C96和C71的电容移除。

将R1、R15、R16、R22、R23和R47的电阻移除。

在R1、R22、R23、R32、C3、C25、C71和C96安装0Ω电阻。

在R37和R47安装4.7pF电容。

在T6封装的引脚1和引脚6上安装150nH电感。

在T6封装的引脚3和引脚4上安装150nH电感。

在T6封装的引脚1和引脚3上安装10pF电容。

移除P18跳线。

此电路中所用产品:

AD9265:16位、125 MSPS/105 MSPS/80 MSPS、1.8 V模数转换器

ADA4930-1:超低噪声驱动器,适用于低压ADC

ADA4930-2:超低噪声驱动器,适用于低压ADC

评论