ADC噪声来自何处?

虽然交错式ADC具有极佳的速度和带宽性能等优势,而除此之外交错式ADC仍存在一些问题和不足之处。

这些问题主要围绕ADC的噪声源展开。 评估ADC噪声的具体情形时,噪声进入ADC的方式是最具参考价值的。因此,噪声进入ADC并体现在输出数据的FFT中时,所通过的入口类型则是需要系统设计师进行深入了解的。

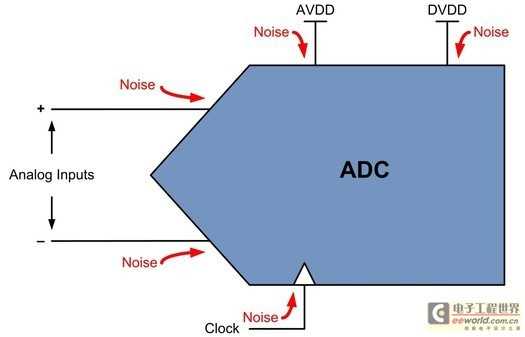

可将ADC大致视为混频器。如果有噪声从任一入口进入ADC,就会在输出数据的FFT中表现出来。 如图1所示,噪声可通过电源输入端、模拟输入端和时钟进入转换器。

ADC噪声“入口”

由于此处的噪声一词含义比较模糊,可以先根据所讨论的ADC输入(入口)来明确其含义。

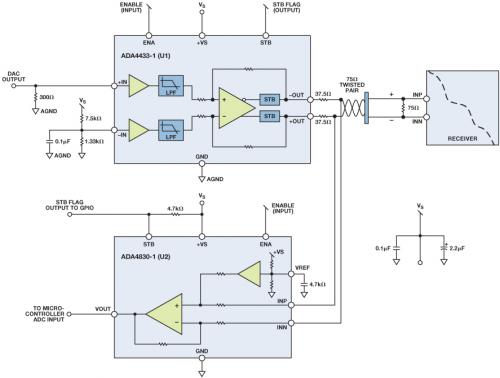

电源输入端是噪声的通道,噪声可由此进入ADC并体现在输出数据的FFT中。这种情况下,有几种方法可以评估该噪声及其对ADC性能的影响。ADC设计应该做到器件本身就可衰减来自电源的噪声输入。这里用于评估电源端噪声的度量方式是电源抑制比(PSRR)和电源调制比(PSMR)。通过测量这两个参数,可以了解到ADC对电源输入端噪声的处理能力。

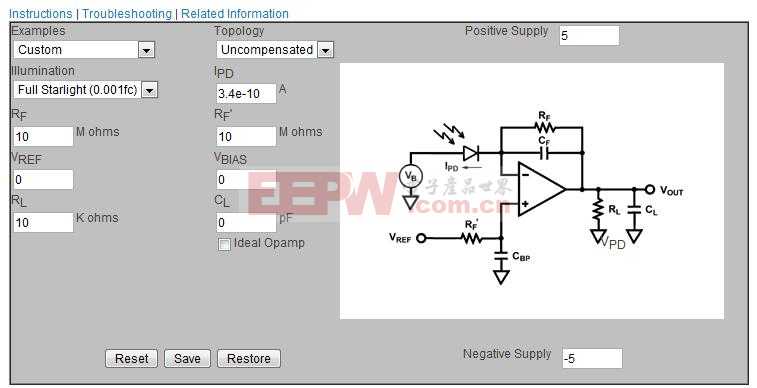

首先,针对ADC的模拟输入端,必须将噪声分成两种类型进行分析。首先,一般宽带噪声会通过模拟输入端进入转换器,并且通常源于信号链中位于ADC之前的器件。系统设计师可为ADC选择噪声极低的驱动放大器,但仍会有一定的噪声被放大并输入ADC。

为克服这一问题,通常会在ADC输入端添加一个抗混叠滤波器(AAF)。这有助于滤除可能进入ADC的大部分宽带噪声,并且最后会在ADC的信噪比(SNR)中体现出来。除宽带噪声外,杂散成分和谐波也可能通过模拟输入端进入ADC。这些也可通过AAF滤除。这将通过ADC的无杂散动态范围(SFDR)反映出来。 具有良好的AAF设计对处理这些状况非常重要。

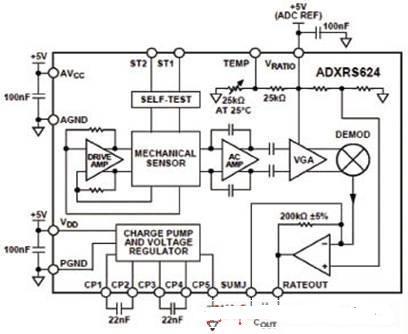

围绕ADC需要阐述的最后一个噪声入口为时钟输入端。该输入端与模拟输入端类似,宽带噪声以及杂散和谐波成分可由此进入ADC并体现在输出数据的FFT中。确保选择合适的时钟输入驱动器来为ADC提供干净的低抖动输入时钟,这点非常重要。

该时钟信号应以特殊方式连接至ADC,使其不会耦合能够进入ADC的噪声。与模拟输入端类似,可在时钟输入端添加滤波器来帮助滤除原本可能通过时钟输入端进入ADC的噪声。 同样,与模拟输入端类似,通过时钟输入端的噪声机制可通过ADC的SNR和SFDR性能表现出来。

使用ADC设计系统时,必须考虑到所有这些入口。经测试发现,应该将ADC作为混频器对待,它会将通过上述任一入口进入的各种噪声成分混合到输出数据上的FFT中。显然,系统设计师希望ADC的输出端只出现所需的信号。为了做到这一点,设计师必须在这些输入端采取适当措施,确保将噪声降至最低,使其无法通过这些入口进入。

评论