用于多站点并行测试的 ACS集成测试系统(一)

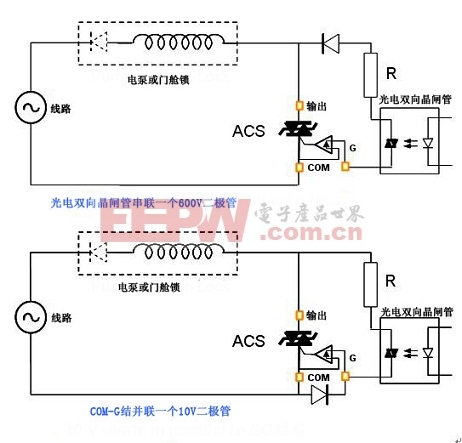

图1. 此例中的ACS集成测试系统配置为并行、多站点 测试,非常适于这些应用: • 多站点参数管芯分选 • 多站点晶圆级可靠性测试 • 多站点小规模模拟功能测试

行业面临的挑战

测试成本被视为未来先进半导体的 首要挑战。对测试成本和测试系统购置成本影响最大的是测试系统吞吐量。不 论什么具体应用,并行测试都最大程度 改善了晶圆上测试的吞吐量公式。这是 因为大部分开销用在了移动探针或者将 探针重新定位至下一个测试站点。开销包括了探测器和耗材(例如探针卡)的 成本和维护。最重要的是如何最大程度 利用这些投入。提高测试仪的吞吐量能 显著降低测试成本,缩短产品面市时间。

解决方案的理念

首先,考虑被测器件(DUT)。DUT常 常包含大量待测元素。在顺序测试架构中, 无论测试多么简单的元素都会增加总测试 时间。如果两个相同元素可以并行测试,甚至更好的情况是,如果物理位置相邻的 两颗相同芯片(如图2所示)可以并行测试,那么测试总吞吐量将翻番。不仅测试 仪吞吐量翻番,而且探针移动次数也减半, 进而显著提高了测试系统吞吐量。 非常重要的是重视芯片间可能出现的 寄生效应。例如,通过晶圆基底的耦合可能需要顺序执行一些低电流测试。非常幸 运的是,多数测试不涉及低电流。 管理测试成本的另一个关键是考虑使 用现有或常规探测方案。例如,常规探针 卡能用于探测图2中两个芯片的20个引脚。 此原理可以扩展至更大数量的芯片,同时继续使用现有的探测技术。

图2. 并列的两个小芯片站在常规探针卡容易到达的范 围。在此情况下,可以并行测试每颗芯片中的两个FET, 因而总吞吐量提高了400%。

评论