具有额外电压输出能力的完整4 mA至20 mA HART解决方案

电路功能与优势

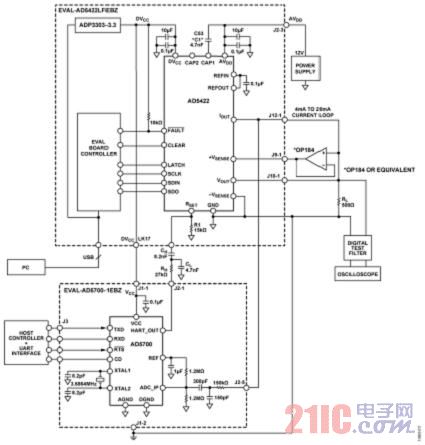

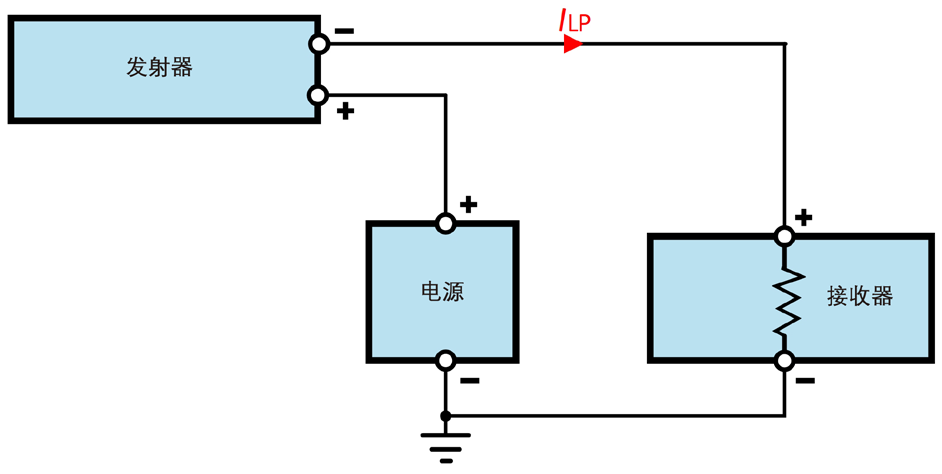

本文引用地址:https://www.eepw.com.cn/article/201610/308208.htm图1所示电路使用业界功耗最低且尺寸的HART®1兼容型IC调制解调器AD5700和16位电流输出和电压输出DAC AD5422,构成完整的HART兼容型4 mA至20 mA解决方案。该电路中采用 OP184,使得IOUT和VOUT引脚能够短接在一起,从而减少可编程逻辑控制(PLC)模块应用中所需的螺丝连接数量。为了进一步节省空间,AD5700-1 提供了精度为0.5%的内部振荡器。

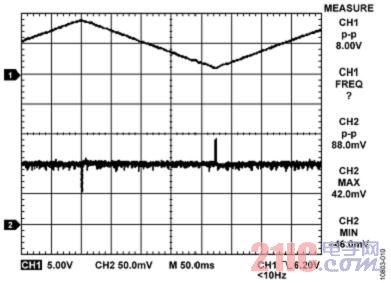

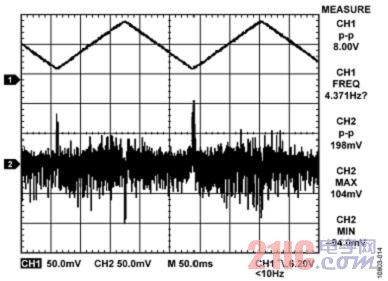

图9. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 3,SR阶跃= 2,C1 = 4.7 nF,C2 = NC

图9显示了AD5422的输出和HART滤波器的输出。滤波器输出端的峰值电压为82 mV,处于规定范围以内。压摆率设置为SR时钟= 3和SR阶跃= 2,从4 mA至20 mA的转换时间设为约120 ms,C1 = 4.7 nF,C2未连接。如果这个变化率太低,可以缩短压摆时间。采用C1 = 4.7 nF且C2未连接的电路配置时,可以发现压摆时间设为80 ms(SR时钟= 1,SR阶跃= 2)时,所得到的模拟变化率符合HART规范。然而,如果将压摆时间进一步缩短至60 ms(SR时钟= 0,SR阶跃=2),则会导致结果超出150 mV规格范围。从CAP1连接至AVDD的电容可用于抵消滤波器输出端因压摆时间过快而导致的峰值电压增加。然而,选择此值时必须小心,因为它会影响“确定外部元件值”部分讨论的低通滤波器截止频率。

图10显示了压摆率控制设置改为SR时钟= 5、SR阶跃= 2且C1电容值保持4.7 nF不变的结果。这样,转换时间就会在240 ms左右。滤波器输出端的峰值幅度可通过增加C1值、配置更慢的压摆率或通过两者的组合来进一步降低。

图10. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 5,SR阶跃= 2,C1 = 4.7 nF,C2 = NC

瞬态电压保护

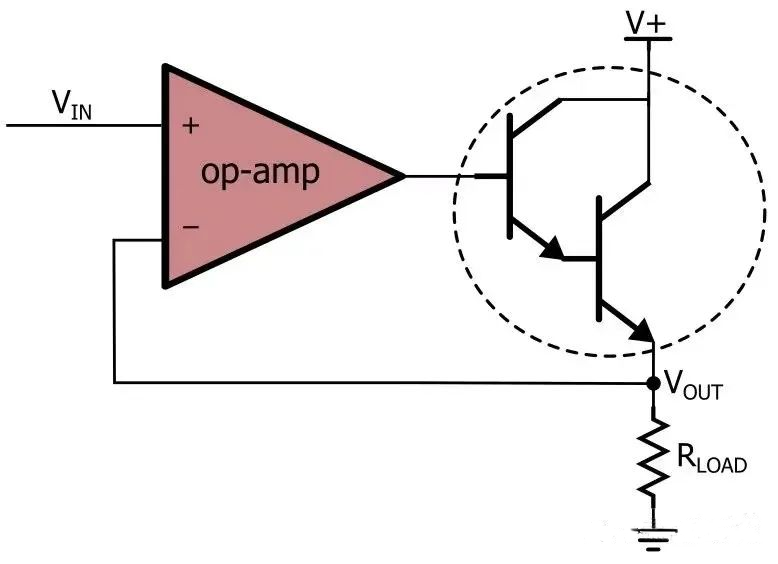

AD5422 内置ESD保护二极管,可防止正常操作造成的损害。但是,工业控制环境会使I/O电路遭受高得多的瞬变。为了防止过高瞬态电压影响AD5422,可能需要外部功率二极管和浪涌电流限制电阻,如图1所示。对电阻值的约束条件(图1中显示为18Ω)是,在正常工作期间,IOUT的输出电平必须保持在其顺从电压限值(AVDD − 2.5 V)以内,并且这两个保护二极管和电阻必须具有适当的额定功率。在18Ω的条件下,对于4 mA至20 mA输出,引脚处的顺从限值降低V = IMAX × R = 0.36 V。 OP184 缓冲器的正输入端还连接了一个10 kΩ电阻,用以限制瞬态期间的电流来保护放大器。通过瞬态电压抑制器(TVS)或瞬态吸收器可实现进一步的保护。这些元件包括单向和双向抑制器,可提供各种各样的隔离和击穿电压额定值。TVS应尽量采用最低击穿电压定标,同时在电流输出的功能范围内不导通。建议保护所有远程连接节点。

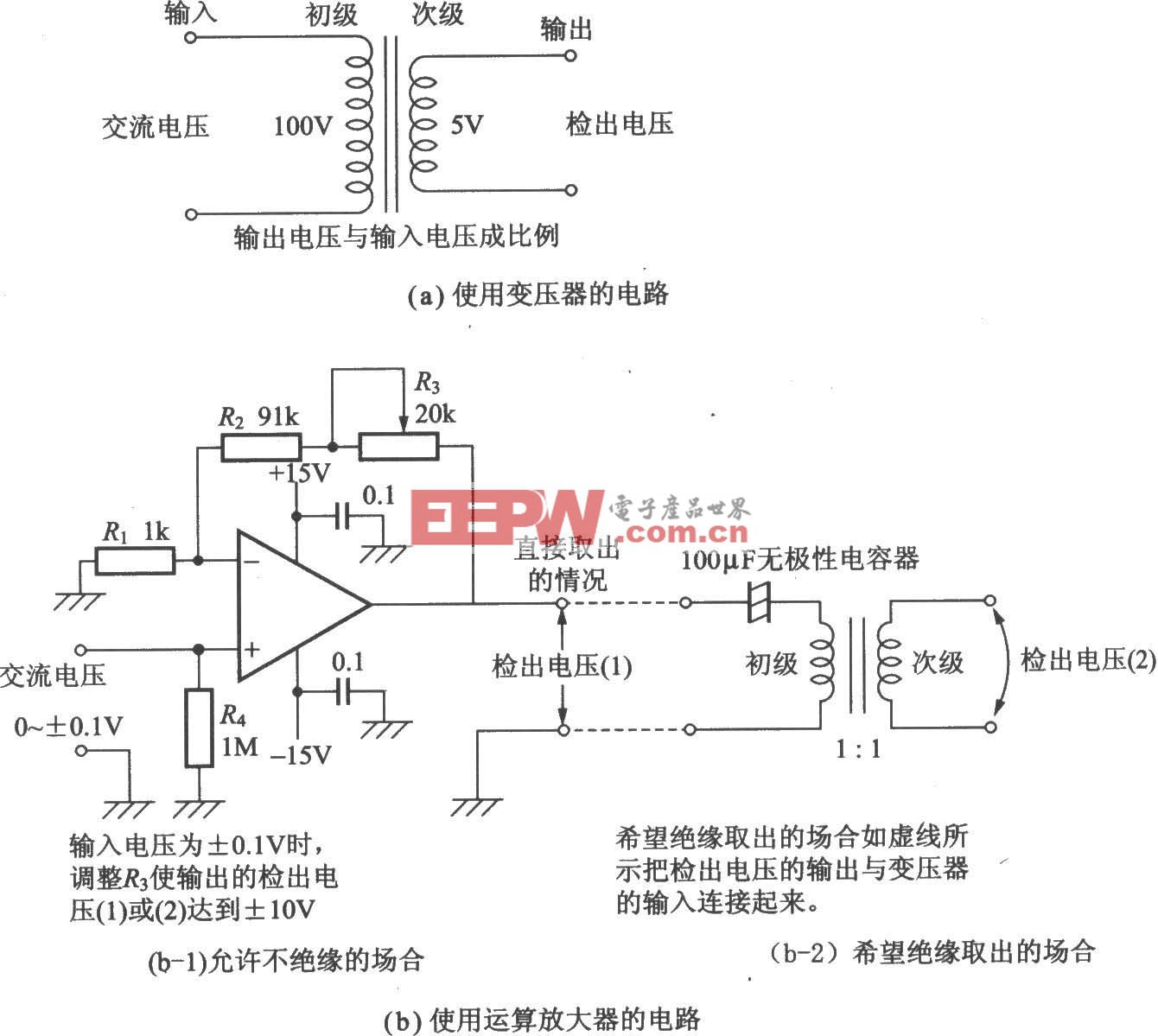

在许多过程控制应用中,需要在控制器与受控单元之间提供一个隔离栅,以保护和隔离控制电路,防止危险的共模电压破坏电路。

ADI公司的iCoupler系列产品可隔离高于2.5 kV的电压。有关iCoupler产品的详情,请访问 www.analog.com/icouplers为了减少所需隔离器的数量,CLEAR等非关键信号可以连到GND;FAULT和SDO可以不连接,从而只需要隔离三个信号。不过请注意,FAULT或SDO引脚是访问AD5422的故障检测功能所必需的。

常见变化

图1所示电路的一个常见变化是使用 AD5422AD5420,它类似于AD5422,但只有一个电流输出。因此,其输出端没有OP184缓冲器配置。这种AD5420和AD5700 HART调制解调器电路详见CN-0270。电路笔记CN-0065提供有关IEC61000兼容解决方案的额外信息,该解决方案适合使用AD5422和ADuM1401数字隔离器的全隔离式输出模块。电路笔记CN-0233包含有关提供电源和数据隔离的信息,所使用的是ADuM3471 PWM控制器和具有四通道隔离器的变压器驱动器。

如果需要多个通道,可使用AD5755-1四通道电压和电流输出DAC。该产品具有创新型片内动态电源控制功能,在电流模式下,可以最大限度地降低封装功耗。各通道均有一个相应的CHARTx引脚, 因此HART信号可以耦合至AD5755-1的电流输出端。

电路评估与测试

要构建此电路, 需要使用 AD5422评估板 ( EVAL-AD5422EBZLFCSP P版本)和 AD5700-1评估板 (EVAL-AD5700-1EBZ)1EBZ),参见图11。除了这两个评估板之外,该电路还需要三个外部电容(C1、CH和CL)、一个电阻(RH)、一个负载电阻(RL)、一个缓冲放大器以及一个UART接口。

设备要求 需要以下设备:

· AD5422 评估板( EVAL-AD5422EBZ LFCSP版本)

· AD5700 评估板( EVAL-AD5700-1EBZ)

· 运行Windows® XP的PC,带USB端口

· 主机控制器和UART接口(标准微控制器, 例如 ADuC7060)

· 10.8 V至60 V的电源

· 数字测试滤波器(HCF_TOOL-31,可从HART通信基金会获得)

· 500Ω负载电阻

· OP184 放大器(位于单独的试验板上且带有连接线)

· 外部电容C1 (4.7 nF)、CH (8.2 nF)和CL (4.7 nF);电阻RH (27 kΩ)

· Tektronix DS1012B示波器或等同产品

图11. 测试设置框图

静默期间噪声测量 AD5422 LFCSP

如前文所述,对于静默测试期间的输出噪声,AD5700调制解调器并未在发射数据(静默)。AD5422设置为输出所需的电流并通过HART通信基金会带通滤波器。接着使用Tektronix TDS1012B示波器测量输出噪声;结果显示输出噪声在HART通信基金会协议规范要求的范围内。

模拟变化率测量 — AD5422 LFCSP

模拟变化率规范可确保当AD5422调节电流时,模拟电流的最大变化率不会干扰HART通信。电流的阶跃变化会扰乱HART信号。为进行这个测试,AD5422被编程为输出一个4 mA至20 mA切换的周期波形,该波形在两个值上都没有延迟,以获得最大变化率。所用的压摆率设置为SR时钟= 3和SR阶跃= 2,C1设置为4.7 nF,C2保持开路。

此外,再将SR时钟设置改变为5而不是3,并保持其它所有设置和元件值不变,从而进一步降低压摆率,由此另外进行测量;至于相关影响,可比较图9和图10来得出。

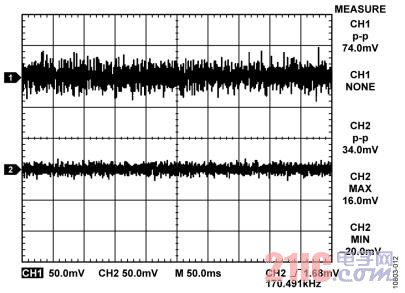

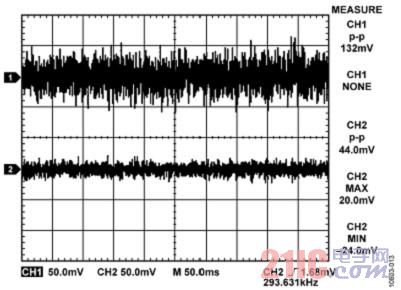

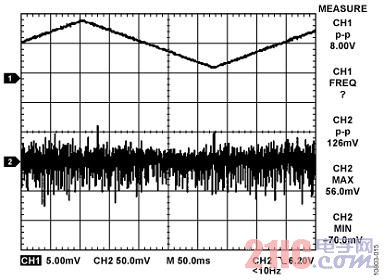

静默期间噪声测量 —AD5422 TSSOP

另外还执行了额外测量,以模拟AD5422 TSSOP封装选项在这种配置下的表现;不过,没有连接在CAP1引脚的电容(C1)(因为此器件的TSSOP版本没有CAP1引脚)。

虽然与有C1的LFCSP器件相比,没有C1时测得的静默期间输出噪声值更大,但还是在HART通信基金会协议规范要求的范围内。图12和图13中的通道2显示了有HCF_TOOL-31滤波器时的宽带噪声,IOUT为4 mA时结果为530μV rms,IOUT为12 mA时结果为690μV rms。可将这些曲线图与图7及图8进行比较,以体现有无C1的影响如何。

图12. 无C1且输出电流为4 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

图13. 无C1且输出电流为12 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

模拟变化率测量 — AD5422 TSSOP

从模拟变化率测试的角度来看,无论有无C1,最大峰值结果都相似。主要区别在于,没有C1时,峰峰值本底噪声要大得多。图14和图15分别是压摆率为120 ms(SR时钟= 3和SR阶跃= 2)和240 ms(SR时钟= 5和SR阶跃= 2)时的模拟变化率曲线图。

图14. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 3,SR阶跃= 2,C1 = NC,C2 = NC

图15. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 5,SR阶跃= 2,C1 = NC,C2 = NC

同样,可将这些曲线图与图9及图10进行比较,以体现有无C1的影响如何。虽然这种电路配置中所用的HART耦合技术要求采用外部RSET电阻,但请注意,即使该电路的HART部分未实施,添加缓冲器也会在使用内部RSET电阻时造成IOUT精度略微降低。因此,在使用这种缓冲器配置将电压和电流输出引脚连接在一起时,建议使用外部RSET电阻。

评论