高速信号采集记录仪设计

摘要:针对高速信号实时采集存储的需求,设计了一种高速信号采集记录仪。记录仪通过高速A/D转换器对信号进行采样,并实时存入NAND FLASH存储阵列中。为提高数据存储速率,综合采用并行总线、交错双平面页编程、多级流水线等技术,大幅提升FLASH的写入速度。记录仪可实现8bit、200MSPS的采样速率,并可将速率为200MB/s的采样数据实时存储。

本文引用地址:https://www.eepw.com.cn/article/201610/306117.htm0 引言

目前在各工业领域对数据采集存储的需求越来越多,对采集速率和存储速率的要求也越来越高。特别是在航空航天领域,经常要对高速信号进行采集,并将采集数据实时存储在非易失存储器之中,以便事后分析处理。

为满足需求,本文提出一种高速信号采集记录仪的设计方法。采用高速A/D转换器对输入信号进行200MSPS的高速采样,然后将采样数据实时存入 FLASH存储阵列中。综合采用了并行总线、交错双平面页编程、多级流水线等技术,大幅提升FLASH的写入速度,从而实现200MB/s采样数据的实时存储记录。

1 系统组成及工作原理

1.1 记录仪系统组成

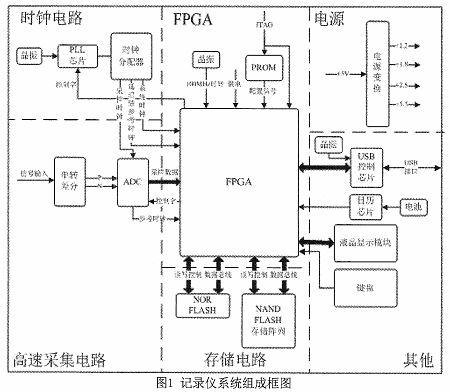

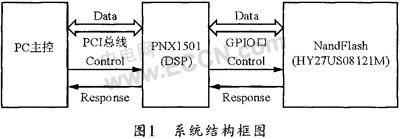

图1为记录仪系统组成框图,记录仪电路系统主要由FPGA电路、时钟电路、高速采集电路、高速存储电路、电源电路、其他外围电路等组成。

PGA选用Xilinx公司的XC4VSX55,PLL时钟芯片选用TI公司CDCF5801A,A/D转换器选用TI公司ADS5547,NAND FLASH存储芯片选用三星公司K9WAG08U1A,USB控制芯片选用CYPR ESS公司CY7C68013A。

1. 2 记录仪工作原理

系统的工作原理为:上电后,FPGA首先读取NOR FLASH中存储的NAND FLASH坏块信息,在内部RAM中建立坏块表,之后每次需要对NAND FLASH进行读写操作之前,都要先查询坏块表,若准备操作的块为坏块,则跳到下一块继续查询,直到找到好块才进行操作。

当需要采集记录信号时,先通过外接的键盘和LCD显示模块设置采样参数。然后记录仪接收到启动信号后开始进行采样记录,需采样信号从SMA接口输入后经过差分放大器转换为差分信号,然后进入A/D转换器进行200MSPS采样,FPGA接收采样数据,采样4级流水线对NAND FLASH存储阵列进行写入操作。此外FPGA还需完成对其他外围器件的控制。

当需要上传数据时,FPGA将数据从NAND FLASH中读出,通过USB控制芯片将数据上传给上位机。

2 关键技术

2.1 高速A/D采样

记录仪采用的A/D转换器为TI公司的14bit、210MSPS的高速A/D芯片ADS5547。系统中实际采用的采样时钟频率为200MHz,由50MHz晶振时钟通过CDCF5801A倍频产生。

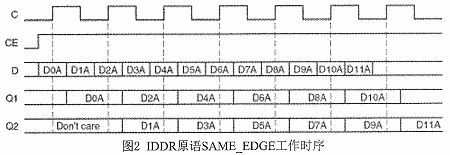

ADS5547采用的工作模式为LVDS DDR模式,即在A/D输出时钟的下降沿传输采样数据的奇位,在上升沿传输采样数据的偶位,所以实际数据传输频率为400MHz,对于这种高速数据传输,在PCB设计时需注意7对差分数据线和1对差分时钟线保持等长,确保迹线传输延时相同。

在FPGA数据接收模块的设计中,直接调用芯片中的IDDR原语,如图2所示,其在SAME EDGE工作模式下的时序正好匹配ADS5547的数据输出时序,所以可将7路DDR数据转换为14bit并行数据,考虑到NAND FLASH的写入速度,在存储时截取采样数据的高8位,这样需要存储数据的速率为200MR/s。

2.2 高速数据存储

记录仪采用的非易失存储器为三星公司的NANDFLASH芯片K9WAG8U1A,单片容量为2GB。由于单片FLASH的存储容量和写入速度有限,所以使用了16片FLASH成存储阵列,总容量为32GB,并综合采用了并行总线、交错双平面页编程、多级流水线等技术提升写入速度。

(1)并行总线

为了提升数据吞吐量,将N片FLASH芯片的I/O并行操作,总线宽度增加为单片的N倍,并共用读写控制线,这样可将N片FLASH当做一片大位宽 FLASH同时进行读写操作,从而可以将写入速度提升至N倍。在该记录仪中,是将8片FLASH的I/O并行操作,每片FLASH的数据位宽为8bit,所以总位宽为64bit,写入速率可提高为单片的8倍。平均数据写入周期只需达到40ns即可实现200MB/s的数据速率,满足FLASH的25ns最小写入周期要求。

(2)交错双平面页编程

NAND FLASH的写入操作是以页为单位进行的,称为页编程操作,分为两阶段进行。第一阶段为数据载入阶段,是将数据先写入到页寄存器中,第二阶段为编程阶段,是将数据从页寄存器中真正编程到FLASH的存储单元之中。数据载入页寄存器时最高速率可达到40MB/s(单片),但数据编程阶段所需时间为 200~700μs,若等待一页编程完成之后再进行下一页数据的载入会严重降低数据写入速率。为充分利用编程阶段的时间,并且增加数据载入时间以便于流水线操作,采用了交错双平面页编程方法。

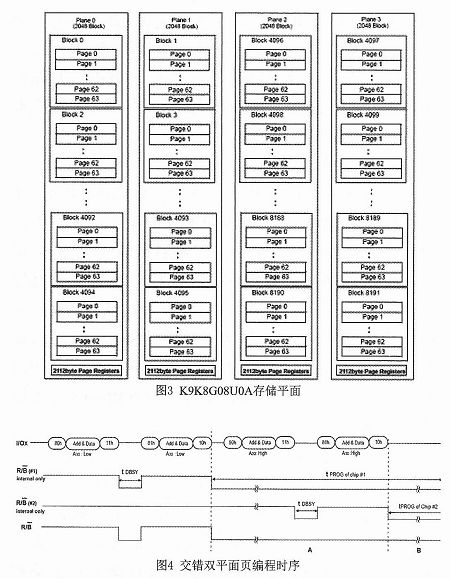

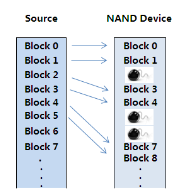

每片K9WAG08U1A实际上是由2片K9K8G08U0A组成,而每片K9K8G08U0A又由2片K9F4G08U0A组成,每片 K9F4G08U0A又由2个2Gb的存储平面组成,每个存储平面有独立的2112字节页寄存器,因此可实现双平面页编程操作,而2片 K9F4G08U0A之间可以实现交替操作。K9K8G08U0A存储平面如图3所示,Plane0和Plane1组成第1片 K9F4G08U0A,Plane2和Plane3组成第2片K9F4G08U0A。

当进行FLASH编程操作时,先发送双平面编程指令,然后Plane0和Plane1进行数据载入,载入完成后进入编程阶段。此时无需等待编程结束,直接对Plane2和Plane3继续进行数据载入,即可实现交错双平面页编程。操作时序如图4所示。

(3)多级流水线

运用交错双平面页编程方式后,可以连续进行4页的数据载入操作,但载入完成后整片K9WAG08U1A的4个平面都将进入编程阶段,无法继续进行操作。为了实现数据的连续载入,采用了多级流水线技术。

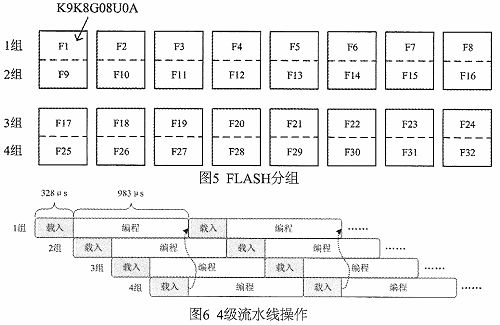

实现流水线操作首先要对FLASH存储阵列进行分组。由于每片FLASH是由2片K9K8G08U0A组成,所以存储阵列可以看作由32片K9K8G08U0A组成,把每8片K9K8G08U0A分为一组,在读写时并行操作,这样整个存储阵列分为四组,如图5所示。

流水线操作方法如图6所示。FLASH进行写入时,首先通过片选信号选中第1组FLASH,进行数据载入操作,载入完成后,该组FLASH进入编程阶段,此时切换片选信号,选中第2组FLASH,继续进行数据载入,依此类推。由于采用了交错双平面页编程方式,所以每个载入过程可以载入4页的数据,而采用并行总线之后,位宽为64bit,即每个写周期可写入8Bytes的数据,按照200MB/s的数据速率计算,每个载入阶段的时间为:

当第4组FLASH的载入过程完成后,距离第1组FLASH开始编程时已过去983μs,大于最长编程时间700μs,所以第1组可继续开始数据载入操作。通过流水线操作,实现了数据的连续载入,从而大幅提高了写入速度,实现了200MB/s的数据存储速率。

3 试验验证

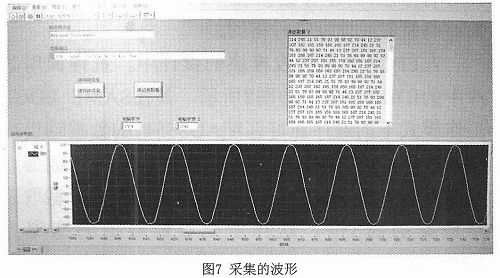

为验证记录仪的性能,进行了数据采集试验。试验中采用信号发生器产生周期为100ns的正弦信号输入记录仪,记录仪对其进行实时采集存储,采集时间为 5s,即产生的数据量为1GB。采集完成后,在上位机软件中发出上传指令读取FLASH中的数据,并通过USB接口上传到上位机形成二进制数据文件。然后截取其中的一段波形进行显示,如图7所示。

在图中可以看到,正弦信号的每个周期对应20个点,而采样周期为5ns,所以20个点为100ns,与设置的信号周期相一致,说明记录仪实现了200MSPS的采样速率和200MB/s的数据存储速率。

4 结论

设计了一种高速信号采集记录仪,该记录仪可 实现8bit,200MSPS的采样率,并可对采样数据实时存储。其电路系统可由单板实现,具有体积小,便于携带和应用的优点。该记录仪适用于各种需要高速信号采集的场合,应用前景广泛。

评论