某型机载作战任务加载器的设计与实现

摘要:为了保证飞机作战任务信息传输和传递的准确性和安全性,并考虑数据加载的方便快捷,文章提出了一种采用DSP实现安全可靠加载任务数据的解决方案。设计方案采用USB标准线性FLASH存储卡作为任务数据加密存储和传递载体,在飞机座舱操纵台安装一个集成USB存储卡,集数据读取解密和1553B总线数据加载等功能为一体的作战任务加载器。文章从应用需求出发,对加载器的软硬件设计与实现方法进行了较为详尽的描述。此作战任务加载器的应用丰富了任务数据的加载方式,减少了飞行员的操作,并能保证作战任务数据的可靠传输。

本文引用地址:https://www.eepw.com.cn/article/201609/303565.htm引言

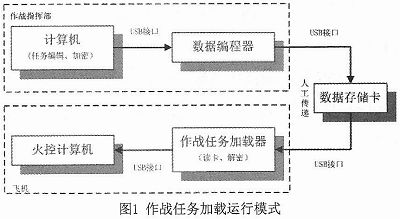

军用飞机作战任务具有较高的保密要求,飞行员需要从作战指挥部获取作战任务数据,然后在飞机执行任务起飞前将作战任务相关参数通过数据加载设备传输到火控计算机中。火控系统根据装订的信息参数引导飞行,在载机到达程序装订的目标区域时提醒飞行员做好战斗准备,此外攻击后的退出引导、返场引导等飞行过程都可根据装订的信息自动完成。作战任务加载运行模式如图1所示。

1 整体方案考虑

作战任务加载器需要实现三个功能,包括读取数据存储卡的数据、数据解密和通过1553B接口向火控计算机发送数据。

数据存储卡用于存储和传递作战导航数据,任务规划系统对数据存储卡执行编程操作,作战任务加载器对数据存储卡执行读取操作。作战任务加载器属于小型机载嵌入式设备,其工作频率较低,数据存储卡应选择工作模式相对简单、读取速度快、可靠性较高的产品。作战任务加载器采用基于USB接口的NOR Flash存储卡作为作战导航参数信息的存储载体。NOR Flash也称为Linear Flash,拥有独立的数据总线和地址总线,能快速随机读取,可以单字节/单字编程,但必须以块为单位或整片执行擦除,重新编程之前必须进行擦除操作。 NOR Flash存储卡简单的访问方式、快速读取速度及较高的可靠性适合机载作战任务加载器的工作环境和工作模式。

作战任务编程/加载系统采用数据加解密技术保证移动存储的安全保密性。所谓数据加密技术是指将信息(或称明文)经过加密钥匙及加密函数转换,变成无意义的密文,而接收方将此密文经过解密函数、解密钥匙还原成明文的技术。作战导航参数信息需要任务规划系统进行数据加密后存储在数据存储卡上,作战任务加载器对数据存储卡上的密文数据进行解密处理。作战任务加载器固定安装在飞机上,应用环境具有较高的安全性。考虑作战任务加载器的实时性要求较低,且需要解密的导航信息数据量较小,加载器采用软件解密方法即可满足要求。虽然会带来软件运行开销,但可降低硬件成本。

本系统采用IDEA(International Data Encryption Algorithm)加密算法实现作战导航数据信息在数据生成端的加密和数据使用端的解密。IDEA被认为是目前世界上最好最安全的分组密码算法,且对计算机功能要求不高。IDEA的密钥长度是128位,相对较长,加密强度高。在穷举攻击的情况下,IDEA需要经过2128次加密才能恢复出密钥,假设芯片每秒能检测10亿个密钥,需要1013年,它被认为仅循环4次即可抵制差分密码分析,对IDEA算法也不起作用,随机选择密钥基本没有危险,故其安全性较高;算法的基础是16位运算,实现速度与DES相同。加密中从数码锁获得的密钥为128比特,明文分组长度是64比特。

采用DSP实现IDEA解密算法与硬件实现解密相比具有开发周期短、成本低的优点。另外DSP本身的流水线和运算器设计也能够有效提高数据解密算法的运算速度。

2 硬件设计

作战任务加载器由数据处理模块、电源系统、机箱和数据存储卡构成,机箱和电源采用一体化设计,数据处理模块是作战任务加载器内部唯一的SRU。数据存储卡直接安装在数据处理模块上,可简化整机结构设计。

2.1 DSP选型

数据处理模块采用TI公司的数字信号处理器SM320F2812,集成1553B、USB、串口、离散量等数字接口。1553B接口用于向火控系统传输数据,USB接口用于访问数据存储卡,串口用于显示维护BIT的测试结果,离散量用于控制作战任务加载器进入不同的工作模式。SM320F2812的额定工作频率为150MHz,每秒可执行1.5亿次指令,具有单周期32bit ×32bit的乘和累加操作功能,主要实现USB存储卡数据读取、解密、发送的功能。

F2812的外部接口映射到5块固定的存储空间。每个存储空间可以单独设置访问时的等待状态数目、选通信号的建立时间和保持时序,且读和写操作的时序可以独立设置。此外,每个空间可以分别选择是否使用外部等待信号(XREADY)来扩展所需的等待状态。这些片选信号以及可编程的等待状态和选通时序使得 DSP芯片可以和许多外部存储器或扩展外设间实现无缝接口。每个XINTF空间都有自己的时序寄存器XTIMING,改变时序寄存器的值将会影响相应空间的访问时序。1553B接口、RAM、数据存储卡可分别映射到不同的存储空间,实现简化设计。

2.2 1553B总线接口电路

作战任务加载器与火控计算机之间的数据传输通过1553B总线接口实现。本设计选择1553B接口芯片HK1553B来实现通信功能。

1553B总线接口电路工作时钟为12MHz,经过隔离变压器连接到1553B总线,模块上1553B芯片工作在RT方式下,1553B协议芯片访问外部存储器为一片64k×16bitSRAM存储器,存储器的访问控制及1553B协议芯片请求DSP总线及应答信号由FPGA产生。1553B协议芯片的地址和数据总线全部引入FPGA,1553B协议芯片访问DSP总线时地址数据通过FPGA挂在EMIF总线上。

2.3 USB接口电路

本系统采用的存储卡为MagicRAM公司的USBFlash存储卡,该存储卡读取周期最大为200ns,可执行100000次写/擦除操作。该存储卡的读写访问时序是典型的异步并行接口访问时序。DSP提供了对异步存储器的无缝访问接口XINTF,将数据存储卡单独映射到DSP的 Zone2外部存储空间。

USB芯片CY7C68013与FPGA相连,在检测到USB供电后,通过FPGA实现对USB接口芯片的复位,并使能USB接口信号,实现与上位机的通信,完成调试加载功能。USB接口部分结构如图2所示。

评论