基于1553B总线远程终端的FPGA程序设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/201609/303476.htm1553B总线是MIL-STD-1553美国军用标准总线的简称,在飞机的航电系统中应用广泛.为了提高可靠性,1553B 总线一般采用双余度总线结构,在1553B 总线上可挂接三种终端类型:总线控制器(BC).远程终端(RT)和总线监视器(BM).总线网络上可挂接32 个终端,在这32 个终端中,远程终端的数量往往最多.目前,为实现1553B 总线通信,大都是开发独立的通信接口模块,不但成本高,整个系统的重量也会因此增加,不利于航空领域的使用.随着电子技术的发展,FPGA已经迅速应用于各个领域,系统中的各个电路模块大都包含FPGA 芯片.本文介绍一种使用FPGA 编程,实现1553B总线通信中远程终端的方法,本方法具有开发周期短.方法简单.可移植性强的特点,可大大降低系统的开发成本,缩短开发周期.

1 1553B总线简介

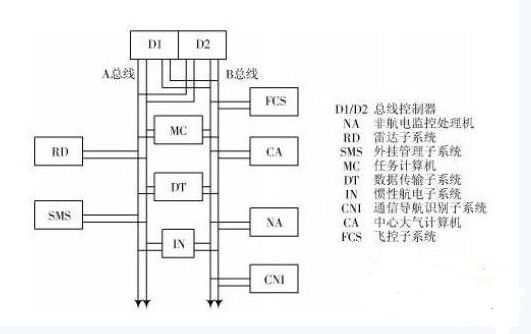

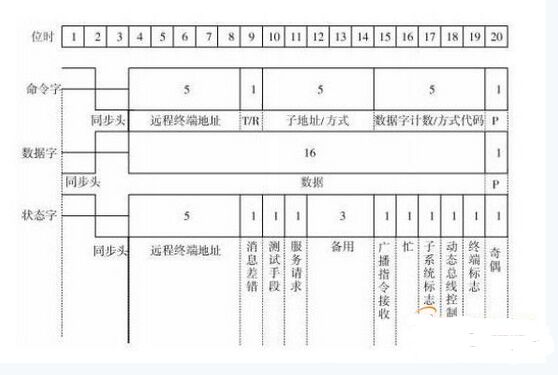

现代飞机典型的航电系统及1553B 总线应用框图如图1所示.1553B总线采用指令/ 响应型通信协议,构成1553B 总线传输协议有三要素:命令字.数据字和状态字,每个字的长度为20 b,且由3部分组成:同步头(3 b).数据段(16 b)和奇偶位(1 b),如图2所示.

命令字由总线控制器(BC)发出,共包含20位的长度,前3位是同步头,最后一位是奇偶校验位,有效信息为16位,有效信息位中,前5位为RT 的地址场,该场指出了被寻址的终端地址.有1位是发送/接收(T/R)位,当此位为“1”时,命令被寻址的终端发送消息,为“0”时,则命令被寻址的终端接收消息.另外5位为子地址/方式代码场,一般情况下,按指示向被寻址终端某一个分地址进行通信,当这5位全为“0”或全为“1”时定义为方式代码场.有效信息中的最后5位为计数/方式码场,通常情况下,它定义了与该指令相关的数据字数,但在前5位为方式场时,它就成了方式控制码.

数据字有20 位长,其中16 位有效信息是总线上传输的数据信息.

状态字仅仅对指令字响应,被寻址的远程终端发出,并包括5位本RT地址场和8位指示了通信状态和本RT及子系统状态的信息位.

2 硬件构成

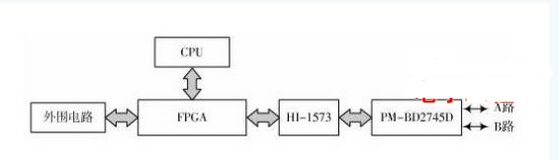

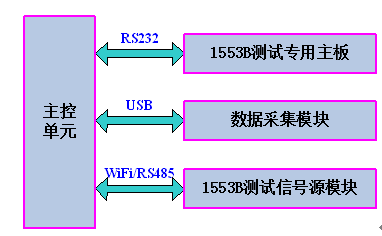

信号调制解调所需的隔离变压器和收发器需单独购买,本文采用HOLT 公司的PM-DB2745D 芯片和HI-

1573 芯片,从而曼彻斯特编码解码往后的部分都可以在一片FPGA芯片内实现.本文是将1553B总线的远程终端集成到海军某型号飞机航电子系统的一块计算机板上,计算机板采用的是Altera 公司的Cyclone Ⅲ系列FPGA芯片,硬件连接关系如图3所示.

3 FPGA内部模块构成

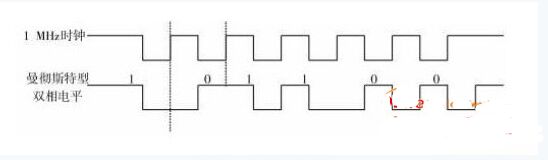

远程终端是用户子系统到数据总线上的接口,它在BC 的控制下提取或吸收数据,总线上的位传输速率为1.0 Mb/s,信号以串行数字脉冲调制方式在数据总线上传输,传输的数据码为曼彻斯特Ⅱ型双电平编码,逻辑1为双极编码信号1/0(即一个正脉冲继之以一个负脉冲),逻辑0 为双极编码信号0/1(即一个负脉冲继之以一个正脉冲),过零跳变发生在每一位时的中点,如图4所示.

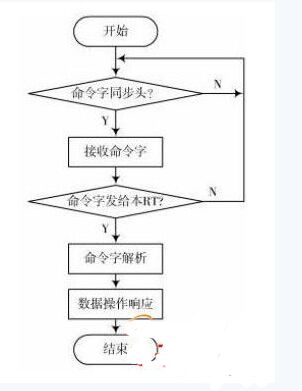

总线系统中传输的消息格式有10种,本文涉及到的有三种消息传输方式,即总线控制器向远程终端的传输.远程终端向总线控制器的传输和远程终端向远程终端的传输.FPGA的主要编程思路如图5所示.

实际编程时,对1553B总线数据的解析响应在数据解析模块.数据编码模块.主控模块和软件接口模块的协调工作下完成,FPGA 内部各功能模块的联系如图6所示.

FPGA中各模块的详细功能详述如下:

(1)数据解析模块:本模块对总线上串行数字脉冲进行接收并解析,数据解析模块负责检测命令字.数据字.状态字的同步头,1553B 总线的每一条消息都是从命令字开始的,数据解析模块在检测到命令字同步头后,将同步头后边的16位有效信息进行串并转换,经过解析后,判定是否对该命令做出响应,若此命令是发给本RT终端的,则根据命令做出接收数据或发送数据的响应,若此命令不是发给本RT 终端的,则不做出任何响应.

(2)数据编码模块:本模块在接收到数据发送命令时进行工作,主要完成对发送数据的曼彻斯特Ⅱ型双电平编码.

(3)主控模块:本模块控制各模块协调工作,为各模块提供正常工作的时钟信号,当数据解析模块接收到的是接收数据命令时,将数据解析模块解析得到的数据字存储到一个双口RAM中,记为RAM1,等待CPU前来读取,RAM1 被划分为32 个区域,对应此RT 终端的32 个子地址;当数据解析模块接收到的是发送数据命令时,将CPU事先存储在另一个双口RAM中的数据发送给数据编码模块,此双口RAM 记为RAM0?RAM0 同样被划分为32个区域,对应RT终端的32个子地址.

(4)软件接口模块:本模块是与CPU 通信的接口,当RAM1中某个区域存储新的数据时,通知软件前来读取,当软件向RAM0中某个区域写入数据后,通知FPGA软件写入数据完毕.

4 试验

试验时,将程序下载至FPGA中,使用Quartus Ⅱ软件自带的逻辑分析仪观察FPGA的通信性能,采用上海旋极公司提供的成品1553B 板卡和配套测试软件与本文开发的电路进行通信,试验证实:两者通信结果正确无误,满足1553B总线通信要求,其中,A路总线接收数据的逻辑关系如图7所示.

评论