Nios软核在CT机扫描系统控制器设计中的应用

1 引言

本文引用地址:https://www.eepw.com.cn/article/199820.htm近年来,可编程逻辑器件的发展,使得SOPC (System On A Programmable Chip,可编程片上系统)成为可能, 即在一块可编程芯片上实现整个系统。Nios是Altera公司研发的可用于SOPC设计的处理器软核。基于Nios软核的SOPC系统,其最大特点就是灵活,能根据自己的需要灵活改动Nios的外围设备,使得硬件利用效率达到最高,同时他具有ISP(In System Programmable,在系统编程)的功能,可裁减,可扩充,可升级。本文充分利用了Nios系统灵活制定的好处,设计实现了一套CT机扫描系统控制器。

2 CT扫描系统控制器

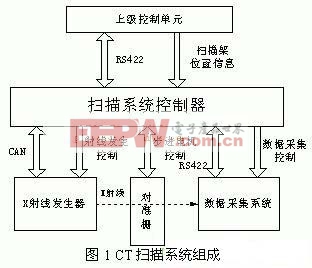

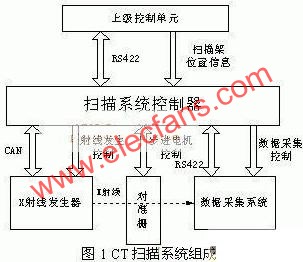

CT机是根据不同密度和厚度的物体对X射线的吸收程度不同的原理,通过计算机成像技术,对病人身体成像的一种医学设备。CT机扫描系统由X射线发生系统,数据采集系统,对准栅三个子系统组成,如图1所示。扫描系统由扫描架承载,扫描架是个旋转体,扫描系统随着扫描架旋转,以获得不同角度下的人体信息,扫描架旋转一周所得数据可产生图像。

扫描系统的三部分中,X射线发生系统产生射线,扫描系统控制器通过CAN总 线和他通信,发送X射线参数和动作指令,同时接收X射线发生器的状态信息。数据采集系统负责对X射线采样和传输数据,他扫描系统控制器采用RS422总线和其通信,发送控制指令,并接收指令执行状态。同时有IO接口用作采样触发脉冲和采样使能。对准栅通过挡板来调节X射线的开口宽度,挡板由一个步进电机驱动。扫描系统控制器接收来自上级的开口宽度指令,然后发出控制脉冲,控制步进电机到达指定位置,通过编码器接收步进电机转子位置信号,形成闭环。

CT扫描系统控制器负责三个子系统的协调控制,为扫描系统中设备的通信中心和控制中心。首先他和上级控制单元通信,接收指令和汇报各子系统状态,其次和各子系统通信,发送控制指令,并接收子系统的状态信息。他根据接收到的控制指令和扫描架的位置信息,控制对准栅到达指定宽度,产生控制X射线发生和采样的时序。可见,CT扫描系统控制器包括了实时通信、电机控制,时序控制,是个多任务的系统。并且对实时性需求也非常高,所有一点时序发生偏差,都会对病人造成不必要的伤害。

本文使用SOPC的方式,设计了以一片FPGA为核心的CT机扫描系统控制器硬件,制定了基于Nios软核的FPGA系统,然后设计了基于实时操作系统Nucleus的应用软件,实现了CT机扫描系统控制器的上述功能。

3 基于Nios的硬件设计

本文使用了Altera 公司的FPGA Cyclone EP1C20,他拥有充足的可编程资源来实现SOPC。因为系统所有功能均由FPGA实现,硬件电路除FPGA外只需加上存储器件和一些物理层接口芯片即可。本文使用了一片8M Byte FLASH、一片16M Byte SDRAM,CAN总线收发器和RS422总线收发器等作为FPGA的外围设备,硬件电路的结构简单明了,提高了系统的可靠性。FPGA系统运行时钟50MHz,确保了系统的运算速度。

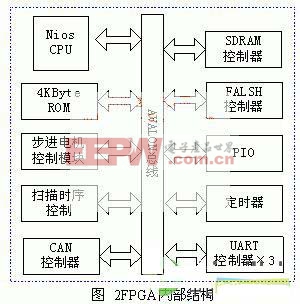

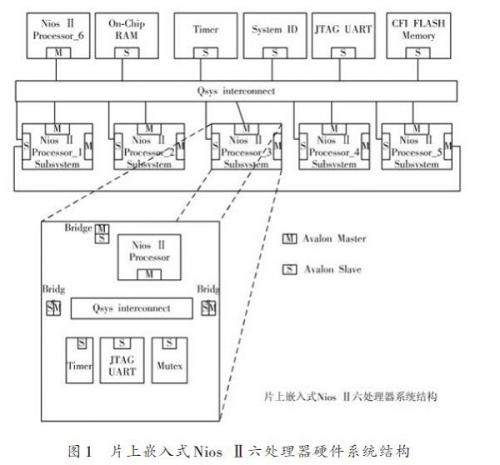

通过Altera的SOPC Builder软件包能制定基于Nios软核的FPGA系统,他提供了一些基本的Nios外设模块,如UART控制器、定时器、FLASH控制器、SDRAM控制器等。本文设计的CT扫描系统控制器FPGA内部结构如图2所示。

Nios是流水线结构的RISC 软核处理器,他能选择32位架构或16位架构。本文使用32位架构,并在SOPC Builder中设置了4K Byte数据缓存和指令缓存,以节省CPU读取数据和指令的时间,提高系统性能。

由图2可见,Nios软核通过AVALON总线和各扩展模块相连接。AVALON总线是专门用于Nios连接外设的一种总线结构,他具有分离的地址,数据和控制线,并提供动态动态总线宽度调整等功能。Nios软核为其主设备。

AVALON总线上的从设备有SDRAM控制器,Flash控制器、定时器、通信接口UART控制器和CAN 控制器。在设计Nios软核的外设时,采用已有的IP核能有效缩短设计周期,同时经过充分验证的IP核也确保了设计的可靠性。本文根据需要采用了三个UART控制器作为Nios软核的外设,分别用于和上级单元通信、和数据采集系统通信和调试信息输出;还使用了CAST公司的IP 核作CAN 控制器,他支持CAN 2.0协议。

在FPGA片内,使用了4 Kbyte的ROM,此ROM中包含了Altera提供的GERMS Monitor启动引导程式,他能实现启动引导、程式下载和基本调试功能。在调试中,通过调试串口和GERMS Monitor通信,将可执行的映象文件下载到SDRAM或FLASH中。

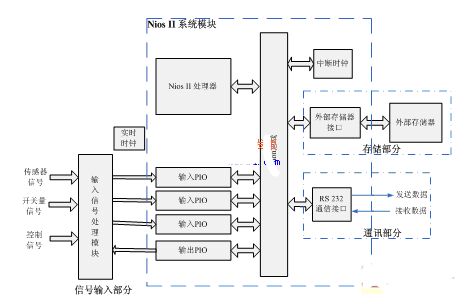

另外,本文根据应用的特别需求设计了自定义模块??扫描时序控制模块和步进电机控制模块。在SOPC系统中,更容易选择系统功能是由运行于Nios中的软件实现,还是使用FPGA硬件实现,由此能均衡系统软硬件的功能,使效率达到最高。系统功能用FPGA硬件实现的优势在于数据的并行处理,实时响应非常快;而用处理器软件实现的优势在于通讯和复杂情况的判断等。本文中为了提高系统的实时性,将步进电机控制在FPGA中实现。步进电机控制FPGA模块如图3所示。

图3右边为AVALON总线接口,由片选,地址线、数据线、读写使能和中断信号组成。左边为FPGA的输出,即和步进电机驱动器接口:DIR为步进电机运行方向控制,Pulse为步进电机的控制脉冲,HOFF为保持信号。下方三个信号为编码器的反馈信号,分别是A相脉冲、B相脉冲和初始位置信号。步进电机控制模块接收Nios通过AVALON总线发送来的目标位置信息,然后根据当前位置及目标位置,得到到达目标所需的步进电机的脉冲数,发出相应的脉冲。同时,根据反馈的编码器信号,解码得到电机当前位置信息,并判断步进电机运动是否达到目标位置,控制任务是否完成。然后产生中断,通知 Nios软核任务完成情况。可见运行于Nios中的软件只需将目标位置通知电机控制模块即可,大大减轻了CPU的负担。

评论