基于eRM建立自动化的验证平台

摘要:为了缩短SoC项目开发中前端验证的时间,实现自动化的可重用性验证环境平台,采用了eRM验证方法学,通过Sequence,BFM,Moni-tor,Scoreboard,Coverage等验证组件来实现此验证平台,并给出了基于此平台的一个应用实例,极大地提高了验证的效率和功能覆盖率。

关键词:验证时间;eRM;eVC验证平台;随机测试

集成电路已进入高速发展的阶段,半导体制造商极为成功的实现了摩尔定律的预期发展速度,为了缩短芯片上市时间,验证工程师必须保证芯片在流片前能得到很完备的验证。为了使日益复杂的项目达到理想的功能覆盖率,验证面临着巨大的挑战。eRM是一种基于e语言的验证方法学,通过Sequence,Bfm,Mkmitor,Scoreboard,Coverage等验证组件建立验证平台,可以对芯片进行Direct,Random等测试,并且可以很好地统计功能覆盖率,极大地据高了验证效率和生产率。

1 常用验证方法

从一个设计的功能验证来看,仅通过模块的接口界面(输入/输出信号端口)就完全可以验证器件的行为以及其实现的所有功能,否则该器件的属性就是不可控制的或是不可预测的。功能验证一般通过以下3种方法:黑盒法、白盒法、灰盒法。

黑盒法是指验证人员不需要用关心设计内部是如何实现的,所有的验证都可以通过接口完成,无需直接访问设计的内部状态。白盒法是是对设计的内部结构和实现具有完全的预测和控制能力,根据验证功能点可以迅速设置感兴趣的状态和输入激励,但不具备重用性。而灰盒法是介于二者之间,既有基于界面的验证组件,也有对内部状态控制和检查的组件,为提高验证效率和重用性,一般采用灰盒法。

2 eRM验证方法学

eRM验证方法学采用的是e验证语言,利用了e语言中的测试激励的生成、激励数据的驱动、输出结果的采样、输出响应的检查、功能覆盖率分析等组件,降低了验证过程中的人工干预,提高了验证的生产率。

2.1 eVC验证平台

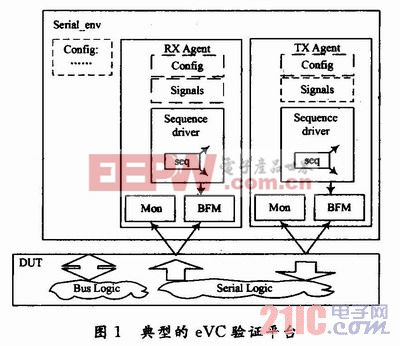

eVC(e Verification Component)是基于eRM方法学的验证环境韵通称,eVC包括所有相关的验证组件,从编写测试激励到功能覆盖率的收集,从模块验证到系统验证,都可以通过eVC来实现。为了提高验证效率,验证人员都都会开发一个黄金eVC,在实际项目中只需要根据实际协议扩展该黄金eVC即可,在验证环境开发前期,节省了大量的代码。典型的eVC验证结构如图1所示。Agent是验证环境中最主要的验证组件,所有的验证组件一般都在Agent里例化,验证环境中的Agent一般相当于设计中的实体(由VHDL实现的设计)或输入输出信号端口(由Veri-log实现的设计)。在图1所示的eVC里,有2个Agent,RX Agent是从DUT信号端口收集数据,而TX Agent是指向DUT的信号端口发送数据。并且每个Agent都是按eRM方法学中的标准方式来构建的,Agent里一般包括以下组件:

Config:包括Agent的属性和行为,主要配置Agent的数量及其主动或被动的属性,一般由验证人员自主定义的。

Signals:该组件中定义了一些DUT的信号端口,验证环境通过这些端口可以访问DUT内部的所有信号。一般情况下,这些信号是以string类型来定义,并在信号前加sig_前缀,利用hdl_path()函数指定与其相连接的DUT信号。

Sequence:是指验证人员希望加载到DUT的数据流,利用sequence既可以定义不加任何约束的随机数据,也可以是某些特定的数据流。

Sequence Driver:此组件是连接BFM和sequence的纽带,将sequence生成的数据流发送到bfm,但不是直接驱动到DUT信号上,而是将数据打包为一个列表,然后由BFM加载到DUT中。

BFM:总线功能模型,该组件只能在Agent里例化,从图1中可以看出,BFM具有双端通道,不仅将Sequence Driver中传递的数据流加载到DUT的信号端口,而且可以取样需要检测的信号,和一般总线的功能相似。

评论