isp1032E在高精度数据采集系统中的应用

引言

本文引用地址:https://www.eepw.com.cn/article/193672.htmisp在系统可编程技术是相对于以往可编程器件(PLD)实现逻辑设计时必须有专用的烧录器而言的,它不需要将isp器件拆上拆下即可实现对所需电路逻辑设计的反复设计和编程。这样就给系统设计研发、电路板调试和升级维护带来了极大的方便,从而缩短了系统的研发周期,实现了硬件电路的软件化设计。

相对于常用的PLD器件,isp器件具有体积小、容量大、编程方便、便于在线调试等优点,可实现较大规模的电路设计,且可实现编程加密。尤其在输入输出管脚众多的情况下,可以大大优化系统设计、节省系统空间。而相对于FPGA器件而言,isp器件的容量要小些,但其片内的逻辑一经加载就不会因掉电而再丢失。若要改变逻辑,只需通过下载电缆重新加载即可,而无需片外扩展EPROM存储电路的结构数据,因而电路实现更为方便简单。其实,这对于一般没有过于复杂的逻辑计算的电路设计,其容量一般已经足够。下面以

Lattice公司的isp1032E为例,介绍isp器件在高精度数据采集系统中的应用技术。

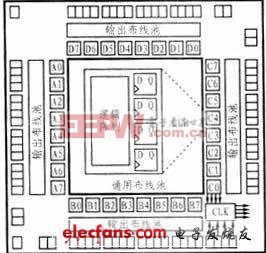

isp1032E的内部结构如图1所示。该器件有6000个门单元逻辑,192个寄存器单元,64个通用I/O,8个专用输入管脚,4个专用时钟输入,一个可提供上述各部分内部互连的集中连接池GRP。isp1032E的基本逻辑单元是万能逻辑块GLB,共32个,分别标定为A0~D7。每个GLB单元对应于18个输入单元、1个与或非逻辑阵列、4个输出单元。GLB的输入单元来自于GRP和专用输入;所有的输出单元都需进入GRP,以便于连接到其他的输入单元。

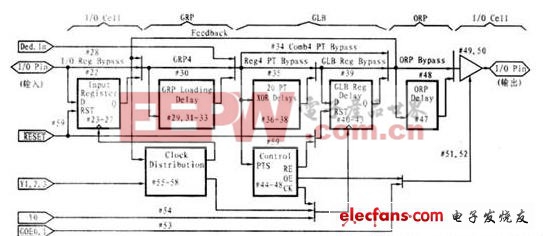

isp1032E的内部时序模型如图2所示。其中GOE0、GOE1为所有I/O单元的输出使能管脚。该管脚也可作为专用输入管脚来用。外部专用时钟输入管脚Y0与所有GLB单元的一个时钟输入脚相连;Y1进入时钟分配网络后可选择控制任何一个GLB单元的时钟输入;Y2进入时钟分配网络后可选择与任何一个GLB单元或I/O单元相连;Y3进入时钟分配网络后可选择与任何一个I/O单元相连。RESETj键可用于将所有的GLB单元或I/O寄存器单元复位。

图1

图2

2.2系统逻辑加载的硬件实现

在通过硬件加载系统逻辑时,首先用Lattice公司的专用编译软件ispDesignExpert生成所需的JED熔丝图文件,再通过专用下载软件ispVMSystem中的is-pDCD(ispDaisyChainDownload)将该JED熔丝图文件转换成isp流的形式,以便于利用PC机并口将所要生成的逻辑通过下载电缆烧录到相应的isp器件中。

图3

isp设备下载电缆的编程接口协议采用的是Lattice ISP协议或ispJTAG协议标准。ispLSI1000/E和2000系列、以及ispGDS和ispGAL系列都只能通过Lattice ISP接口来进行编程;而ispLSI2000V系列只能采用ispJTAG标准进行编程;其余的ispGDX、ispLSI3000和6000系列均可采用上述两种协议。

通过下载电缆实现上述过程的原理图如图3所示。需要特别注意的是:图中ispEN信号与地之间必须加入0.01μF的滤波电容,而且该电容与ISPEN脚的距离越近越好。这是因为在下载程序期间,is-pEN信号为低电平有效,这样就很容易受干扰而淹没本身很弱的有效信号。

3 软件流程

该数据采集系统的软件设计流程如图4所示。通常在设计软件时,图形输入方法与硬件语言描述方法有各自的优点。图形输入法比较简单明了,便于调试;而硬件描述语言在书写复杂电路设计中具有较大的优势。实际上,混合输入法兼有上面两种方法的优点,因而具有广泛的应用。

评论