数字基带传输系统的FPGA设计与实现

2.4 译码模块的仿真

根据图2所示,译码模块方框图在QuartusⅡ平台上用VHDL语言编程,经编译后可进行仿真。为了将译码结果与原始信号进行比较,将图3,图4的编码结果作为译码器的输入信号进行译码,将译码结果与以上的原始信号进行比较。

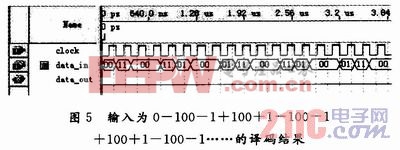

当输入的HDB3码为0-100-1+100+1-100-1+100+1-100-1+100+1……译码结果为全“0”码,如图5所示。图中clock为时钟信号,data_in为输入HDB3码,data_out为输出的信码。data_in为00,表示“0”电平;data_in为01,表示“+1”电平;data_in为11,表示“-1”电平。

将译码结果与编码前的原始信号做比较,可看出两者是一致的。本文引用地址:http://www.eepw.com.cn/article/191307.htm

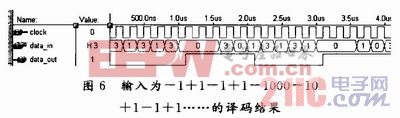

让输入信号data_in为31313000301313100010……,译码的结果为11111000001111100000……,如图6所示。

将译码结果与编码前的原始信号做比较,可看出两者仍是一致的。

3 数字基带系统设计与仿真

3.1 数字基带系统的设计

HDB3编译码数字基带系统的设计是在QuartusⅡ平台上,采用原理图的方式来实现的。首先,分别创建HDB3编码模块和译码模块符号文件;然后新建基带系统顶层文件;再在顶层文件中分别调入HDB3编码模块和译码模块符号文件;按要求连线后,即得到HDB3编译码数字基带系统电路。

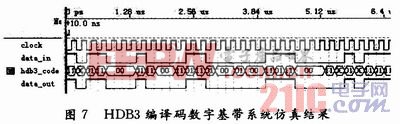

3.2 数字基带系统的仿真

将以上原理图进行编译后,即可进行仿真。使输入信码为10110001000011000000111000001011,系统传输结果如图7所示。图中,clock为时钟信号,data_in为输入信码,hdb3_code为系统传输用的HDB3码,da_ta_out为输出信码。由图可知,系统的输出与输入完全一致。

3.3 数字基带系统的调试

当整个系统通过程序仿真后,将程序下载到ACEX1K-EP1K30TC144-1芯片,从而完成整个数字基带系统的设计。调试时把发送部分与接收部分连接起来进行系统调试,检测各测试点信号是否正确,在调试中,硬软件要结合起来。由于芯片可以高度集成,问题一般出现在软件上,故在调试中软件参数的更改是最重要的。

4 结语

采用FPGA技术实现数字基带传输系统,包括编码器的设计与仿真、译码器的设计与仿真以及整个数字基带传输系统的设计与仿真。最后,在Altera公司的ACEX1K-EP1K30TC144-1芯片上加以实现。整个系统具有结构简单,性能稳定,有效性好,可靠性高等优点。除此之外,其优点还体现在设计者不受芯片结构的影响,避免了重复设计,缩短了开发周期;设计的模块化,提高了软硬件的组合度,使设计成果可以重复利用;在选择实现系统目标器件的类型、规模、硬件结构等方面,具有更大的自由度;总的设计方案和功能结构被确定后,就可以进行多人多任务的并行工作方式,扩大了设计规模,提高了设计效率。

评论