数字基带传输系统的FPGA设计与实现

2 编、译码模块的设计与仿真

编、译码模块的设计是在QuartusⅡ软件开发平台上,采用VHDL语言来实现的。

2.1 编码模块的设计

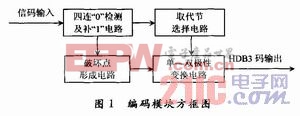

编码模块的方框图如图1所示。

四连“0”检测及补“1”电路 根据编码规则,当输入的信号遇到四连“0”码的时候,四连“0”码将由取代节“B00V”或者“000V”取代。因此,首先要检测出哪些是四连“0”码,哪些是非四连“0”码。在检测出四连“0”码后,还要将破坏脉冲V加入在第四个0的位置上。

取代节选择电路 当需要用取代节代替四连“0”码时,应判断采用哪一种取代节,即选择四连“0”码中第一个0码变为B码,还是变为0码。如果传号数为奇数,采用“000V”取代;如果传号数为偶数,则采用“B00V”取代。

破坏点形成电路 将补放的“1”码变成破坏点,使后续的V码与前面相邻的“1”码极性相同,破坏了交替反转的规律,形成了破坏点。

单—双极性变换电路 HDB3码极性形成电路有两个功能:一是正常传号“B”正负交替极性的形成;二是破坏点“V”脉冲的正负交替极性的形成,并输出HDB3码。

2.2 译码模块的设计

译码模块的方框图如图2所示。

破坏点检测电路 即找V码,在s消息的二进制代码中,若找出相邻两个同极性的码元,则可以确定后一个码元必为V码。

取代节去除电路 在V码出现时刻将信码流中的V码及其前面的第三位码置为“0”,即去掉取代节。

双—单极性变换电路 进行全波整流,将“+1”和“-1”还原为1。变换后的码元即为原信息码。

2.3 编码模块的仿真

根据图1所示的编码模块方框图在QuartusⅡ平台上用VHDL语言编程,编译通过后可进行仿真。

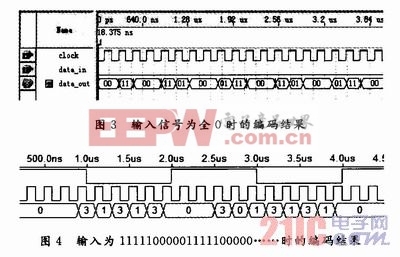

当输入信码为全“0”码时,编码结果为0-100-1+100+1-100-1+100+1……的序列,如图3所示。图中clock为时钟信号,data_in为输入信码,data_out为编码后的结果。data_out为00,表示“0”电平;data_out为01(十进制数字为1),表示“+1”电平;data_out为11(十进制数字为3),表示“-1”电平。

当输入信码为11111000001111100000……时,编码结果为-1+1-1+1-1000-10+1-1+1-1+1000+1……的序列,如图4所示。

由图3,图4可知,编码结果完全正确。

评论