增量设计流程针对需要变更部分进行优化

本文引用地址:http://www.eepw.com.cn/article/191195.htm

步骤四:在物理实现环节将更新的网表导入Libero

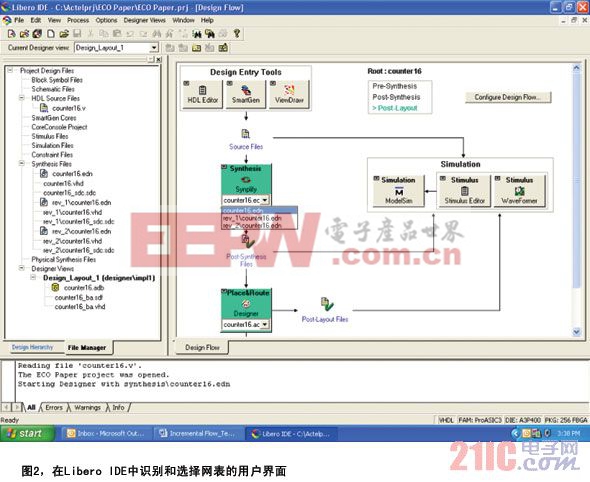

一旦Synplify Pro生成网表,就自动成为Libero IDE文档管理器的一部分,并且可用于布局布线 (即可被布局功能调用)。在设计流程和文档管理器与Libero之间的用户界面上,你很容易就找到和选出Synplify Pro创建的网表实现方案(参见图2)。

假设该网表是更新后的网表,包含设计和综合过程中产生的增量变更,你可能首先希望保护Libero的初始布局布线过程生成的原始布局。在Libero中,你可轻松地将原始布局保存为物理设计“View”(也叫做“implementation”) 文件,可按使用方便给该视图命名,比如命名为“Design_Layout_1”。Libero不会用更新的网表结果覆盖“Design_Layout_1”这个文件,它允许在同一项目中创建新的View。例如,可将名为“Design_Layout_2”的文件用于存放更新网表的实现和测试结果。这个功能使用户能够比较用Synplify Pro产生增量网表变化前后的结果。

接下来,在Libero中打开Actel的物理实现工具Designer,将更新的网表用新的实现方案名称导入Libero,并编译设计。编译设计后,在Libero的布局选项中完成设计布局。该菜单的缺省选项会对整个布局进行重新布局布线。对于包含经MultiPoint更新后的网表,Actel建议采用完全布局布线。完全布局布线的布局效率最高,但需要对所有时序进行重新验证。从增量修改策略的角度来看,只对那些直接受增量变化影响的布局部分进行重新布局布线也许更为有利。布局选项菜单包括“Place Incrementally”(放置增量)、“Lock Existing Placement (Fix)”[锁定现有放置 (修正)]和“Route Incrementally”(布线增量)

评论