双网传真机的编译码电路设计与实现

摘要:对双网数字传真机硬件系统中的编码和译码电路进行设计,并采用FPGA芯片进行系统实现和验证。其中的编译码电路分别采用两级编码和快速译码的思路,利用硬件描述语言设计和仿真,简化了逻辑电路的实现。验证测试表明,该电路增强了系统的稳定性和可靠性,提高了编译码效率,缩短了开发周期。

关键词:编译码电路;FPGA;码表;双网传真机

0 引言

传真通信规程是将要扫描的电平信号值进行A/D转换,再经过图像二值化处理,表示成连续交替黑白点的数据序列(I/O序列),再对该数据序列进行编码后,调制发送;接收端对收到的编码数据信号解调后进行译码,最后由热敏头打印输出。

在传真通信中,对传真图像数据进行编码和译码是传真通信的关键技术。改进的Huffman码(MHC)是ITU—T.4向各国推荐的一维标准码,主要应用于三类传真机上。MHC码是一种常用的变长码,其信源的消息与码字之间的关系是一对一的,是信息保持型的压缩方法。双网传真系统完成与Internet和PSTN网络的传真通信,采用嵌入式系统的设计思路划分软硬件。其中,传真协议采用软件实现,传真编译码和外围设备控制器采用硬件实现,以降低设计复杂度,提高传真效率。

1 传真机硬件系统模型

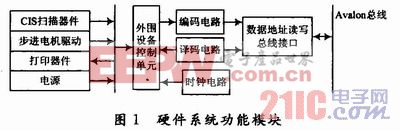

硬件电路模块应包括:CIS扫描电路模块(A/D转换)、编码电路模块(图像二值化处理)、译码电路模块、打印电路模块、步进电机驱动电路模块及时钟电路模块。并以NiosⅡ软核处理器、CIS扫描器件、步进电机、TPH打印器件为硬件平台,通过FPGA实现硬件电路模块。上层软件通过读写寄存器来控制外围设备和编译码电路,完成编码数据的读取和译码数据的写入。图1给出了硬件系统功能模块划分逻辑图。

其中,时钟电路用来产生扫描、打印及步进电机所需的时序信号;由时钟电路产生的CIS时钟周期为2.6μs,打印时钟周期为4.96μs,步进电机时钟周期为10 ms。数据地址读写总线接口与NiosⅡ处理器直接交互各种控制命令及读写数据,产生外围设备的工作使能信号,通过地址选通信号,完成各个模块与NiosⅡ处理器之间数据的交互。

2 外围设备控制单元

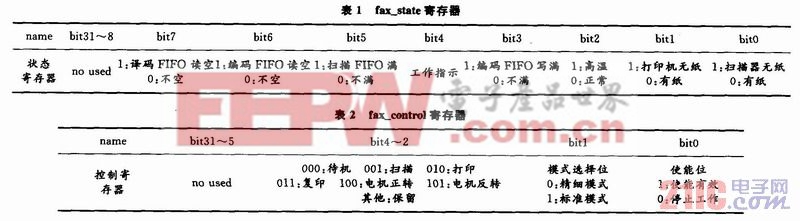

外围设备的控制主要是通过对CIS扫描器件、TPH打印器件和步进电机发出相应的控制时序信号完成扫描、打印和步进电机的驱动等功能。该部分采用硬件实现可以产生超过定时中断周期的更小周期的时序信号和时序要求精确的驱动信号,同时可以通过配置控制寄存器,对扫描和打印的功能进行选择,上层软件通过状态寄存器来判断电路的工作状态。表1和表2给出了寄存器的详细描述。

2.1 CIS扫描及A/D转换

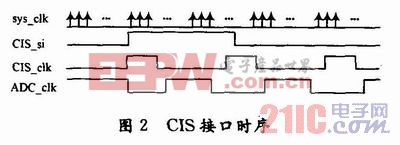

设计采用的CIS器件具有最高1.7 MHz的扫描时钟,且有效扫描宽度为216 mm(A4纸的宽度),每行有1728个扫描点。FPGA片内的数字逻辑产生驱动信号CIS_si和CIS_clk,并将模拟信号接入A/D转换器的模拟输入端口,由FPGA片内数字逻辑实时对A/D转换器的输出进行采集。图2给出了CIS接口时序。其中,CIS_si为行启动信号,每行有1728个扫描点,每隔10ms启动一次CIS_si。由于扫描最快能达到1.8ms/line,而打印最快只能达到10 ms/line,所以扫描完成后且预留出步进电机工作的时间,这样就能满足该系统的要求。CIS_clk为2.6μs的扫描时钟,占空比为0.254。ADC_clk为AD采样时钟,周期与CIS_clk相同,占空比为0.046。

A/D转换的原理是通过CIS扫描器件把原稿的光信号转化为电信号,将CIS扫描器件获得的模拟电信号通过A/D转换器件转化为8 b的数字信号在ADC_clk的下降沿送入扫描数据缓冲区。

评论