基于CPLD及DDS的正交信号源滤波器的设计

3.2 CPLD模块

该模块通过一个4引脚的工业标准JTAG接口在系统编程(ISP),并且在编程过程中仅需5.0 V单电压供电。编程过程中,I/O引脚处于三态并被上拉,以消除板上冲突。上拉阻值为1 kΩ。因为该器件是在线编程的,为了便于调试,所以把下载口直接做在电路板上。考虑到电源为自制的稳压电源,CPLD受电源纹波干扰影响较大,所以在每个器件旁都加有去耦电容。

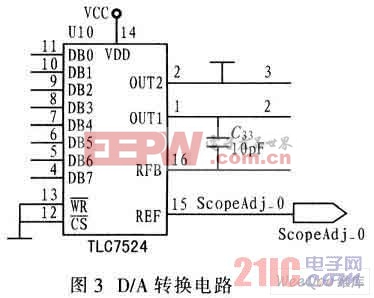

3.3 D/A转换及幅度控制

D/A转换采用TI公司的TLC7524,该器件转换速度可达10 M,幅度控制D/A转换采用MAX518,该器件是I2C总线的双D/A转换器,只需很少的端口线就可实现两路幅度的控制,大大节省单片机的端口。图3给出D/A转换电路。

3.4 后级处理模块

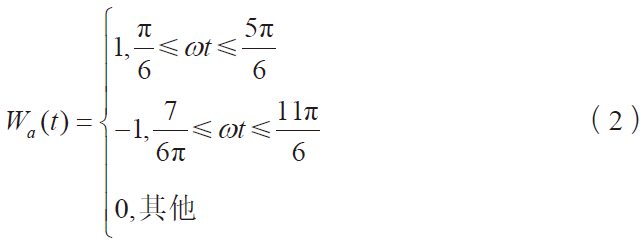

低通滤波器对阶梯正弦波进行傅里叶分析。其中若一周期采样点数为N,则其高次谐波能量主要集中在输出频率的(N±1)倍频上,其幅值为基频的 1/(N±1)。低通滤波可以平滑其台阶。另外还需滤除由DAC0832和TCL7524产生的1MHz和10 MHz的高频分量。因此根据设计的要求(输出最大频率为250 kHz,为了保证250 kHz频带内输出幅度平坦,又要尽可能抑制谐波和高频分量,综合考虑选用宽带运放LF351,用EWB仿真表明:截止频率为1 MHz~250 kHz以内幅度平坦。为了保证稳幅输出,选用AD817。该器件是一种低功耗、高速、宽带运算放大器,具有很强的大电流驱动能力。实际电路测量表明:当负载为100 Ω,输出峰-峰值为10 V时,其带宽大于500 kHz,幅度变化小于±1%。

4 软件设计

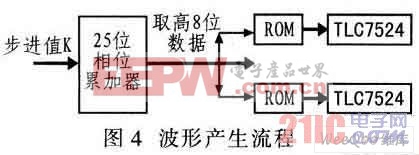

4.1 波形发生

在CPLD内设置25位相位累加器,高9位为ROM地址,低16 位为产生精确的读ROM的点与点之间的时间间隔而设置的累加寄存器,即:单片机送一频率控制字,由低16位寄存器每个时钟都累加这个值,累加到低16位溢出,然后ROM的地址加1。ROM内的每个地址的数据表示当前波形的幅度,然后连续读出数据并被平滑滤波后得出平滑、稳定的波形。波形产生流程如图4所示。

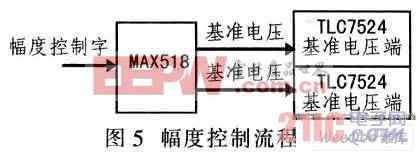

4.2 幅度控制

系统的幅度控制由MAX518完成,利用其内部电阻网络实现数字电位器功能,输出电压作为TLC7524的基准电压。图5为幅度控制流程。

评论