基于CPLD的服务机器人的视觉系统设计

随着计算机科学和自动控制技术的发展,越来越多的不同种类的智能机器人出现在工厂、生活当中,机器人视觉系统作为智能机器人系统中一个重要的子系统,也越来越受到人们的重视。它涉及了图像处理、模式识别和视觉跟踪等领域。不同种类的机器人由于工作的重点不一样,它的视觉系统在软件或硬件上都有着细微的差别。本文研究基于服务机器人的单目视觉系统。它处理的是二维图像,是基于对无遮挡物体颜色和形状的识别以及3D目标物体的平动跟踪。

本文引用地址:https://www.eepw.com.cn/article/189748.htm视觉系统是一个非常复杂的系统,它既要做到图像的准确采集还要做到对外界变化反应的实时性,同时还需要对外界运动的目标实时跟踪。因此,视觉系统对硬件和软件系统都提出了较高的要求。目前比较流行的足球机器人技术,它的视觉系统属于比较典型的快速识别和反应类型。一般情况下,它是通过彩色标志定标的方法来达到对队员和目标的识别,以及通过扩展卡尔曼滤波器的预测功能来实现对目标的跟踪功能。在硬件上,采用一个现成的摄像机来实现一个机器人的图像采集系统。

本系统在设计上采用CMOS图像传感器代替CCD类型传感器进行采集图像,DSP处理芯片TMS320VC5509A进行图像处理以及作为CPU控制,在设计过程中,为了直观显现机器人视觉系统识别和跟踪的效果,专门采用了一个TFT格式的液晶来直观显示。软件上,采用了一部分足球机器人的视觉技术来达到对目标的快速识别,通过全局的特征矩构建的雅可比矩阵达到对目标的自适应跟踪。

1 硬件部分设计

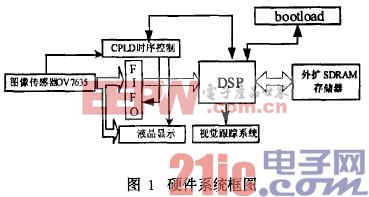

图1为系统硬件电路的功能模块框图。

1.1 图像采集

视觉镜头把外部的图像信息成像在图像传感器的面阵单元上。目前流行的图像传感器有面阵CCD(Charged Coupled Device,电荷耦合器件)型和面阵CMOS两种。相比较CCD型的图像传感器,CMOS图像传感器的有源像素单元为每一个像素提供了放大器,只需一个单供电低逻辑电平电压,功耗只相当于CCD的十分之一。CMOS图像传感器内部集成了A/D转换部分,直接输出数字信号。基于这些因素,本系统采用了Omnivision公司推出的CMOS彩色图像传感器OV7635。

OV7635的分辨力为640X480,能输出3种格式的8位数据:YCbCr4:2:2模式、RGB4:2:2模式和RGB原始数据模式。输出VGA格式最大可达到30fps(fps:每秒帧数)。能工作在逐行扫描下和隔行扫描下。OV7635有主模式和从模式两种工作模式。在主模式下,同步信号和时钟不由外围设备控制。在从模式下,OV7635的场同步信号VSYNC,行同步信号HREF以及系统的晶振频率XCLK均由外部设备控制。本系统采用的是主模式。OV7635通过I2C总线配置片内寄存器,使其输出原始数据。系统上电复位后,由DSP芯片的I2C总线信号对CMOS寄存器初始化。然后OV7635就按要求输出图像信号。包括行同步信号HREF,场同步信号VSYNC,像素时钟信号PCLK,数字图像信号。

1.2 液晶显示

为了很直观的看到视觉系统对人的识别和跟踪效果,采用了一片INNOLUX公司的PT035TN01液晶显示屏。为了不增加对DSP的负担,同时也为了实时看到对外界目标物体的跟踪效果,液晶显示的数据不经由DSP,直接通过传感器OV7635输出的图像数据信号和CPLD控制时序来进行显示。PT035TN01是3.5英寸TFT格式的液晶,分辨力为320×3(RGB)×240,液晶IF1、IF2两输入控制脚对输入的数据格式进行选择:串行RGB格式、CCIR601格式、CCIR656格式。液晶的扫描模式有4种。本视觉系统采用的输入数据格式是CCIR601格式,扫描模式为由上到下和左到右的扫描模式。

在CCIR601格式下,图像传感器输出的像素时钟PCLK通过CPLD二分频作为液晶的工作时钟,图像传感器输出的行同步信号HREF经过CPLD的处理后作为液晶的行同步信号HIS,这样,在CPLD控制下,图像传感器OV7635输出的数据信号送入液晶中进行显示。

1.3 时序控制

OV7635输出的场同步信号VSYNC,行同步信号HREF以及像素时钟信号PCLK接至CPLD芯片,产生控制信号把OV7635输出的数据信号存入FIFO帧存储器AL422B中,以及产生液晶的时钟和行同步信号控制液晶的显示。CPLD采用了ALTERA公司的EPM7064芯片。在CPLD中完成了对FIFO的写控制、通知DSP读信号、液晶的时钟信号的产生等功能。

CPLD接收场同步信号VSYNC,此信号的下降沿表示图像传感器输出一帧的开始,此时CPLD产生WRST负脉冲复位FIFO的写指针。场同步信号VSYNC下降沿后,判断行同步信号HREF的上升沿到来,接着利用像素时钟信号PCLK作为写时钟WCK将图像数据直接存储到FIFO中,当存到一定的数后,就及时发信号给DSP,以便DSP读取数据,本系统采用的是一个中断INT0来通知DSP。此时DSP可以读数据也可以不读,视处理的速度来定。读数据时,可利用RD和片选,产生RCK信号。DSP读取的速度不能太快,以读取速度小于写速度为原则。

在对液晶的逻辑时序控制上,由于图像输出的信号是640×480的像素,而液晶的显示为320×240的格式。所以利用CPLD把图像传感器输入的像素时钟信号PCLK进行二分频产生液晶的时钟信号控制液晶的显示,同时对行同步信号进行隔行有效从而达到液晶对图像的显示。CPLD中的程序编写用的采用了硬件描述语言VHDL,在QUARTUSⅡ软件平台上进行编写的。由于在选用芯片时采用的是EPM7064S系列的44脚PLCC封装的,只能工作在5V电压情况下,其输出的高电平信号是5V,必须通过处理才能接入系统中工作在3。3V状态下的芯片器件。

评论