PCB电源供电系统分析与设计

当今,在没有透彻掌握芯片、封装结构及PCB的电源供电系统特性时,高速电子系统的设计是很难成功的。事实上,为了满足更低的供电电压、更快的信号翻转速度、更高的集成度和许多越来越具有挑战性的要求,很多走在电子设计前沿的公司在产品设计过程中为了确保电源和信号的完整性,对电源供电系统的分析投入了大量的资金,人力和物力。

本文引用地址:https://www.eepw.com.cn/article/189743.htm电源供电系统(PDS)的分析与设计在高速电路设计领域,特别是在计算机、半导体、通信、网络和消费电子产业中正变得越来越重要。随着超大规模集成电路技术不可避免的进一步等比缩小,集成电路的供电电压将会持续降低。随着越来越多的生产厂家从130nm技术转向90nm技术,可以预见供电电压会降到1.2V,甚至更低,而同时电流也会显著地增加。从直流IR压降到交流动态电压波动控制来看,由于允许的噪声范围越来越小,这种发展趋势给电源供电系统的设计带来了巨大的挑战。

PCB电源供电系统设计概览

通常在交流分析中,电源地之间的输入阻抗是用来衡量电源供电系统特性的一个重要的观测量。对这个观测量的确定在直流分析中则演变成为IR压降的计算。无论在直流或交流的分析中,影响电源供电系统特性的因素有:PCB的分层、电源板层平面的形状、元器件的布局、过孔和管脚的分布等等。

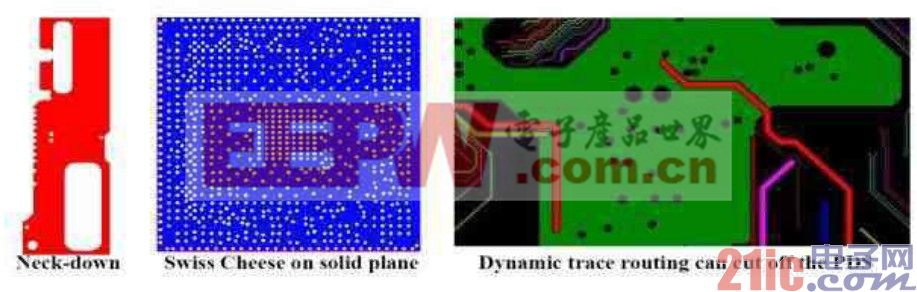

图1:PCB上一些常见的会增加电流路径阻性的物理结构设计。

电源地之间的输入阻抗概念就可以应用在对上述因素的仿真和分析中。比如,电源地输入阻抗的一个非常广泛的应用是用来评估板上去耦电容的放置问题。随着一定数量的去耦电容被放置在板上,电路板本身特有的谐振可以被抑制掉,从而减少噪声的产生,还可以降低电路板边缘辐射以缓解电磁兼容问题。为了提高电源供电系统的可靠性和降级系统的制造成本,系统设计工程师必须经常考虑如何经济有效地选择去耦电容的系统布局。

高速电路系统中的电源供电系统通常可以分成芯片、集成电路封装结构和PCB三个物理子系统。芯片上的电源栅格由交替放置的几层金属层构成,每层金属由X或Y方向的金属细条构成电源或地栅格,过孔则将不同层的金属细条连接起来。

对于一些高性能的芯片,无论内核或是IO的电源供电都集成了很多去耦单元。集成电路封装结构,如同一个缩小了的PCB,有几层形状复杂的电源或地平板。在封装结构的上表面,通常留有去耦电容的安装位置。PCB则通常含有连续的面积较大的电源和地平板,以及一些大大小小的分立去耦电容元件,及电源整流模块(VRM)。邦定线、C4凸点、焊球则把芯片、封装和PCB连接在了一起。

整个电源供电系统要保证给各个集成电路器件提供在正常范围内稳定的电压。然而,开关电流和那些电源供电系统中寄生的高频效应总是会引入电压噪声。其电压变化可以由下式计算得到:

这里ΔV是在器件处观测到的电压波动,ΔI是开关电流。Z是在器件处观测到的整个电源供电系统电源与地之间的输入阻抗。为了减小电压波动,电源与地之间要保持低阻。在直流情况下,由于Z变成了纯电阻,低阻就对应了低的电源供电IR压降。在交流情况下,低阻能使开关电流产生的瞬态噪声也变小。当然,这就需要Z在很宽的频带上都要保持很小。

图2:Sigrity PowerDC计算得到电源板层上的电流分布。

注意到电源和地通常用来作为信号回路和参考平面,因此电源供电系统与信号分布系统之间有着很紧密的关系。然而,由于篇幅的限制,同步开关噪声(IO SSO)引入的电源供电系统的噪声现象和电流回路控制问题将不在这里讨论。以下几节将忽略信号系统,而单纯注重电源供电系统的分析。

评论