一种大电压输出摆幅低电流失配电荷泵的设计

摘要:在分析了基本锁相环电荷泵工作机制的基础上,提出一种新型的电荷泵结构,该电荷泵在非常宽的电压范围内具有很低的电流失配,解决了传统电荷泵结构所具有的电荷注入、时钟馈通和电荷共享等问题,并且非常容易实现电荷泵充放电电流的数字控制。基于SMI(:O.18 gm cMOSRF工艺库设计的实际电路,使用Cadence工具仿真结果表明,在电源电压2.O V时,输出电压为O.3~1.63 V,充放电电流最大失配率小于0.1%,电流绝对值偏移率小于O.6%,说明这种新型电荷泵结构具有良好的性能。

关键词:锁相环;电荷泵;电流失配;数字控制

0 引 言

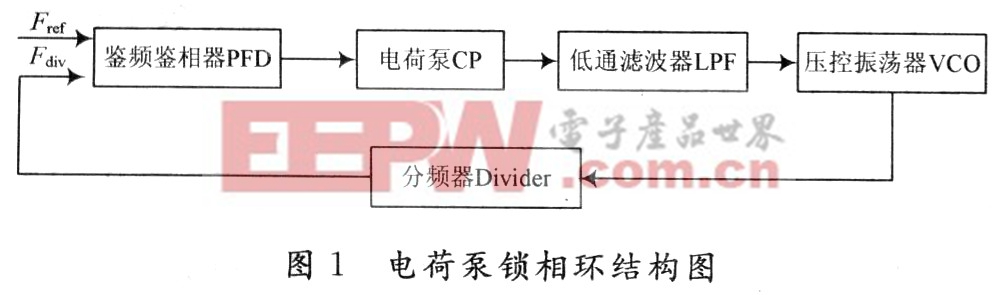

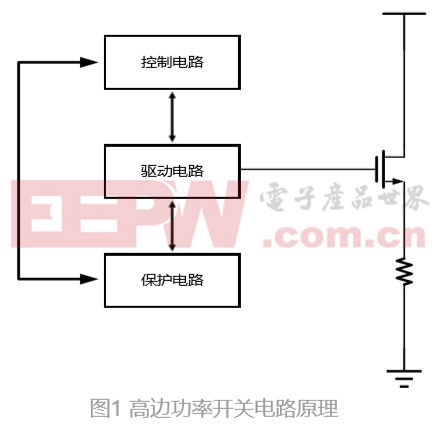

CMOS电荷泵锁相环以其高速、低抖动、低功耗和易集成等特点,已广泛用于接收机芯片、时钟恢复电路中,如图l所示,电荷泵对整个电荷泵锁相环性能具有关键的作用,如果电荷泵的充放电电流能够在很大的输出电压范围内具有高精度的匹配,在PLL锁定某个频率时,LPF提供给VCO的控制电压将是一个常数,它将显著降低VCO输出频率的抖动,提高VCO的相位噪声特性,并且VCO可以具有很大的调谐范围。

l 传统电荷泵工作机制

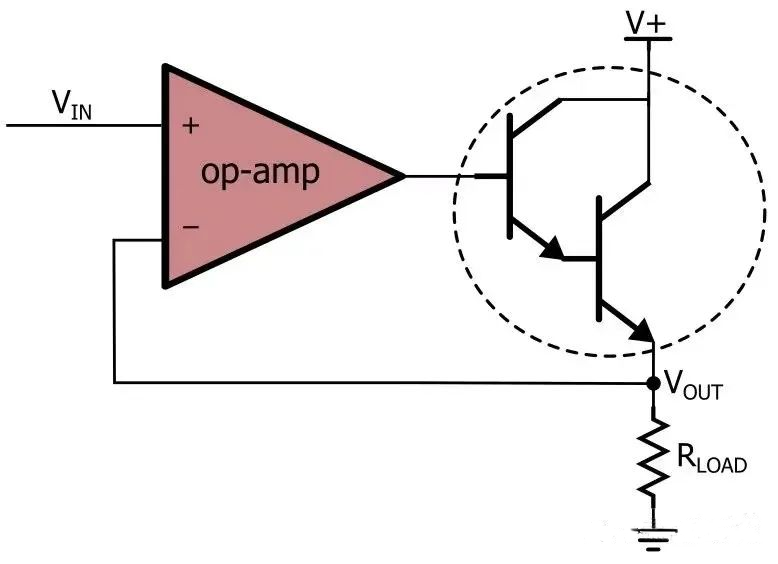

传统电荷泵结构如图2所示。

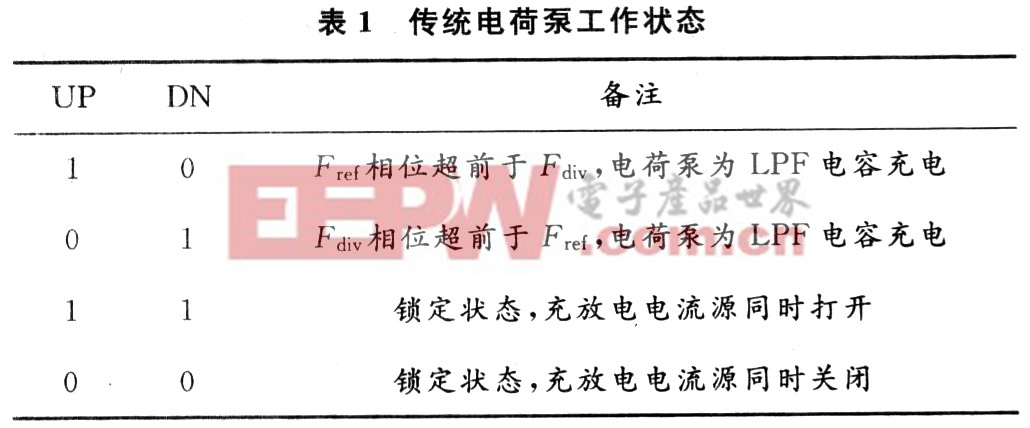

它主要由两个受控开关的电流源组成,通过PFD比较Fref和Fdiv的相位,如果Fref相位超前于Fdiv,则输出UP为高电平,DN为低电平,Iup给LPF电容充电,使得VC0的控制电压上升,控制VCO的输出信号频率升高;如果Fdiv相位超前于Fref,则输出uP为低电平,DN为高电平,LPF电容通过Idown。放电,使得VCO的控制电压下降,控制VCO的输出信号频率降低;如果Fref和Fdiv的相位相同,PLL达到锁定状态,则UP和DN信号控制充放电电流源同时打开或关闭,具体工作状态如表1所示。

在电路锁定状态,为了消除PFD的死区,电荷泵的充放电电流源在每个周期需要同时打开一段时间,如果这两个电流源的电流大小不精确匹配,假设Iup大于Idown,则将有Iup。减去Idown大小的电流为LPF电容充电,使得VCO的控制电压升高,继而使得VCO的输出频率发生变化,降低了输出时钟的噪声性能。而在电荷泵的充放电电流同时关闭时,由于MOS管开关的源极和漏极寄生电容以及沟道反型层中存储了电荷,导致电荷注入到IPF的电容上,从而引起VCO输出频率的变化,克服电荷共享最有效的方法是在充放电开关断开时用单位增益运放将输出电压复制到电流源漏端。由电荷泵的非理想特性导致的开关时间延时、充放电电流失配和电荷注入引起的PLL输出信号的相位偏差为:

评论