一种基于DDS和PLL技术本振源的设计与实现

频率合成技术作为现在电子系统中的一种关键技术,已广泛应用于通信、雷达、电子对抗、定位导航、广播电视、遥测遥控、仪器仪表等许多领域并得到了快速的发展,它是用一个或多个高稳定、高精确度的标准频率源作为参考,通过对频率进行加、减、乘、除等一系列变换,从而产生同样高稳定度和精确度的大量离散频率的技术。频率合成器的实现方式有4种:直接模拟频率合成器(DAS)、锁相环频率合成器(PLL)、直接数字频率合成器(DDS)和混合结构(PLL+DDS)。其中,第1种已很少使用,第2~4种都有广泛的使用。应根据频率合成器的使用场合、指标要求确定具体使用哪种方案。

随着电子技术的不断发展,各类电子系统对频率合成器的要求越来越高,对相位噪声、频率转换时间、频率分辨率、相对工作带宽、体积及功耗等多种指标也提出了更高的要求。在某项课题研究中,根据接收机的结构,接收机需要频综部分提供一个1 514 MHz(77 200 MHz/51△1 514 MHz)的下变频本振信号,为实现载波同步,需要快速地调整下变频本振信号的频率、相位,其频率调整范围不大,在10 MHz以内。如果单独选用锁相环频率合成器(PLL),则可实现结构简单、体积小、易于集成、调试方便、杂散低等优点,但是频率转换时间相对较长,而直接数字频率合成器(DDS)是一个全数字化的系统,具有易于集成、极快的跳频速度、极高的频率分辨率和频率切换时相位连续等优点,缺点就是杂散比较大、输出频率低。所以根据这两种频率合成器的特点,本文采用DDS和PLL相结合,利用DDS作为参考信号源,以DDS激励PLL的频率合成方案。

1 系统原理

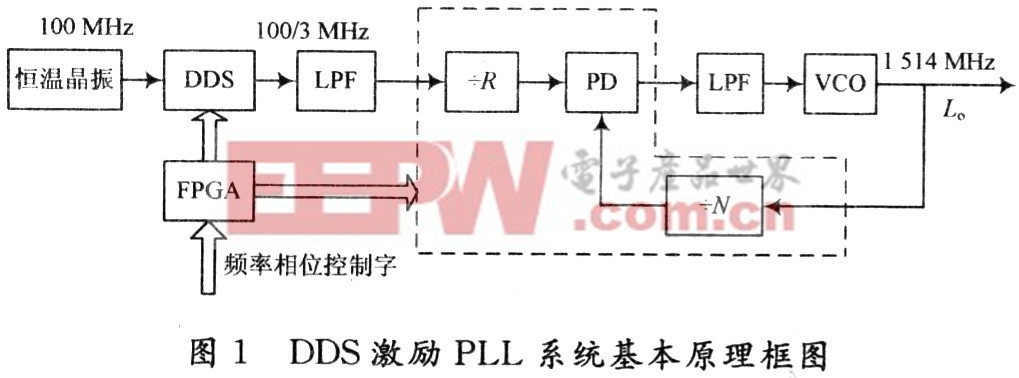

以DDS激励PLL的基本原理组成框图如图1所示,采用高稳定的石英晶体振荡器作为DDS的参考时钟源;通过FPGA把频率控制字和相位控制字写入DDS内部的寄存器中,DDS便可以产生一个频率和相位都可编程控制的模拟正弦波输出;然后把DDS的输出信号作为PLL的参考信号;最后根据期望输出的信号频率,设定分频器的分频比N,便得到了频率为DDS输出频率N/R倍的时钟信号。

这种结构利用DDS的高分辨率保证了足够小的频率步进,同时PLL的带通特性很好地抑制了DDS输出频谱中的部分杂散。该方案实现了DDS和PLL的优势互补,兼顾了各个方面的性能,所以此方案实现的本振源做到了比较高的频率、较快的频率转换速度和较高的频率分辨率,同时也很好地保证了系统杂散和相位噪声性能。

2 电路设计

本设计系统的整个电路主要包括两大部分,即DDS部分和PLL部分。

2.1 DDS部分

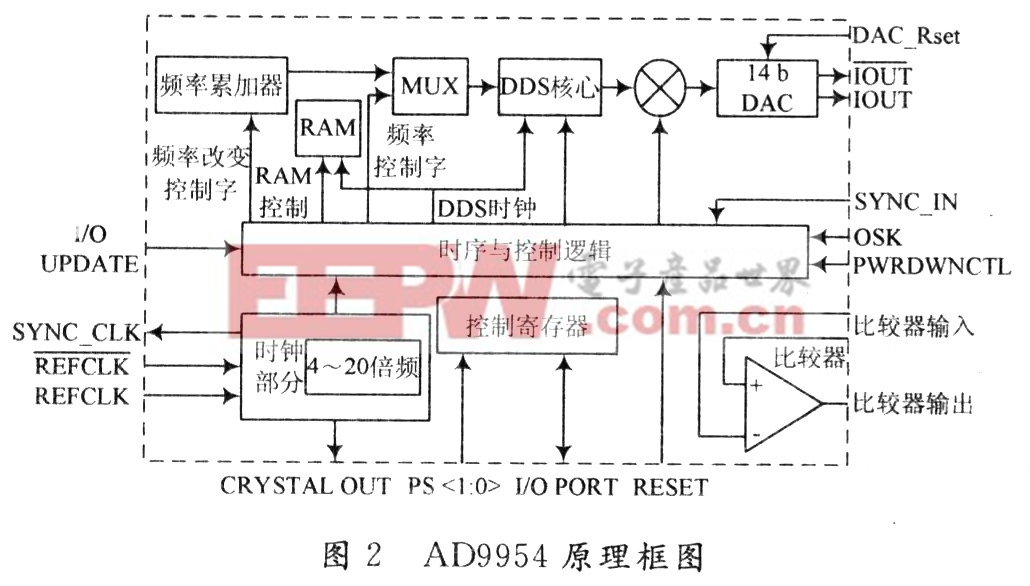

DDS部分的时钟输入选用100 MHz的恒温晶体振荡器;DDS部分的核心采用美国AD公司生产的大规模集成芯片AD9954,它是用先进的DDS技术开发的高集成度DDS器件,内置高速、高性能D/A转换器及超高速比较器,可作为数字编程控制的频率合成器,能产生0~160 MHz的正弦波信号。AD9954内含1 024×32 b静态RAM,利用该RAM可实现高速调制,并支持几种扫描模式。AD9954可提供自定义的线性扫描操作模式,通过AD9954的串行I/O口输入控制字可实现快速变频且具有良好的频率分辨率。其应用范围包括灵敏频率合成器、可编程时钟发生器、雷达和扫描系统的FM调制源以及测试和测量装置等,其内部结构如图2所示。

DDS电路设计应遵循的主要原则是使其输出信号具有较好的控制时序、较低的相位噪声和窄带杂散,其次是正确的电路铺设和连接,DDS的外围电路并不复杂,主要由低压差稳压电源NCP1117和低通滤波器SCLF-30等组成。AD9954频率控制字为32位,在本应用中系统工作时钟为100 MHz,输出时钟的频率分辨率△f1=100 MHz/232=0.023 Hz。AD9954相位控制字为14位,输出时钟的相位分辨率△φ1=360°/214=0.022。

2.2 PLL部分

PLL部分主要包括预分频器、分频器、鉴相器、环路滤波器和’VCO。根据设计需要采用锁相环频率合成器集成芯片ADF4112,它集成了预分频器、分频器、鉴相器等各种重要部件,如图3所示。它由一个低噪声数字鉴相器、一个高精度电荷泵、一个可编程参考分频器(R分频器)、一个可编程A,B计数器以及一个双模分频器P/P+1组成。6位A计数器、13位B计数器与双模分频器P/P+1共同组成了N分频器,分频比N=BP+A。数字鉴相器用来对R计数器和N计数器的输出相位进行比较,然后输出一个与二者相位误差成比例的误差电压。鉴相器内部还有一个可编程延迟单元,用来控制翻转脉冲的宽度,这个翻转脉冲保证鉴相器的传递函数没有死区,因此降低了相位噪声和参考杂散。该芯片的主要性能特点如下:

工作电压:2.7~5.5 V,同时还提供外部可调的电荷泵电压调节功能;最高鉴相频率为55 MHz,最高RF输入频率达3 GHz;具有四组可编程双模分频器8/9,16/19,32/33,64/65;内置可编程电荷泵电流和可编程反冲脉宽功能;编程控制采用3线串行接口;能够进行模拟和数字锁定检测;软、硬件断电模式;具有良好的相位噪声参数。

评论