转换器时钟技术向高速数据时钟发展

无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖动、精确的频率转换和去抖动能力。高性能转换器时钟解决方案所体现的许多属性可被有线网络所用的时钟解决方案延用。整个有线网络对互操作性和可靠同步的需求也衍生出某些独特的时钟系统需求。希望这篇文章有助于对这两个应用领域的时钟技术需求进行对比和分析。

本文引用地址:https://www.eepw.com.cn/article/188853.htm转换器时钟

基站收发器、宽带调制解调器和高端仪器仪表通常需要具有高动态范围和高采样率的ADC和/或DAC。高动态范围是为了将信号解析到所需的精度。高采样率则是处理高带宽信号所必需的。无论是无线电系统、调制解调器或者是测量仪器,对转换器的要求将取决于整个系统的规格参数和架构。该转换器的采样时钟的频谱纯度往往会对实际达到的性能产生重大影响。

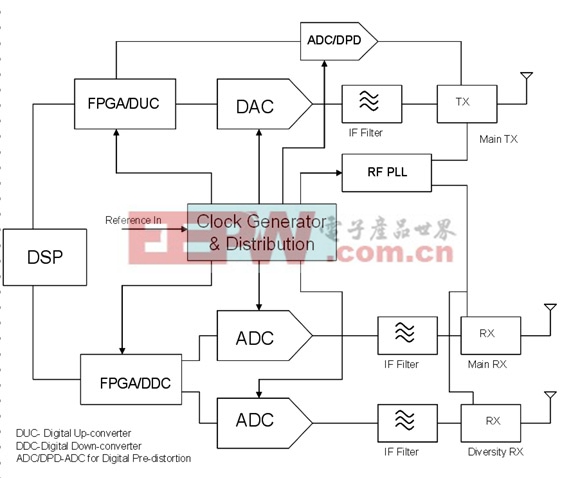

一个无线收发器电路的例子如图1所示。除了为ADC和DAC提供时钟,时钟发生器还负责将时钟信号分配到收发器卡上的其他几个电路模块。接下来我们将集中讨论时钟抖动和相位噪声对ADC性能的影响。

图1:收发器系统框图。

无线电接收器中ADC的一个关键指标是信噪比(SNR),它将影响到ADC在给定幅度范围内能够达到的信号采样精度。理想情况下,ADC应该能够以很高的分辨率将非常小的模拟输入信号转换成精确的数字信号。按照无线电术语,ADC的SNR将决定最小可检测信号(MDS)。

N位转换器基于量化噪声的理论SNR等于:

SNR = 6.02(N) + 1.8 db

因此,对于一个14位转换器,其可以实现的最佳SNR大约为86db。

在IF采样架构中,如图1所示框图,对时钟抖动的要求可以说非常严格。事实上,提供给ADC的时钟的质量常常是系统SNR性能的一个限制因素。这可以通过以下公式来理解。

评论