一种自动变模控制的宽频带全数字锁相环

在此提出了一种具有自动变模控制的宽频带的全数字锁相环。在传统的自动变模控制的全数字锁相环的基础上,增加了独特的鉴频锁存模块,能够随时跟踪输入信号频率的变化,在先锁定输入信号频率的基础上快速实现相位的锁定。整个系统采用VHDL语言设计实现,使用QuartusⅡ软件对系统进行仿真验证,给出了计算机的仿真结果。

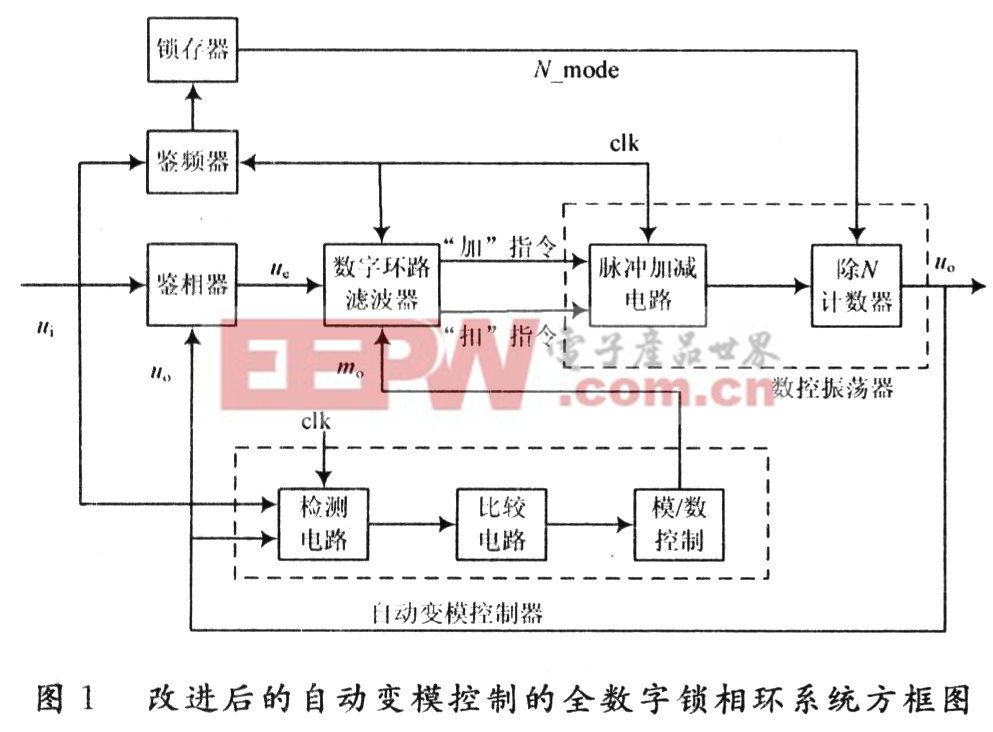

1 改进后的自动变模控制的全数字锁相环的结构和工作原理

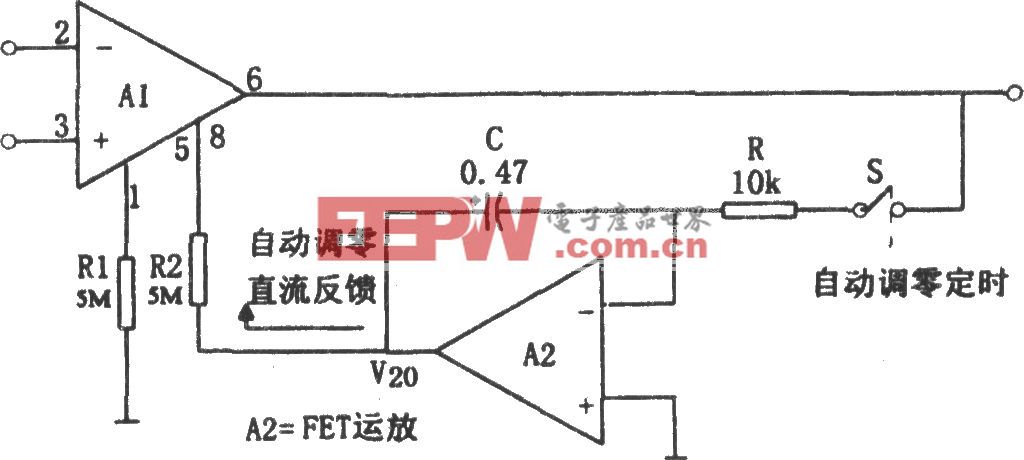

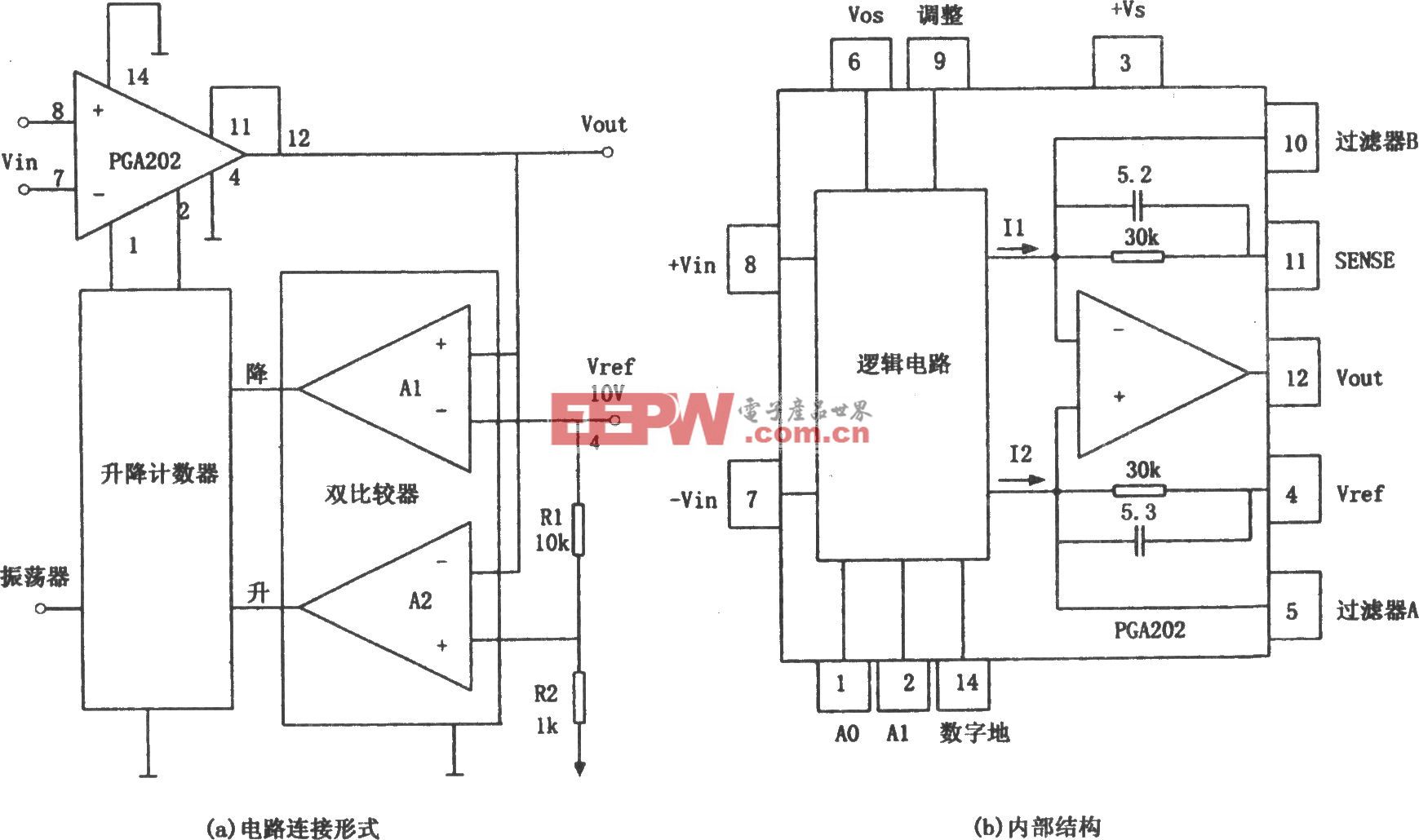

如图1所示为改进后的自动变模控制的全数字锁相环的系统方框图。图中的鉴相器采用边沿触发鉴相器,相对于异或门鉴相器具有更大的鉴相范围,边沿触发型鉴相器的线性鉴相范围为±π。该设计中的数字环路滤波器为可变模的K可逆计数器,鉴相器的输出ue作为K可逆计数器的计数方向控制信号,K计数器的计数值增加到K时,就输出“加”指令;反之,K计数器的计数值减到0时,就输出“减”指令。在系统工作过程中,自动变模控制器通过检测电路对输入信号ui和输出信号uo的相位差进行计数,然后经过比较电路和模数控制电路选择合适的模值mo,不断地更新K计数器的K值。脉冲加减电路作为数控振荡器的一部分,是整个系统中最重要的模块。脉冲加减电路的功能是在接收到“加”、“扣”指令时,能够准确地在本地高速时钟clk中插入和扣除一个脉冲,把调整后的脉冲序列作为除N计数器的时钟源,对输出信号uo的相位进行调整。该设计的最大特点就是除N计数器模块的N值可以根据输入信号的变化不断更新,使输出信号uo快速跟踪输入信号ui的频率,同时达到对系统中心频率的不断更新,实现宽频带快速锁相的目的。N值的检测是由鉴频和锁存模块实现的,当输入信号ui为上升沿时,内部计数器开始计数,直到ui变为低电平时,计数器停止计数。同时在ui为低电平时把计数结果送入锁存器中作为除N计数器的分频值。上述即为改进后的自动变模控制的全数字锁相环的工作原理。

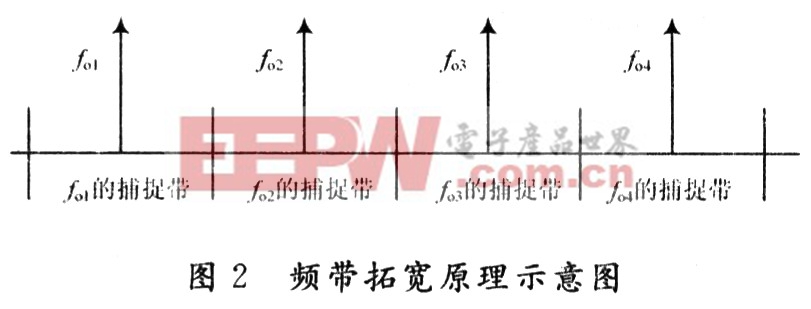

从以上的分析可知,该设计的全数字锁相环具有两个显著优点:第一,由于采用自动变模控制的数字环路滤波器,很好地解决了环路的捕捉时间和抗噪声性能之间的矛盾。模值K的大小对整个系统的性能具有很大影响,K值越大,系统响应越慢,捕捉时间越长;相反,K值越小,系统响应越快,捕捉时间越短。但是在系统由捕捉进入同步过程后,如果K值太小,会因可逆计数器的频繁循环计数而产生持续的进位或借位脉冲,导致输出信号相位抖动,增加了同步误差。采用自动变模控制后,系统可以根据输入/输出信号相位误差的大小,对模值K进行选择更新。在环路捕捉过程中,选择较小的模值,可增加环路带宽,加快锁定速度;在同步过程中,选择较大的模值,可缩小环路带宽,有利于抑制相位抖动,减小同步误差,从而可以实现快速高精度的锁相。第二,在传统全数字锁相环结构的基础上增加了独特的鉴频锁存模块,不仅可以捕捉和锁定未知的输入信号,还可以使系统具有较宽的频带宽度,实现对频率发生变化的输入信号的快速锁定。该设计的频带拓宽原理可以描述为:在鉴频锁存模块,输入信号频率的计算是以外部高速时钟作为时钟源的,外部时钟频率越高得到的N值越精确。能够精确计算出的频率值就相当于不同系统中心频率,而在每个中心频率附近锁相环系统都有一个捕捉带。因此,选择合适的外部高速时钟,不同的中心频率所得到的不同捕捉带,就可以构成整个环路的捕捉带。所以,该设计与传统的数字锁相环系统相比具有较宽的频带。如图2所示为频带拓宽原理示意图。

评论